SPI廣泛用于將微控制器連接到嵌入式系統中的外設和存儲設備。特別是,它經常用于存儲可執行代碼的串行NOR閃存。

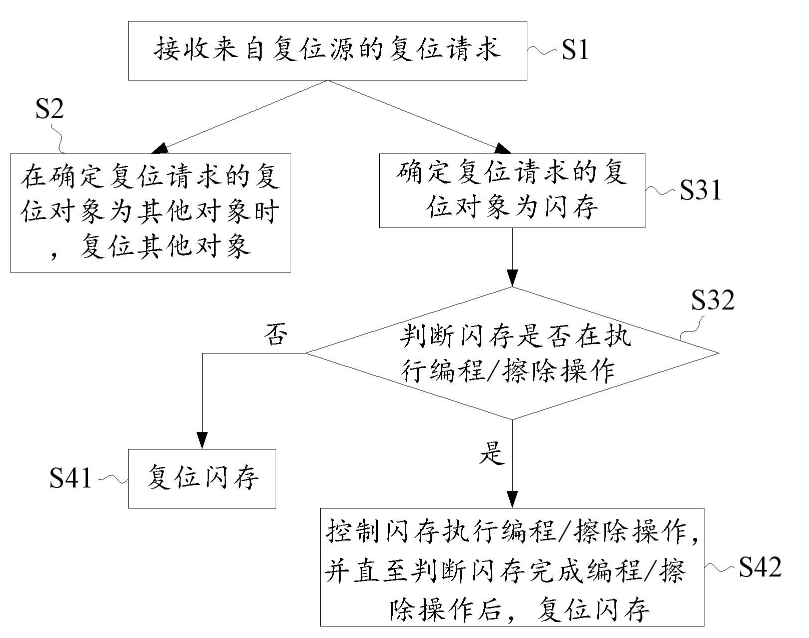

設計穩定性在嵌入式設計中至關重要,復位的使用是從運行時錯誤中恢復的強大工具。然而,由于存儲器制造商開發的更小的封裝無法支持專用硬件復位引腳,因此復位引腳面臨壓力。值得慶幸的是,對于支持新JEDEC JESD252標準的串行閃存器件來說,現在這個問題已經不那么嚴重了,該標準定義了一種不需要專用復位引腳的復位機制。

電子系統中瞬態錯誤有許多潛在原因,包括信號完整性問題和背景輻射,這些原因可能會損壞存儲器,從而導致數據和編程錯誤。這些是可能導致常見問題的失敗:“您是否嘗試過將其關閉并再次打開?這可能只會給消費類設備帶來不便,但成為嵌入式系統和物聯網節點的主要問題。

這些系統需要以最小的停機時間連續運行。通常,它們無法訪問,因此它們需要能夠在沒有人為干預的情況下從故障中恢復。這樣的系統通常已經使用自檢機制,如看門狗定時器,以檢測故障并采取糾正措施,但這并不總是足夠的。

設計工程師將確保所有器件在上電時都設置為已知狀態。但是,軟復位也可以是錯誤恢復策略的一部分,因此整個系統能夠復位組件和子系統非常重要。

重置串行閃存

串行外設接口(SPI)廣泛用于將微控制器連接到嵌入式系統中的外設和存儲設備。特別是,它經常用于存儲可執行代碼的串行NOR閃存。

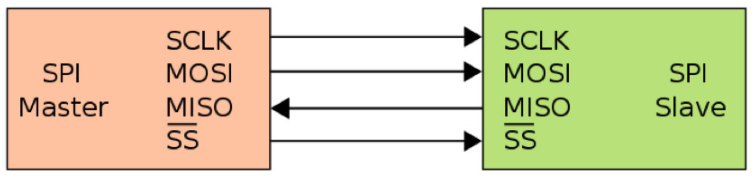

圖 1: SPI 接口

最初的SPI規范在每個方向上只有一根數據線。這太慢了,無法直接從串行存儲器支持高性能代碼執行。這意味著代碼必須先復制到SRAM才能運行,從而增加了啟動時間并增加了系統成本。

為了提高原始SPI規格的帶寬,可以使用四個或八個數據信號,從而允許在每個時鐘周期傳輸更多的數據位。這些擴展的 SPI (xSPI) 接口由 JEDEC 在 JESD251 中定義。

現代八進制 xSPI 存儲器(如 Adesto EcoXiP 系列)可提供直接從串行存儲器執行代碼所需的性能,這種技術稱為就地執行 (XiP)。這提供了高性能并支持即時啟動,同時將功耗降至最低。它還減少了所需的SRAM量,從而降低了系統成本。

在系統故障的情況下,串行存儲器可能需要在恢復過程中重置。然而,制造商面臨壓力,要求生產更小、成本更低的封裝,引腳數減少,這意味著許多串行存儲器沒有復位引腳,或者,如果它們有復位引腳,它可能會與另一個功能多路復用,使其難以使用。標準 JESD252 中定義的新型 JEDEC 串行閃存復位協議無需專用復位引腳即可控制復位功能。

JESD252不使用復位引腳,而是使用SPI信號(時鐘、芯片選擇和串行數據)來傳輸迫使目標器件自行復位的序列。在復位序列期間,時鐘信號保持低電平,以區分復位事務與正常SPI命令,并防止發送任何SPI命令,使用芯片選擇信號作為目標器件的時鐘。指定的轉換序列在數據引腳上傳輸,以防止噪聲引起的錯誤復位。

Adesto 出貨了第一款支持 JESD252 的串行 NOR 閃存,其 EcoXiP 也提供,該接口具有八通道 SPI 接口,可提供比四通道接口更高的性能。通過執行順序指令提取進一步優化了執行性能,而無需為每次讀取發送地址。EcoXiP 還具有降低功耗和提供更高安全性的功能。

構建更好的設計

使用 XiP,您將能夠以更低的功耗和成本提供所需的性能。雖然XiP需要在微控制器上具有兼容的存儲器接口,但越來越多的制造商正在增加對此的支持。通過指定支持JESD252串行復位協議的串行閃存器件,您將能夠開發更可靠、更穩定的產品,從而提高客戶滿意度。

審核編輯:郭婷

-

微控制器

+關注

關注

48文章

7572瀏覽量

151635 -

物聯網

+關注

關注

2910文章

44777瀏覽量

374650 -

閃存器

+關注

關注

0文章

7瀏覽量

1992

發布評論請先 登錄

相關推薦

電腦變成云存儲設備,電腦變成云存儲設備的教程,個人云電腦是什么以及怎么連接

TMS320C672x DSP串行外設接口(SPI)參考指南

KeyStone架構串行外設接口(SPI)手冊

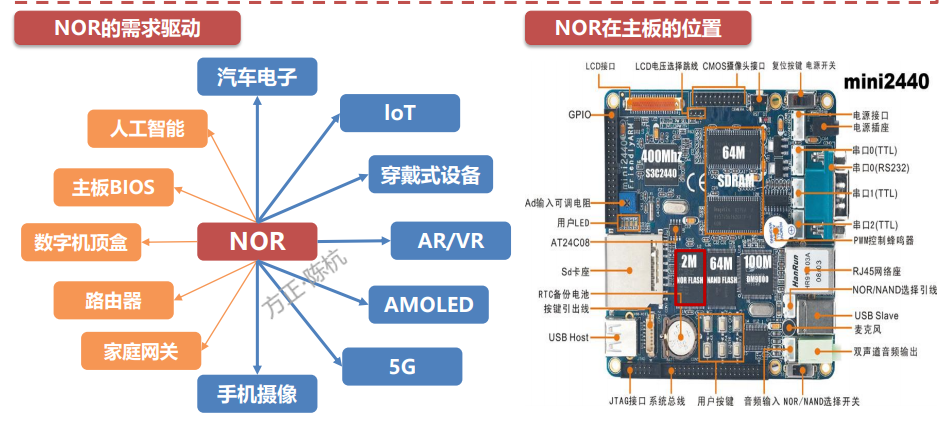

物聯網行業存儲方案詳解_SPI NOR Flash

航天級100krad隔離式串行外設接口(SPI)LVDS電路

航天級100krad隔離式串行外設接口(SPI)RS-422電路

SPI總線的定義和特點

設備遠程維護平臺是什么

探索SPI單線傳輸模式中時鐘線與數據傳輸的簡化

具有雙/四SPI和QPI的串行閃存W25Q128FV數據手冊

復位電路的電阻電容分別有什么作用?

一文詳解SPI串行外設接口

如何遠程復位串行SPI存儲設備

如何遠程復位串行SPI存儲設備

評論