注意示波器的探頭和示波器本身的帶寬能夠滿足測試要求。

測試點的選擇要注意選到盡量靠近信號的接受端。由于 DDR 信令比較復雜,因此為了能快速測試、調試和解決信號上的問題,我們希望能簡單地分離讀/寫比特。

此時,最常用的是通過眼圖分析來幫助檢查 DDR 信號是否滿足電壓、定時和抖動方面的要求。觸發模式的設置有幾種,首先可以利用前導寬度觸發器分離讀/寫信號。

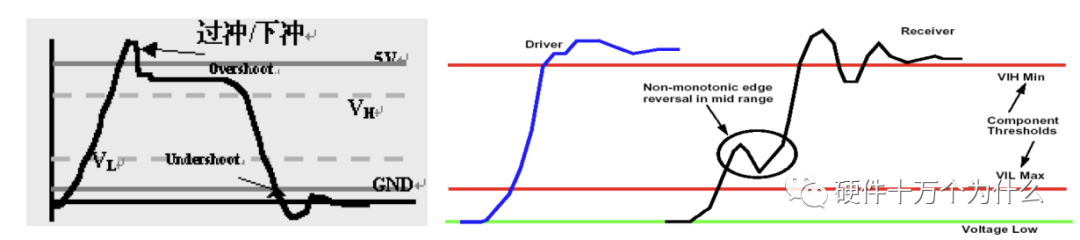

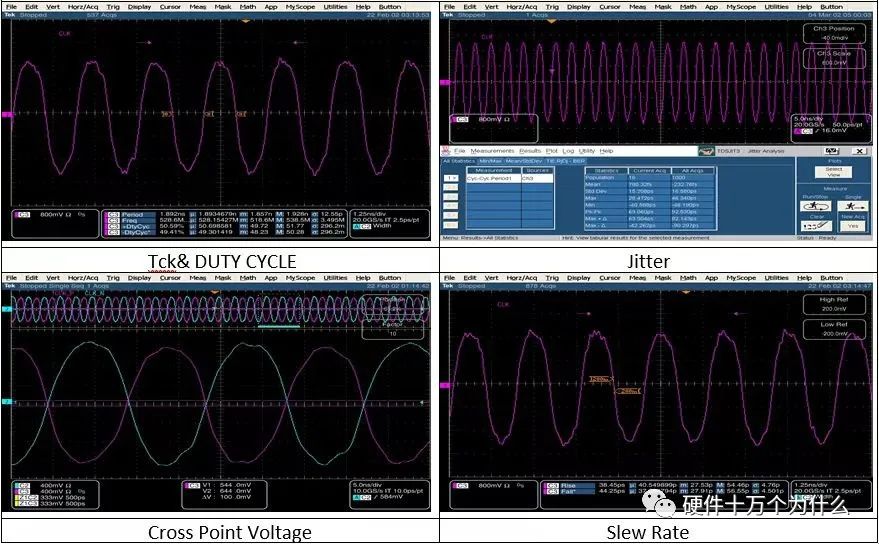

根據 JEDEC 規范,讀前導的寬度為 0.9 到 1.1 個時鐘周期,而寫前導的寬度規定為大于 0.35 個時鐘周期,沒有上限。第二種觸發方式是利用更大的信號幅度觸發方法分離讀/寫信號。通常,讀/寫信號的信號幅度是不同的,因此我們可以通過在更大的信號幅度上觸發示波器來實現兩者的分離。測試中要注意信號的幅度,時鐘的頻率,差分時鐘的交叉點,上升沿是否單調,過沖等。

2、DDR3中的幾種采樣關系

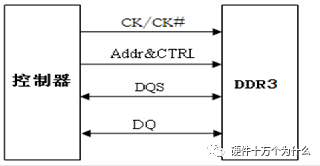

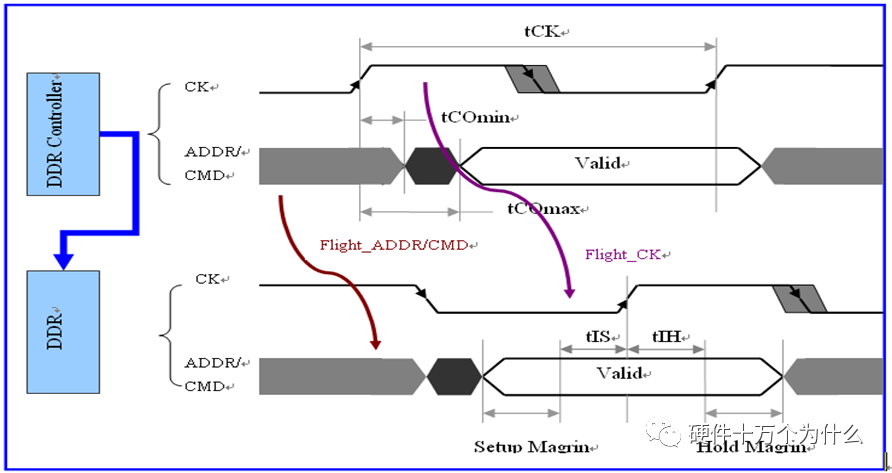

地址控制信號ADDR/CMD與系統時鐘CK的時序關系

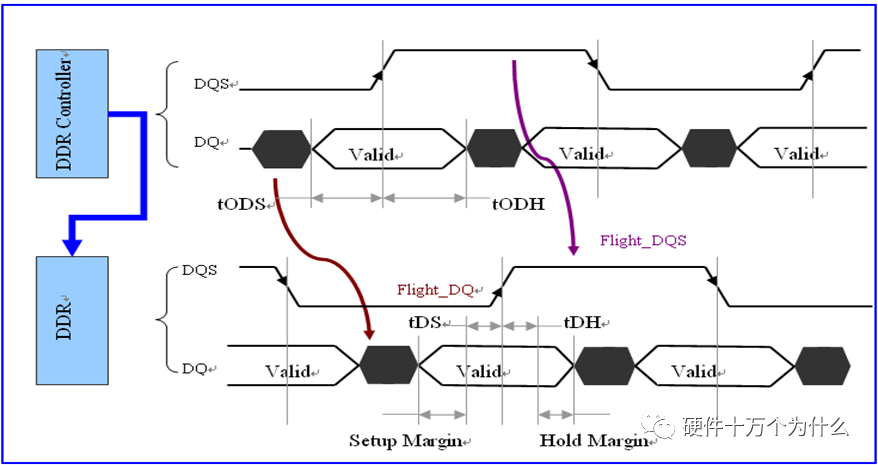

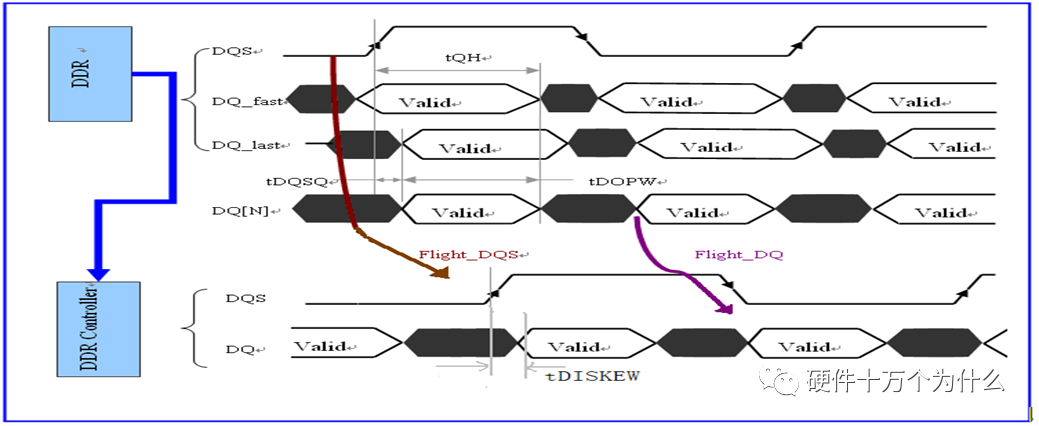

數據信號DQ/DM與數據選通信號DQS的時序關系

寫周期

讀周期

幾種時序關系,后續會做詳解

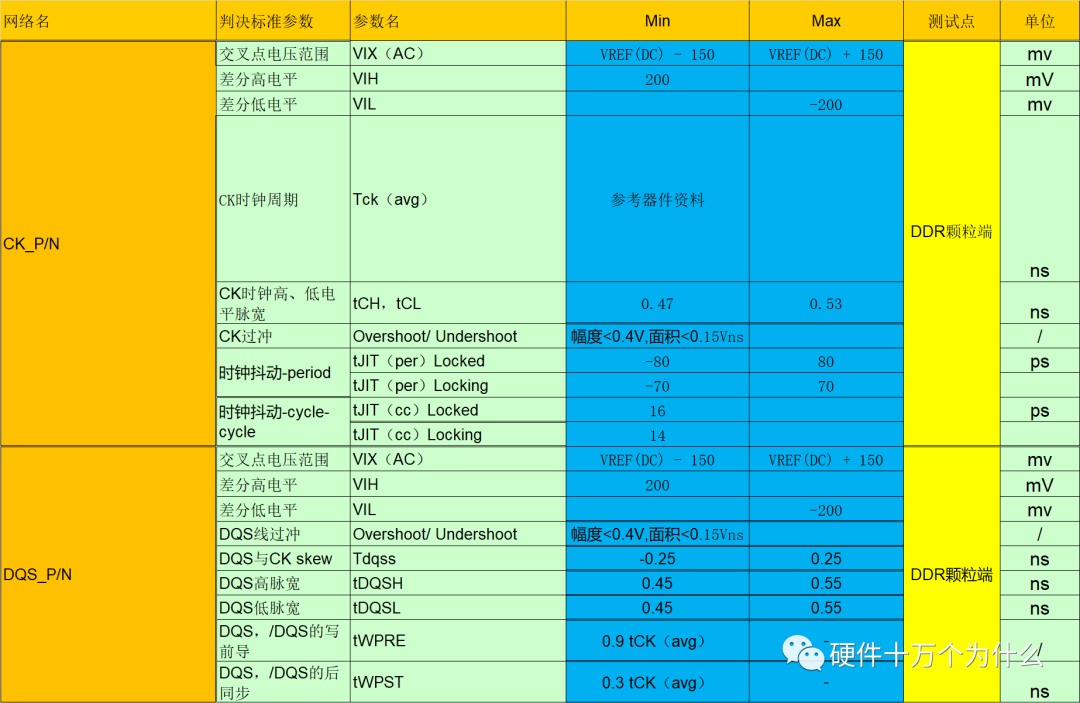

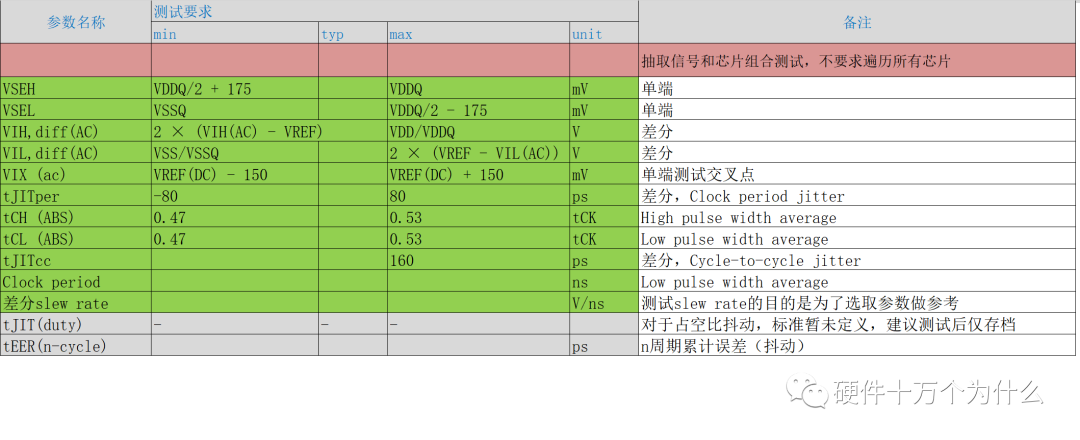

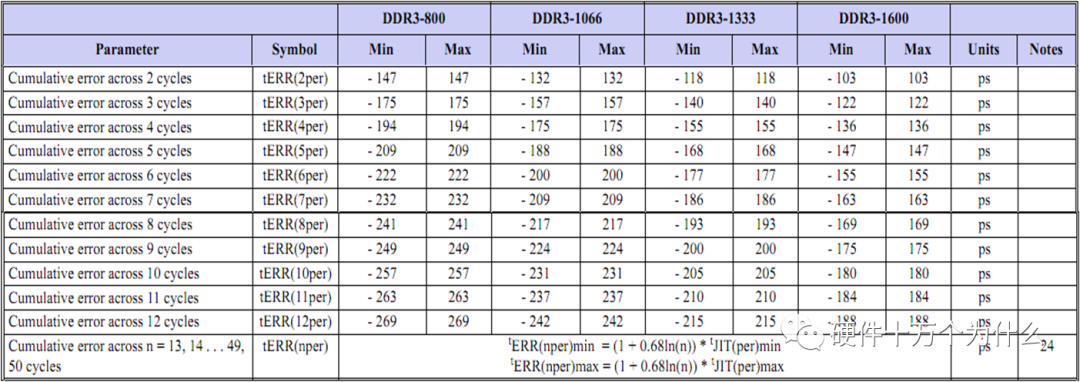

3、DDR時鐘信號(CK、DQS)測試:

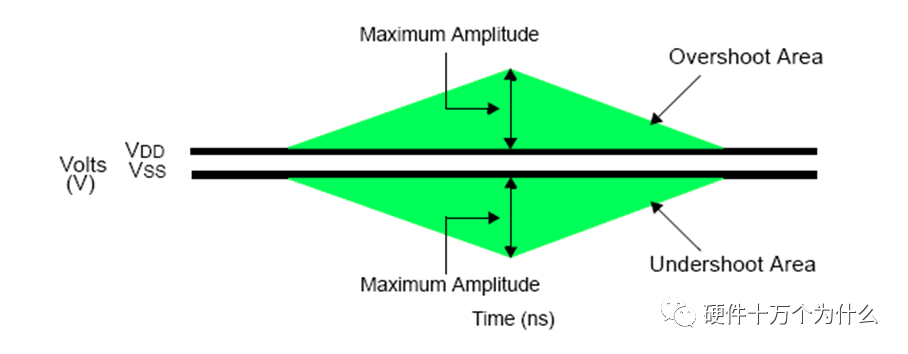

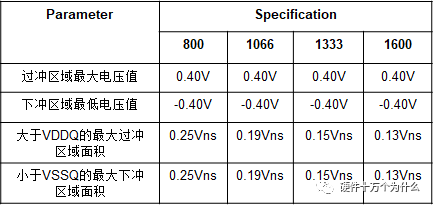

時鐘信號過沖要求

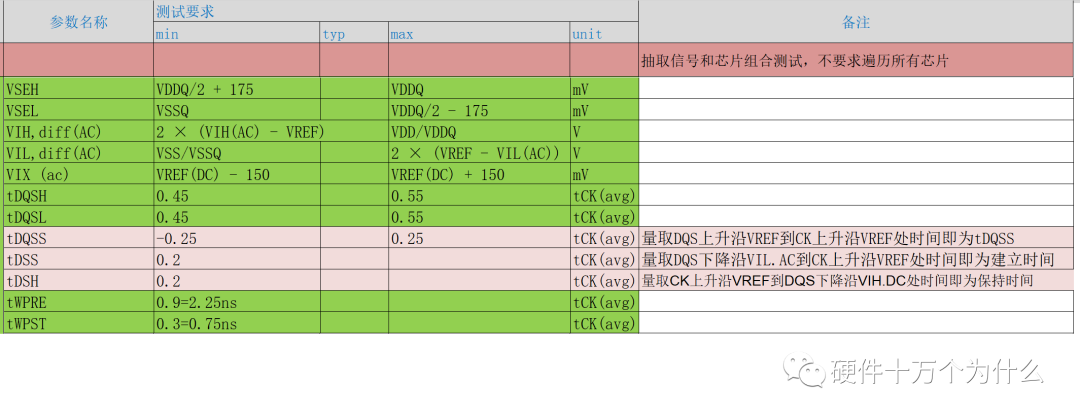

寫方向

CK

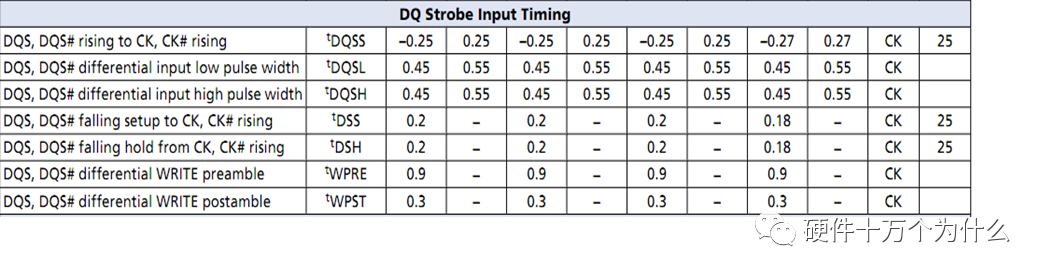

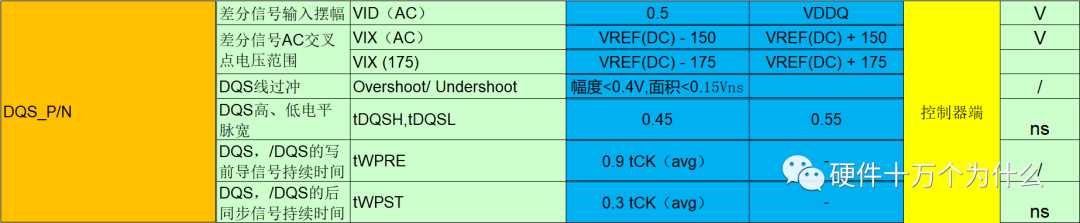

DQS

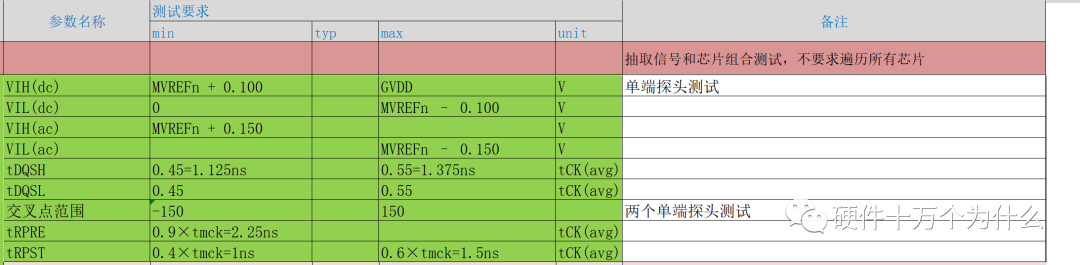

讀方向

審核編輯:湯梓紅

-

示波器

+關注

關注

113文章

6273瀏覽量

185509 -

SDRAM

+關注

關注

7文章

429瀏覽量

55285 -

DDR

+關注

關注

11文章

712瀏覽量

65420

原文標題:【硬件的單元測試_6】DDR3信號測試1

文章出處:【微信號:Hardware_10W,微信公眾號:硬件十萬個為什么】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

5V 輸入、10A負載DDR3/DDR4通用電源解決方案

泰克公司推出市面上性能最高的DDR3協議測試解決方案

ddr4和ddr3內存的區別,可以通用嗎

模擬DDR3的地址信號與時鐘信號資料下載

關于Virtex7上DDR3的測試例程詳解

Virtex7上DDR3的測試例程

完整的DDR、DDR2和DDR3內存電源解決方案同步降壓控制器數據表

完整的DDR2、DDR3和DDR3L內存電源解決方案同步降壓控制器TPS51216數據表

全套DDR、DDR2、DDR3、DDR3L、LPDDR3 和 DDR4 電源解決方案同步降壓控制器數據表

完整DDR,DDR2,DDR3 和LPDDR3 存儲器電源解決方案同步降壓控制器數據表

DDR3信號測試解決方案

DDR3信號測試解決方案

評論