如果摩爾定律有什么是能夠讓人真切感受到的,那就是隨著時間的推移,晶體管變得越來越小。在過去10年間,科學家和工程師們將這種趨勢發展到了近乎荒謬的地步,他們創造出由單原子厚度材料制成的器件。

這些材料中最著名的當然是石墨烯,它是一種六邊形的蜂窩狀碳片,具有出色的導熱性、電導率、奇特的光學性能和難以置信的機械強度。但作為一種用于制造晶體管的物質,石墨烯并沒有真正發揮作用。由于沒有自然的能帶隙(使半導體具有半導體的特性),它并不適合用于制造晶體管。

相反,科學家和工程師們一直在探索過渡金屬二硫化物的相關領域,這類物質的化學分子式都為MX2。它們是由十幾種過渡金屬(M)中的一種和三種硫屬化合物(X,即硫、硒或碲)中的一種組成。二硫化鎢、二烯化鉬和其他一些材料可以在單原子層中制成(與石墨烯不同)天然半導體。這些材料具有廣闊的應用前景,即使如今的硅技術已經基本接近發展的盡頭,我們也能將晶體管縮小為原子厚度的組件。

這種想法令人感到興奮,我和我在比利時微電子研究中心(Imec)的同事們相信,盡管硅材料仍是該領域的主導者,但2D材料會很快出現。我們一直在研究并開發一項技術,將2D半導體應用于硅芯片,增強硅片性能和簡化設計。

2D材料制成的器件是值得我們和其他研究人員投入的科學工程,因為這種技術將能夠消除當今晶體管所面臨的一個最大的問題,即短溝道效應,這是幾十年來晶體管持續縮小所帶來的結果。

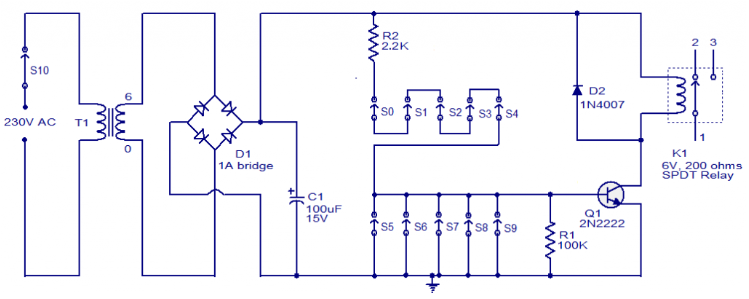

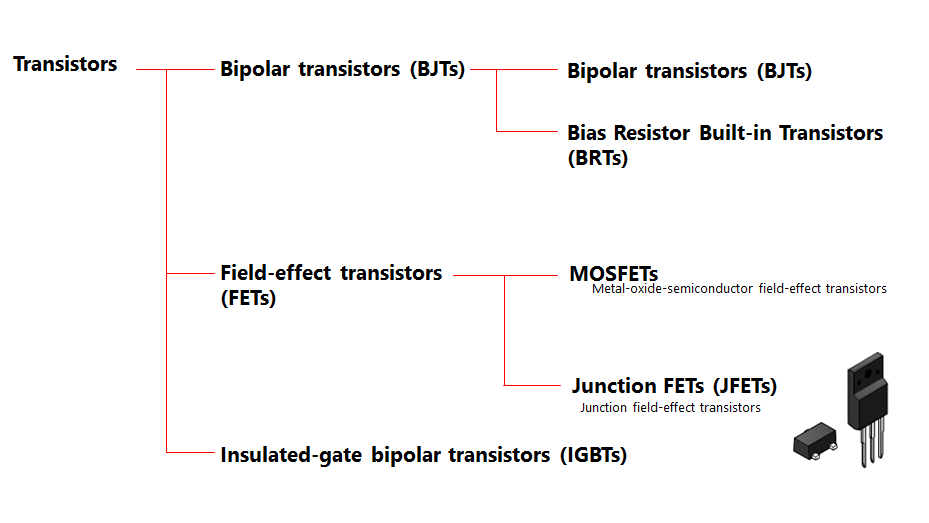

金屬氧化物半導體場效應晶體管(MOSFET)是數字器件中的一種,它由5個基本部分組成:源極和漏極;連接它們的溝道區域;覆蓋溝道的一個或多個側面的柵極介電層;以及與電介質接觸的柵極。在柵極處施加相對于源極的電壓,在溝道區域生成一層移動電荷載體,在源極和漏極之間形成導電橋,允許電流流動。

但是隨著溝道變得越來越小,即使柵極上沒有電壓,漏電流也會不斷增加,浪費電能。20世紀的二維設計發展成為如今最先進的處理器中使用的鰭式場效應晶體管(FinFET)結構,就是為了使溝道區域變薄,并使柵極從更多的側面圍繞溝道區域,來對抗這種短溝道效應。由此產生的鰭狀結構可實現更好的靜電控制。

我們認為,通過替換器件溝道中的硅,某些2D半導體可以規避短溝道效應。2D半導體提供了一個非常薄的2D區域——如果僅用一層半導體,它就和單原子一樣薄。由于限制了電流的路徑,當器件處于關閉狀態時,電荷載流子幾乎沒有機會偷偷通過。這意味著晶體管可以繼續縮小,減少對短溝道效應后果的擔憂。

這些2D材料不僅可用作半導體。某些材料,如六方氮化硼,也可以作為柵極介電層,其介電常數與二氧化硅的介電常數相似,直到十幾年前二氧化硅才廣泛應用于這一領域。用石墨烯代替晶體管的金屬部件,可組成完整的晶體管2D材料。事實上,早在2014年,就有不同的研究小組制造出這樣的器件。雖然這些原型尺寸很大,但你可以想象我們可以將它們的尺寸縮小到幾納米。

讓人感到不可思議的不僅在于全2D晶體管的尺寸可比如今器件的尺寸還小,而且在于電子電路不會是2D材料的首個應用。2D材料可能將會應用在性能要求和面積限制比較寬松的低功耗電路中。

我們在Imec研究的目標是所謂的后端工序制造的電路。芯片的制造分為兩部分:前端工序需要許多高溫工藝,改變硅自身的屬性,例如用摻雜來定義晶體管;后端工序是構建多層互連線,這些互連線將晶體管連接起來,形成電路和提供電源。

隨著傳統晶體管縮小變得越來越困難,工程師們一直在尋找提升互連層性能的方法。我們無法簡單地通過使用常規硅工藝來做到這一點,因為產生的熱量會損壞器件和器件下方的互連。因此,許多方案都依賴于能夠在相對較低溫度下制成器件的材料。

使用2D半導體而非其他候選材料的一個特殊優勢是可以同時制造p型(攜帶正電荷)和n型(攜帶電子)器件,這是互補金屬氧化物半導體(CMOS)邏輯電路的必要條件。CMOS電路是當今邏輯電路的支柱,因為理想情況下,電路只在從一種狀態轉換到另一種狀態時才消耗能量。在我們首選的2D半導體中,我們已經演示了n型晶體管,但還沒有演示p型晶體管。但是,這些材料背后的物理學原理清晰地表明,我們制作中可以通過與半導體接觸的介質和金屬來實現。

如果能同時制造p型和n型器件,就能開發出緊湊的后端邏輯電路,如中繼器。中繼器對必須在芯片上進行相對遠距離傳遞的數據進行轉發。涉及的晶體管通常位于硅層,信號必須先爬上互連層,在互聯層向目的地傳輸一部分距離,然后回到硅層,進行中繼后再回到長距離互連層。這有點像汽車駛離高速公路,開到一個擁擠的城市中心去買汽油,然后再回到高速公路上。

長距離互連層附近的中繼器更類似于高速公路加油站。它節省了信號垂直雙向傳輸的時間,也避免了垂直互連電阻造成的功率損失。更重要的是,將中繼器移到互連層可以節省硅片上的空間來實現更多的邏輯。

中繼器并不是2D材料唯一的潛在用途。2D材料也可以用于構建其他電路,如片上電源管理系統、信號緩沖器和存儲器選擇器。這些電路的一個共同點是,它們不需要器件驅動大電流,因此一層2D材料就可滿足。

如果沒有與工業標準300毫米硅片相兼容的制造工藝,未來的超小型2D器件和低需求的后端工序電路都無法實現。因此,我們Imec的團隊正致力于此,希望開發一種適合所有應用的制造工藝。

第一步是確定最具應用前景的2D材料和器件結構。因此,我們參照先進的鰭式場效應晶體管(FinFET)器件,對各種2D半導體材料和2D場效應晶體管(FET)架構進行基準測試。

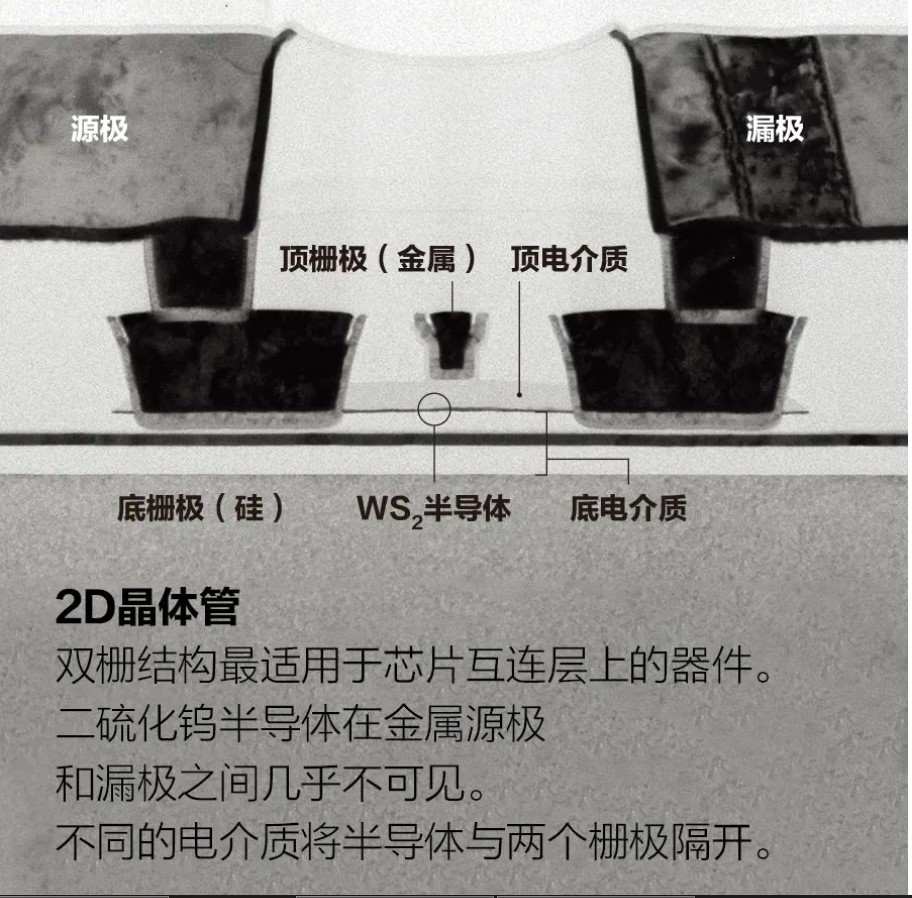

由于研究人員對二硫化鉬(MoS2)的研究經驗最為豐富,因此使用MoS2制作的實驗器件取得了最大的進展。實際在去年12月的IEEE國際電子器件會議上,Imec發布了一種MoS2晶體管,其溝道長度只有30納米,源極和漏極觸點只有13納米。但是經過可用性檢驗,我們認為MoS2不是最終結果。相反,我們得出結論,在與300毫米硅片技術兼容的所有材料中,用二硫化鎢(WS2)制成的堆疊納米器件具有最大的性能潛力,它可以驅動最多的電流。對于需求較低的后端工序線路應用,我們也得出結論,在半導體溝道區域上下都有柵極的FET結構比只有一個柵極的FET結構性能更加出色。

在得出這個結論之前,我們已經非常了解WS2:我們可以在一個300毫米的硅片上做出一個高質量版本。我們在2018年首次演示了利用金屬-有機化學氣相沉積(MOCVD)在硅片上生長材料,這是一種通過化學反應在晶片表面生長晶體的常見工藝。我們采用的方法可在整個300毫米晶片上將可控厚度降低到單分子層,即單層厚度。然而,MOCVD生長是以高溫為代價的,而在后端工藝中是禁止高溫的,因為高溫會損壞下方的硅器件。

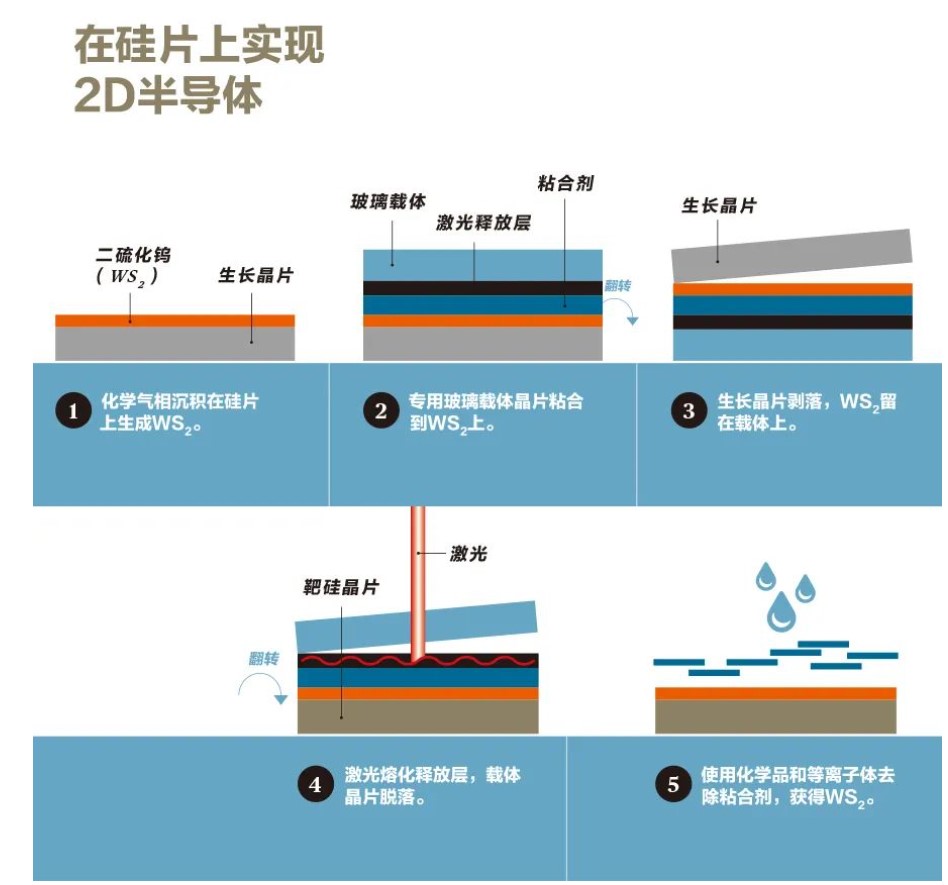

為解決這一問題,我們先在一個單獨的晶片上生長WS2,然后將其轉移到已經部分制成的硅片上。Imec團隊開發了一種獨特的轉移工藝,能夠將一層只有0.7納米薄的WS2轉移到靶硅晶片上,幾乎不會損害2D材料的電性能。

在此工藝中,首先在氧化覆蓋的硅片上生長WS2,然后將其放在特殊處理的晶片上。這種晶片上有一層材料,在激光照射下會發生熔化。此外,還有一層粘合劑。將粘合劑側壓在覆蓋WS2的晶片上,2D材料從生長晶片上剝離并粘附在粘合劑上。之后,帶有2D材料的粘合晶片翻轉到靶硅晶片上,靶晶片在實際的芯片制造中已經有了晶體管和幾層互連。接下來,通過一束激光照射晶片,將其大部分熔化,只留下靶晶片上的粘合劑和WS2。用化學藥品和等離子體除去粘合劑。剩下的就是處理過的硅和附著的WS2,通過范德華力加以固定。

這種工藝雖然復雜,但卻十分有效。當然,還有很大的改進空間,最重要的是減少晶片表面不必要的顆粒造成的缺陷,同時消除邊緣的一些缺陷。

2D半導體材料制成后,就可以開始制造器件了。我們在這方面已經取得了勝利,但仍存在一些重大挑戰。

也許最關鍵的問題是如何處理WS2中形成的缺陷。這種缺陷嚴重降低了2D器件的性能。在一般的硅器件中,電荷會在柵極電介質和溝道區域之間的接口缺陷中被捕獲。當電荷試圖穿過器件會在接口附近散射電子或空穴,造成速度減慢。在二維半導體中,由于接口是溝道,散射問題更加明顯。

硫空位是影響器件溝道區域的最常見缺陷。Imec正在研究不同的等離子體處理如何減小這些空位化學反應,從而減小晶體管性能改變的傾向。我們還需要防止單層生長后出現缺陷增加。如果WS2和其他2D材料存在缺陷,則會迅速老化并進一步退化。氧攻擊硫空位會造成附近出現更多空位,使缺陷面積變得越來越大。但我們發現,將樣本儲存在惰性環境中,可以有效防止空位增多。

半導體的缺陷并不是我們在制造2D器件時遇到的唯一問題。在2D表面上沉積絕緣材料形成柵極電介質才是一項真正的挑戰。WS2和類似的材料缺乏懸空鍵,不利于將電介質固定在表面上。

我們的團隊目前正在探索兩種可能的有效途徑:

一種是降低生長溫度的原子層沉積(ALD)。在ALD中,一種氣體分子吸附在半導體的暴露表面,形成單層。然后加入第二種氣體,與吸附的第一種氣體發生反應,形成精確的原子物質層,如介電二氧化鉿。即使沒有化學鍵,在低溫下采用這種工藝也能夠提升氣體分子粘附在WS2表面的能力。

另一種方案是使用非常薄的氧化層(如氧化硅)來增強ALD,以幫助ALD層的成核生長。采用物理沉積方法(如濺射或蒸發)沉積極薄的硅層;然后再進行氧化,完成一個常規氧化柵的ALD沉積。我們使用蒸發法取得了良好的成果。

制造優質2D器件的另一項挑戰是選擇合適的金屬作為源極和漏極觸點。金屬的性能可改變器件的特性。從金屬中提取電子所需的最低能量這一參數,表示注入觸點電子及空穴的差異。因此,Imec小組篩選了多種金屬,與WS2納米片接觸。我們發現,在n型器件中,使用鎂觸點可以獲得最高的通流,而鎳或鎢等其他金屬也不錯。我們將為未來的p型器件尋找多種金屬。

盡管存在這些挑戰,但是我們已經能夠判斷器件性能的上限,以及規劃實現這一目標的路徑與方法。

作為一個基準測試,Imec團隊使用了與之前描述類似的雙柵極器件。我們用小的、自然剝離的WS2薄片制造器件,這種薄片的缺陷比晶片大小的半導體要小。對于這些實驗器件,我們測量的電子遷移率高達每伏特秒幾百平方厘米,幾乎與晶體硅相持平,而且接近理論預測的2D材料的最大值。由于在自然材料中發現這種優異的遷移率,因此我們有信心在300毫米晶片上的合成材料也可以達到這一目標(目前這種材料只能達到每伏特秒幾平方厘米)。

對于未來二維半導體發展的主要挑戰,我們的團隊已有一個明確的解決方案。例如,我們知道材料如何生長并轉移到300毫米的靶晶片上;我們知道如何整合關鍵的柵極電介質;我們正致力于將器件電荷載流子的遷移率提高到與硅相當的水平。

但是,正如我們所指出的,目前的技術中仍然存在一些重大問題。這需要加強工程努力,以及在本質上增加對這類新型2D材料的了解。解決這些挑戰將有助于把高性能器件縮小到原子層,不過,在我們繼續縮小硅片的過程中,這些器件也可能首先實現一些指標需求不高的新功能。

審核編輯:劉清

-

MOSFET

+關注

關注

147文章

7212瀏覽量

213818 -

晶體管

+關注

關注

77文章

9723瀏覽量

138620 -

數字器件

+關注

關注

0文章

9瀏覽量

9978

原文標題:原子厚度的晶體管

文章出處:【微信號:深圳市賽姆烯金科技有限公司,微信公眾號:深圳市賽姆烯金科技有限公司】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

什么是單極型晶體管?它有哪些優勢?

晶體管的主要材料有哪些

GaN晶體管和SiC晶體管有什么不同

基于量子干涉技術的單分子晶體管問世

基于晶體管的電路圖分析

一種用于制造晶體管的單原子厚度材料

一種用于制造晶體管的單原子厚度材料

評論