監控系統中對更高質量視頻圖像的需求需要在傳感器和可用視頻數據之間建立高級鏈接。僅由軟件處理組成的圖像處理系統無法滿足這些需求,基于ASIC的系統無法提供所需的靈活性。由于像素處理的計算密集型特性,使用JPEG2000編碼的基于FPGA的成像處理設計提供了一種強大而靈活的方法。

高清數字視頻已變得司空見慣;我們大多數人都在自己的家中擁有高清設備。然而,將該技術轉移到實時軍事監視應用在捕獲高清圖像和分發大量數據方面帶來了重大挑戰。圖像傳感器現在正在千兆像素領域生產,使用較小的百萬像素探測器陣列實現。圖像數據采集必須靈活,以便于與各種傳感器接口,并且必須與數據處理和壓縮緊密耦合才能分發數據。與傳統軟件或ASIC成像處理系統相比,利用FPGA協處理器具有許多優勢,并且可以將復雜的算法打包到一個小型,功能強大的設備中。

因此,基于FPGA的處理器可以在高清圖像傳感器和低帶寬JPEG2000壓縮數據之間提供關鍵鏈路。可重構計算的這一趨勢使得滿足機載和地面車輛平臺(如捕食者無人機、收割者無人機、蜂鳥無人機直升機、MULE自主地面機器人、浮空器等)中強大成像系統的需求成為可能。基于 FPGA 的高性能計算允許軍事監視系統接收和處理來自各種來源的高清傳感器數據,并使用 JPEG2000 壓縮數據以進行傳輸。

像素處理對于 FPGA 而言是無痛的

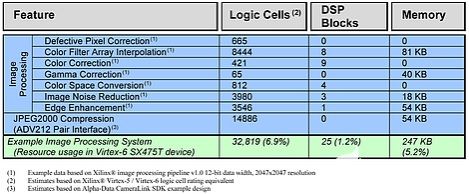

圖像像素處理的高度計算特性可以在現代FPGA器件中高效實現。Virtex-6 SX475T FPGA 具有超過 475 K 個邏輯單元和 2,016 個嵌入式 DSP 模塊,可靈活連接到系統的其余部分,包括集成的 6.5 Gb 收發器以及許多其他功能強大的元件。這些特性允許在單個FPGA器件中將許多圖像處理功能流水線連接在一起,用于多個圖像傳感器。表1中詳述的示例圖像處理設計表明,全功能圖像處理和壓縮通道只需要不到7%的FPGA資源。

表 1:圖像處理系統示例 – FPGA 資源要求

(單擊圖形可縮放 1.9 倍)

圖像處理系統需求:夠硬嗎?

軍事監視系統希望能夠查看廣闊的區域,例如大于16平方公里,因為“通過蘇打吸管觀察”無法獲得太多信息。此外,監控系統通常必須在距離目標數公里的距離內運行,以保持安全,同時生成高分辨率圖像。所有這些都需要捕獲和處理大量的圖像數據。例如,DARPA ARGUS-IS系統使用368個500萬像素探測器(總計1.8千兆像素),能夠生成超過260 Gbps的原始數據。

這些數據必須在實時系統中捕獲和處理,通常具有極端的SWaP限制。此外,成像系統在捕獲原始像素數據后可能需要許多其他所需的功能才能使用:

有缺陷的像素校正

彩色濾光片陣列插值

色彩校正

伽瑪校正

色彩空間轉換

圖像降噪

邊緣增強

視頻縮放

視頻窗口 – 對象跟蹤

穩

視頻壓縮(JPEG2000、H.264、MPEG-4)

數據加密

用于傳輸和/或存儲的視頻輸出

基于FPGA處理器的可重構計算技術非常適合滿足這些苛刻的需求。這種方法比專用軟件處理系統更小、更快、更高效,并且比ASIC方法更靈活、更具成本效益。圖像傳感器和軟件處理之間的基本環節非常適合FPGA技術。

適應各種圖像傳感器接口

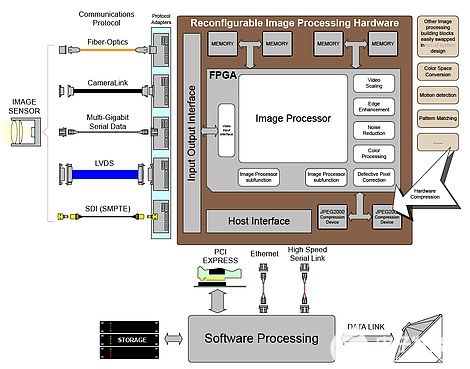

監控系統和其他成像平臺正在迅速發展和擴展,以利用各種傳感器進行光學,紅外和合成孔徑雷達技術,并且圖像尺寸一直在增加。圖像傳感器的物理接口各不相同,因此處理系統需要一個靈活的模塊化接口,以便與這些系統一起擴展和擴展。可重構計算系統通過支持多種格式和物理接口的傳入數據來滿足這一需求,例如,CameraLink、SDI、原始像素、LVDS、多千兆位串行接口、光纖等。基于FPGA的系統非常適合從各種來源和協議采集圖像數據,因為具有可編程I/O模塊、集成收發器和SERDES模塊。

此外,監控系統可能具有許多不同的任務目標,這些目標需要在處理視頻數據時具有靈活性。例如,系統可能需要每隔幾秒鐘提供整個視場的全分辨率圖像,或者使用較小的圖像窗口跟蹤移動目標,該窗口以10 Hz更新。系統可能需要控制圖像系統具有的數據帶寬,以便下行鏈路或存儲數據以供以后傳輸。基于FPGA的圖像處理器可以在系統中重新配置,從而允許在不修改硬件的情況下添加升級和附加功能,例如模式匹配或運動檢測。與任何預定義的圖像采集卡或基于ASIC的硬件相比,這是一個很大的優勢。圖1顯示了可重構圖像處理系統的靈活性,該系統能夠從各種源和接口接收圖像數據,實現一系列計算復雜的圖像處理功能,并通過各種接口輸出壓縮的視頻流。

圖 1:可重構圖像處理硬件的靈活性

使用 JPEG2000 進行前期數據壓縮

從任何系統中的彩色圖像傳感器接收的數據必須首先進行插值以獲得每個像素的RGB分量,然后通常轉換為YCrCb色彩空間,以使用色度子采樣來減少數據量。然而,通過使用FPGA處理系統,視頻數據可以使用JPEG2000進一步壓縮,并且在無損壓縮中將帶寬額外減少2:1,在視覺無損壓縮中減少10:1,在有損壓縮中最大可降低100:1。FPGA圖像處理器提供的壓縮數據允許系統輕松存儲,通過軟件進一步處理,并將數據傳輸給用戶。使用 JPEG2000 進行圖像數據壓縮可為系統提供卓越的結果,而無需預先進行數據壓縮,并減少系統需要處理的數據。

JPEG2000編解碼器在軍事監視應用中特別受歡迎,因為它提供了非常高的性能,低延遲,執行無損壓縮的能力以及其他非常有用的功能。這種壓縮標準的工作原理是使用小波變換將單個圖像幀分解成分辨率越來越低的子波段。然后將數據排列成數據包,其中包含有關連續像素組的信息。生成的圖像流提供了有用的功能,例如可選區域、可選分辨率、錯誤恢復能力和帶寬限制,此外還允許系統以圖像流的壓縮格式使用它。例如,JPEG2000數據可用于遠程監控系統,以從相同的圖像傳感器下行鏈接小型高清圖像窗口或廣域快照的靈活組合,而無需先解壓縮數據。

它也可以在特定帶寬下使用,只需提取部分JPEG2000數據并截斷流的更高分辨率部分即可。這對于傳輸圖像數據非常有用,因為圖像中最重要的信息可以使用不到20%的JPEG2000數據流來傳遞。由于每個視頻幀都經過單獨壓縮,因此進一步增強了這種誤差恢復能力,這使得數據鏈路能夠以較少的糾錯方式運行。因此,與其他壓縮標準相比,JPEG2000對數據丟失的擔憂較少,后者需要來自多個幀的信息進行解碼。最后,JPEG2000數據可以在同一原始流中以不同的分辨率和質量進行查看。

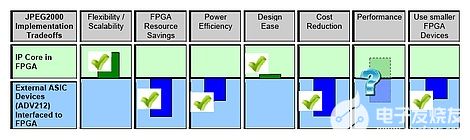

雖然JPEG2000編碼器的實現相當復雜,但FPGA提供了大量資源,可以在圖像處理設計中包含此功能。有一些 IP 核可隨時集成到 FPGA 設計中,或者 FPGA 可用于與 ADV212 ASIC(JPEG2000 片上系統)接口。這兩個選項都有自己的優點和缺點(表2),這些編解碼器選項中的任何一個都可以在COTS硬件上使用,例如阿爾法數據ADM-XRC-5T2-ADV夾層FPGA板。

表 2:在 FPGA 中使用 IP 核實現 JPEG2000 圖像壓縮時,與使用連接到 FPGA 的外部 ASIC 設備相比,需要進行設計權衡。

將 COTS FPGA 硬件用于圖像處理器

為了 促進 高級 圖像 數據 處理, 模 塊 化 FPGA 圖像 處理 板 ( 例如 基于 PMC/XMC 的 板 卡 ) 可以 用于 工業 標準 的 嵌入式 計算 系統, 包括 CompactPCI、 VME、 VXS、 VPX、 PCI、 PCI Express 和其他 外 形 規格 中的 系統。這些小型 (74 mm x 144 mm) 模塊可與最大的 FPGA 器件一起使用,可用于工作站開發系統,或直接移至堅固耐用的部署監控系統中。對于 JPEG2000 壓縮,COTS 板提供 IP 核所需的大量板載內存和/或專用 JPEG2000 專用集成電路。主機計算系統可以輕松控制硬件圖像處理器卡以應用用戶設置,重新配置FPGA以進行各種視頻操作,控制圖像窗口,命令目標跟蹤以及接收輸出視頻流。這種COTS硬件通常提供軟件驅動程序和API接口,使控制和數據傳輸在系統中無縫。

審核編輯:郭婷

-

處理器

+關注

關注

68文章

19286瀏覽量

229842 -

dsp

+關注

關注

553文章

7998瀏覽量

348931 -

FPGA

+關注

關注

1629文章

21736瀏覽量

603387

發布評論請先 登錄

相關推薦

基于FPGA的可重構系統結構分析

求一種可重構測控系統的設計構想

面向可重構系統的一種功耗相關硬件任務調度算法設計

一種基于體系結構模板的粗粒度可重構SoC設計方法

一種可重構的硬件處理器方法

一種可重構的硬件處理器方法

評論