作者:JASON WADE,RANDALL MILLAR

軍方依靠視頻圖像進行態勢感知,但圖像質量通常很差,以至于操作員可能會錯過重要細節。為顯示控制器配備實時運行圖像增強算法的FPGA,為觀看者提供更好的圖像。

現代國防能力、情報、監視和偵察 (ISR) 的支柱依賴于由集成傳感器、飛機和人力組成的強大而多樣化的網絡。該網絡的價值最終取決于人類能夠清楚地看到傳感器圖像,識別重要細節并采取果斷行動。在現場,我們很少或根本無法控制從傳感器獲取圖像的照明和環境條件。但是,可以通過允許查看實時傳感器圖像的人實時微調視頻圖像以提取更多信息來為他們提供更多控制。

實時增強視頻需要巨大的計算吞吐量。它需要將復雜的圖像處理算法應用于傳入的視頻流,而不會引入延遲。高性能現場可編程門陣列(FPGA)提供了一個理想的平臺,允許使用并行計算技術實現軟件算法。當嵌入到智能顯示控制器中時,這些算法使操作員能夠最大程度地控制圖像質量,并顯著提高圖像清晰度。

清晰度在旁觀者的眼中

全動態視頻 (FMV) 是軍事態勢感知的首選工具。幾乎所有軍用車輛都有自動視頻錄制功能,包括戰斗機、卡車和坦克等載人船只,以及無人駕駛飛機系統(UAS)。在移動平臺上生成高質量圖像會帶來許多挑戰。除了與攝像機運動和由此產生的圖像透視相關的問題外,視頻圖像的質量還可能因惡劣的環境條件、數據鏈路降級和帶寬限制而受到影響。大氣因素(如黎明、黃昏或夜間照明不佳)以及惡劣天氣(包括沙塵暴和多變的云層)可能會遮擋重要細節。

然而,傳感器圖像質量并不是唯一的問題。觀看視頻的條件差異很大,因此帶來了另一組挑戰。例如,視頻流可以在明亮的陽光下、水下或屏幕上有前照燈的黑暗洞穴中觀看。因此,在顯示器本身內提供圖像增強功能具有明顯的優勢,而不是在傳感器或網絡上的其他地方。

確保良好圖像質量的唯一方法是讓觀看者能夠根據自己的需要調整圖片。實現這一目標的最佳方法是為戰術邊緣帶來實時視頻增強。FPGA 提供 將 這種 功能 直接 構建 到 顯示 控制器 中 所需 的 性能、 設計 靈活 性 和 彈性。

具有實時圖像增強功能的視頻控制器

所有顯示控制器都執行基本圖像處理,這意味著它們以特定分辨率接收視頻并以顯示器的原始分辨率顯示。例如,如果它是 1,920 x 1,080 的顯示器,則它需要為每一幀接收 1,920 x 1,080 像素。但是,不能保證用戶將插入與此匹配的柵格。事實上,他很可能不會。相反,傳入的視頻流的格式可能為 1,024 x 768 或類似格式。視頻處理是縮放行為,即將傳入的視頻信號從一種大小或分辨率轉換為另一種大小或分辨率,以便與顯示面板配合使用。這就是通常所說的“視頻處理”,與視頻增強相比,這是一項小壯舉。

視頻增強從視頻處理結束的地方開始。專為實時視頻增強而設計的視頻控制器可能從現成的視頻處理芯片或專門構建的ASIC開始,該芯片可以預先進行縮放和基本圖像處理。一旦該操作完成,視頻流將被傳遞到特殊用途的處理器,如FPGA以進行增強。

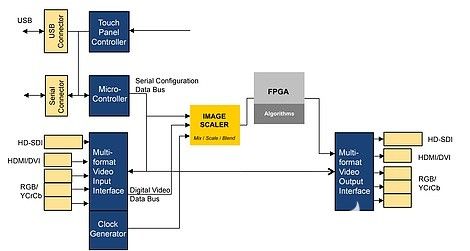

當然,可以選擇將視頻處理和視頻增強功能組合在一個ASIC中。事實上,這是消費類電視制造商經常做的事情。但是,這種實現最適合基本的視頻增強,例如邊緣銳化,并且幾乎沒有為復雜的圖像增強算法留下多少空間。通過內置于實時視頻增強的FPGA,可以超越傳統的顯示功能并提供高級增強功能(圖1)。

圖 1:具有內置實時視頻增強功能的顯示控制器:視頻處理芯片對傳入的視頻流進行格式化,以滿足顯示要求。FPGA運行圖像增強算法,以實現顯著更好的圖像清晰度。

驚人的算法是計算密集型的

任何熟悉照片編輯程序(如 Adobe Photoshop)的人都可以欣賞軟件算法在增強靜止圖像方面的強大功能。使用復雜的軟件算法將數學函數應用于圖像矩陣,可以在不丟失細節的情況下揭示隱藏的視覺信息層。這是一種純粹的數學方法,利用所有可用的圖像信息,包括人眼通常不可見的部分。

在過去的幾十年中,使用直方圖操作、卷積、形態學、過采樣和欠采樣、量化和光譜處理(包括傅里葉變換和離散余弦變換 (DCT))等技術開發了大量的圖像處理算法。這些算法往往是計算密集型的。傳統的處理器技術無法提供滿足 FMV 所需的性能,速度高達 60 幀/秒 (fps),或每 16.67 毫秒 1 幀。處理標清 (SD) 視頻流需要大約 150 到 200 千萬億次浮點運算,而 1,080p 流需要大約 1.2 萬億次浮點運算。這就是 FPGA 發揮作用的地方。

卷積核過濾在工作

當使用并行處理技術重寫圖像增強算法并移植到FPGA時,可以實時顯著增強ISR視頻。在多種類型的圖像增強算法中,空間卷積核濾波產生的結果最顯著。

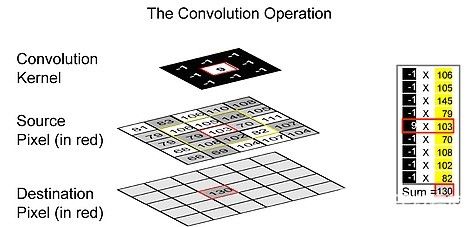

雖然卷積濾波的基礎數學很復雜,但執行圖像卷積運算非常簡單。卷積核根據感興趣的像素值與其周圍像素的值之間的關系生成新的像素值。在卷積中,兩個函數相互疊加和相乘。其中一個函數是視頻幀圖像,另一個是卷積核。幀圖像由一大數組表示,這些數字是 x 軸和 y 軸中的像素值。卷積核是一個較小的數組,或一個掩碼,其中的值是根據所需的過濾函數(例如,模糊、銳化和邊緣檢測)分配的。此數組的大小(稱為內核大小)確定將使用多少個相鄰像素來生成新像素。在卷積中,內核對圖像進行操作,以便在每次應用掩模時創建一個新像素,因此必須對圖像中的每個像素重復該操作(圖 2)。

圖 2:卷積核掩碼操作:源像素被自身及其相鄰像素的加權平均值替換。

大果仁產生更好的結果

卷積是計算密集型的,因此大多數實現僅使用小內核(3 x 3,9 x 9,16 x 16)。但是,使用獨特的非傳統編程技術,可以實現非常大的卷積核,從而產生更好的結果。非常大的內核產生更好結果的原因與給定區域(稱為空間頻率)上亮度的范圍和變化有關。

在處理時,通過考慮以每個像素為中心的大型鄰域中的數據,大內核包含更大的空間頻率范圍。傳統的小核處理只能增強最高空間頻率下的細節,這些頻率通常只包含圖像的光譜內容(全色范圍),并且是噪聲普遍存在的地方。因此,小型內核處理器必須采用高增益才能對圖像產生明顯的影響。高增益往往會產生清晰的輪廓偽像,并增加可見的噪點。大的內核處理(在圖像的更多“肉”上操作)可以產生顯著的結果,增益要低得多,并具有大面積著色的額外好處,產生更自然的圖像,增加局部對比度,增加維度,并改善細微細節和特征的可見性。

一種大型內核卷積算法,旨在通過消除霧霾和增強圖像細節來澄清圖像,使用 400 x 400 內核。該澄清器算法的工作原理是求解一個數學方程,該方程將“完美圖像”的模型與傳感器相機捕獲的測量的不完美圖像相關聯。該技術反向工作,去除損壞的噪聲和圖像模糊,同時調整每個像素的強度,直到出現適合實時數據的最簡單的圖像。這個概念是,因為已知環境因素會扭曲圖像,如果知道扭曲是如何產生的,那么它可以被撤消。其他技術使用的方法可以去除失真并接近真實圖像,但僅此而已。相比之下,這種方法更進一步,繼續將算法應用于圖像,直到它盡可能接近完美圖像。因此,它能夠去除所有不屬于真實圖像的不必要的數據。一旦消除了環境失真,并且隨著更多真實圖像的顯現,就會實現非凡的清晰度。

追求完美的形象

FPGA 打開了通往大量復雜算法的大門,這些算法可用于實時增強 ISR 視頻。FPGA是計算主力,非常適合軍用視頻顯示控制器應用。它們可以承受惡劣的環境,并滿足嚴格的軍事要求,包括堅固性、溫度耐受性、可靠性和保證較長的產品壽命。由于 FPGA 可 重新 編 程, 因此 可 實現 設計 靈活 性, 因此 顯示 控制器 可以 輕松 適應 變化 的 視頻 標準 或 特殊 任務 要求。此外,一旦部署,基于FPGA的顯示控制器可以現場升級,以添加附加功能和新的圖像增強算法。

審核編輯:郭婷

-

傳感器

+關注

關注

2551文章

51125瀏覽量

753760 -

FPGA

+關注

關注

1629文章

21742瀏覽量

603540 -

控制器

+關注

關注

112文章

16374瀏覽量

178157

發布評論請先 登錄

相關推薦

FPGA 與微控制器優缺點比較

德州儀器推出兩個全新系列實時微控制器

斷電控制器是控制供電開關的裝置對嗎

EtherCAT主站控制器系統實時性測試

開放式高實時高性能PLC控制器解決方案-基于米爾電子STM32MP135

Led顯示屏控制系統怎么使用 led顯示屏控制器怎么設置

FPGA供電的顯示控制器可實時增強ISR視頻

FPGA供電的顯示控制器可實時增強ISR視頻

評論