目錄

1、基本情況介紹

2、仿真流程對比介紹

2.1、視圖上的差異

2.2、仿真結果處理的差異

2.3、預處理方面差異

2.4、驅動碼型差異

3、結果對比

3.1、讀操作

3.2、寫操作

4、模型的處理

4.1、IBIS模型

4.2、S參數模型

5、報告生成

6、總結

高速信號仿真工具眾多,有較大用戶群體的主要有Sigrity,Siwave,Hyperlynx,ADS,CST等。每個工具背后都有自己的黑科技加持,整體上都在朝著更準確、高效、便捷的目標發展。

本文對比了Siwave和Sigrity在SI仿真上的差異,對于新手用戶來說,可以選擇其中易于上手的一個。作者本人對Siwave更為熟練,Sigrity只是作為日常對比參照,且水平有限,其中有理解錯誤的地方,歡迎專家老師指點。同時,仿真用到的圖紙文件也會放在文章末尾,歡迎各位下載學習。

1、基本情況介紹

本文仿真對象為恩智浦公司官網的i.MX8QXP開發板。(i.MX 8處理器家族高度集成,是英飛凌公司的一款非常具有代表性的產品,其廣泛應用于工業控制,智慧城市,智能家居和汽車電子等領域,可支持圖形、視頻、圖像處理、音頻和語音功能,能夠滿足安全認證和高能效方面的需求。)

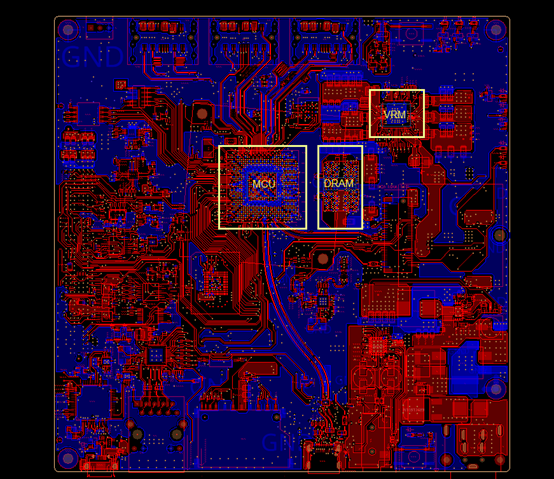

PCB布局整體如下圖所示,橙色方框標注的MCU-DRAM-VRM系統為本文主要仿真對象,目標信號為LPDDR4信號。

圖1、開發板PCB整體視圖

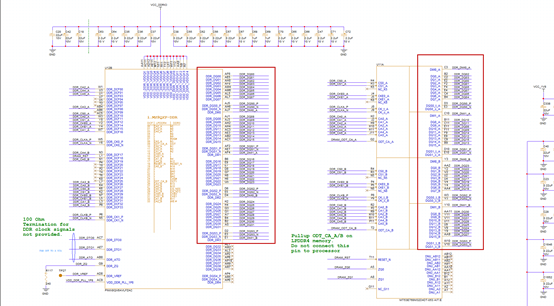

從圖2原理圖中可以看出(紅色方框),目標IC設計中包含了4組數據信號,就對該4組數據信號進行仿真,地址線的仿真方法相同,因此本文不再重復。(根據DDR信號規范,數據信號為整個DRAM系統中速率最快的信號,其次是地址信號,是仿真和測試重點關注的網絡,由于整個仿真過程需要參照JEDEC標準規范要求,因此需要對DDR信號規范有一定的了解,不了解的讀者可以翻閱本人之前有關DDR4的相關介紹-采用ANSYS進行DDR4仿真。)

圖2、開發板原理圖中DDR部分

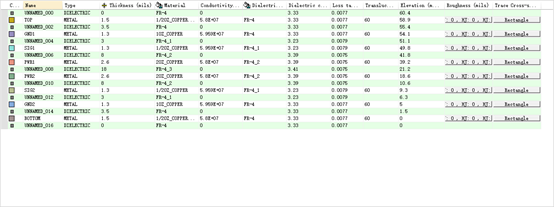

仿真疊層設置如圖3所示,確保PCB設置一致,Siwave和Sigrity均使用相同疊層設置。

圖3、PCB疊層設置

由于仿真中考慮了信號SSN效應,所以需要同時考慮PDN的影響,為了保持一致,器件參數統一按照下表進行設定。

| 模型參數 | 位號 | 容值 |

| GRM152D70E224ME19 |

C24,C25,C26,C27,C28C29,C30,C35,C36,C37,C38,C43,C44,C45,C46,C55,C56,C57,C62,C1646,C1647,C1648,C1649,C1651,C1652,C1653, C1654,C1655,C1656,C1657 |

2.2E-7 |

| GRM152R60J105ME15 | C68,C69 | 1E-6 |

| GRM155C71A225ME11 | C47,C48,C49,C50,C51,C52,C63,C64,C65,C66,C67,C70,C71,C72,C1645,C1650 | 2E-6 |

| GRM31CC80J226ME19 | C18,C19,C20,C39,C40,C41,C42,C133,C134 | 2.2E-5 |

同樣為了方便對比,Siwave和Sigrity內器件驅動和接收參數均按照下表設置。

| Mode | Parameter | Value |

| Read | DRAM Slew | PD60-ODT40-VOH30 |

| SOC | ODT-60Ohm | |

| Write | SOC Rout | 80Ohm |

| DRAM | ODT-40Ohm |

表2、器件驅動參數設置表

最后可以簡單介紹兩款軟件,以方便初學者做出適合自己的選擇。

1)、Siwave是ANSYS公司發布的一款軟件,包含在ANSYSElectronics Desktop(通常也稱為“電子桌面”)中,電子桌面主要進行電動力學方面的仿真,可以滿足從直流到太赫茲頻段的各類仿真需求。其中包含的Siwave、Circuit和HFSS 3D layout三個模塊主要用來處理PCB以及相應的電路-PCB協同仿真需求。從軟件功能上看,信號完整性仿真僅僅是ANSYS電子桌面眾多能力中的其中之一,除此之外還可以進行電力電子仿真、射頻和天線仿真、磁元件仿真以及多物理場的聯合仿真等。如果使用者有較為復雜多變的仿真需求,ANSYS是不錯的選擇。遺憾之處在于,ANSYS公司沒有一款Layout工具,這導致其處理PCB仿真需求時需要借助Cadence等其他EDA公司的軟件進行部分PCB的前處理工作,這一點在進行PCB的優化上是遠不如自帶Layout工具的仿真軟件方便的。

2)、Sigrity是Cadence公司旗下產品。除去高大上的芯片設計工具,我們通常用到的Cadence軟件包主要有Orcad和Allegro,以及Pspice和Sigrity。Orcad和Allegro功能大家都知道,主要是原理圖和Layout。Pspice為電路仿真工具。Sigrity為PCB仿真工具,內部包含了System SI,Power SI,Power DC等模塊,目的是為滿足PCB仿真中的信號和電源協同分析設計和仿真需求。SIgrity與SIwave在算法上非常相似,兩者均采用了包括FEM、矩量法和傳輸線法的混合算法。從這里可以看到,Sigrity背后的Cadence不能處理復雜的電磁場仿真需求,但其在Layout和CAD方面是權威。而且從學習成本上,Sigrity相對資料更多,更容易上手。

2、仿真流程對比介紹

在對DDR的仿真處理上,Siwave和Sigrity整體流程類似。Siwave采用自身進行PCB的S參數提取,然后匯入Circuit中搭建系統電路進行仿真。SIgrity則是通過Power SI進行PCB的S參數提取,然后在System SI中搭建系統電路進行仿真。

2.1、視圖上的差異

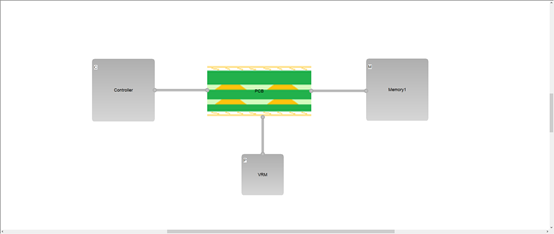

Siwave在匯入Circuit后,整體電路拓撲層次分明,關鍵信息幾乎全部體現在主視窗中。

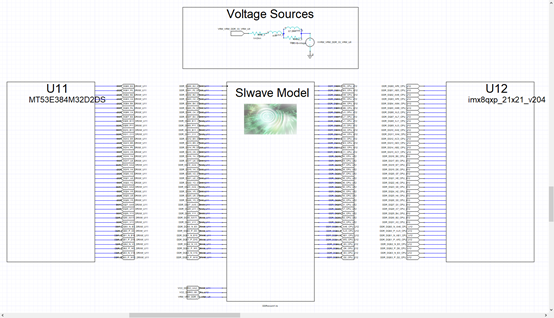

圖4、Circuit中搭建的DDR仿真拓撲

Sigrity的系統界面主窗口相比更為簡潔,用戶需要對電路進行編輯,需要通過雙擊相應的圖標來完成,更多的信息隱藏在二級界面中。

圖5、Sigrity中搭建的DDR仿真拓撲

2.2、仿真結果處理的差異

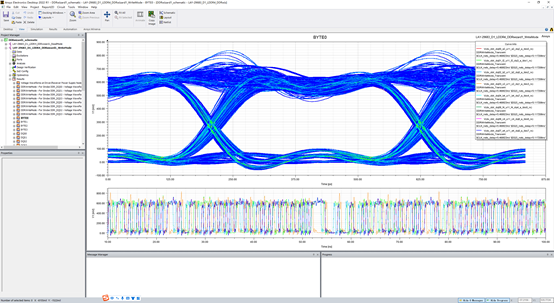

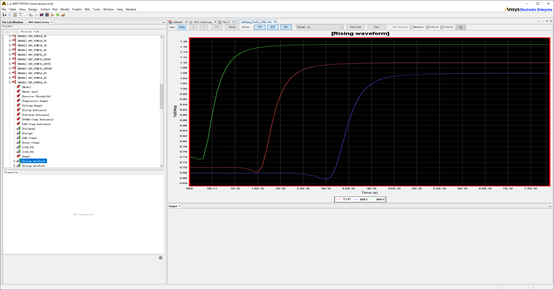

使用Siwave時,用戶需要自行調出仿真結果,并且在眼圖的導出中需要手動設置UI時長,且在對驅動參數、信號速率等重新編輯后,原始結果會被清除,若要保留則需要手動復制,總之整體的操作過程中手動的部分更多一些。

圖6、Circuit仿真結果界面

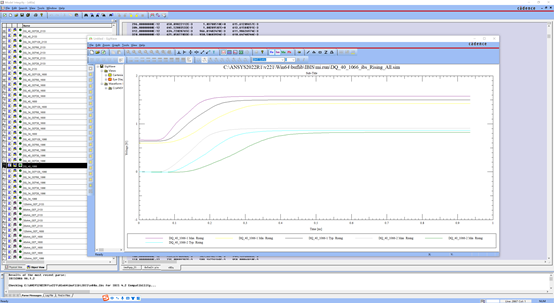

相反在使用Sigrity時,仿真結果是自動生成的,眼圖等常用結果的呈現也更為自動化,用戶在進行驅動參數、信號速率等重復編輯,軟件也能自動保存每次仿真的結果。即整個過程中自動的部分更多一些。

圖7、System SI仿真結果界面

2.3、預處理方面差異

Siwave因為整合度較高,充分發揮了ANSYS電子桌面的強大之處,因此在模型預處理方面更為全面,包括S參數的合規性檢查,IBIS模型的檢查、修復、重新編輯等。因此個人認為更為專業一些。

圖8、Siwave對S參數模型的處理

圖9、Siwave對IBIS模型的處理

圖10、Cadence自帶的IBIS模型工具

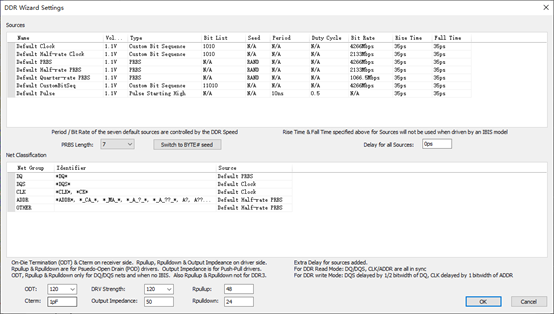

2.4、驅動碼型差異

Siwave和Sigrity在驅動碼型上存在一定差異。其中,Siwave默認為PRBS碼型,可設置每個網絡碼型由系統隨機生成。

圖11、Siwave中的碼型設置界面

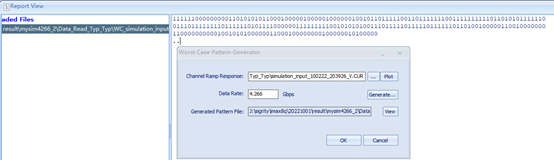

Sigrity在驅動碼型的設置上也類似,但多了一個通道檢測的功能,可以根據通道響應特性生成“worst case”的驅動碼型。這點主要考慮了PDN的SSN效應,根據Larry Smith(高通PI首席專家)的文章,系統在特定的碼型驅動下,可以被激發出導致系統崩潰的浪涌,并將這種現象定義為Rogue Wave。從這個角度來看,worst case是一種檢驗DDR系統魯棒性的較為便捷的方法。

圖12、Sigrity碼型生成工具

3、結果對比

設置信號速率為4.266Gbps,分別仿真得到結果。

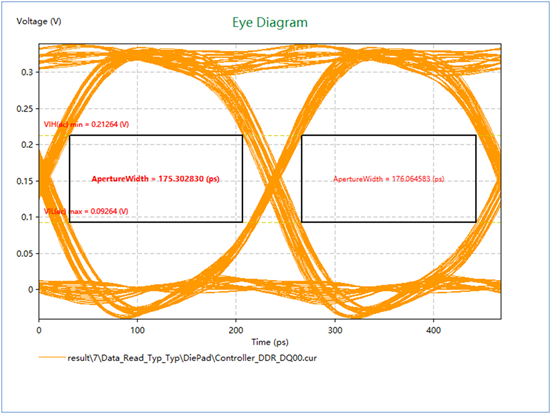

3.1、讀操作

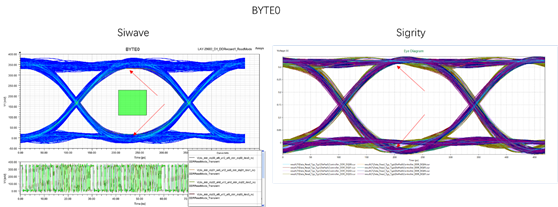

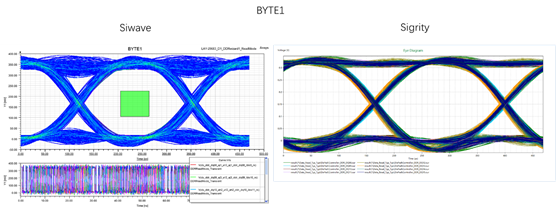

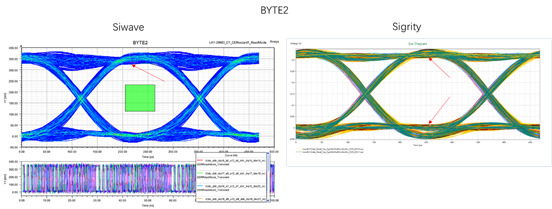

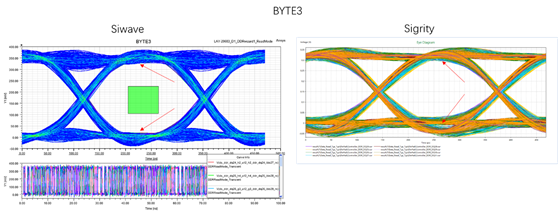

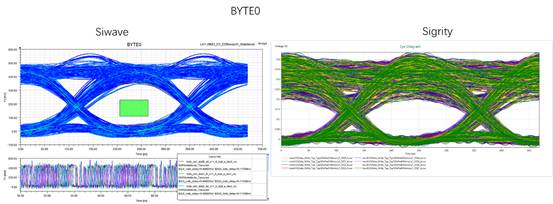

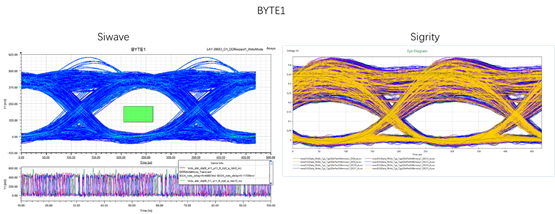

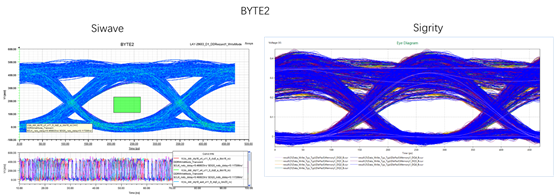

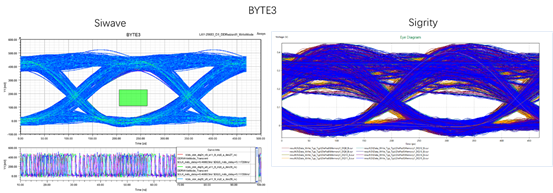

可以看到兩個工具在讀操作下的結果基本一致,波形細節存在一定的差異,比如Sigrity波形的眼高要略小于Siwave結果。個人猜測可能主要是兩個工具在處理IBIS模型數據上存在一定的差異。(為什么不是S參數結果的差異呢?原因在下文中。)

圖13、Byte0結果對比

圖14、Byte1結果對比

圖15、Byte2結果對比

圖16、Byte3結果對比

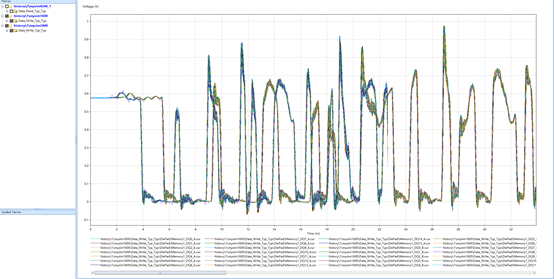

3.2、寫操作

在寫操作結果中,兩者出現了巨大的差異。Siwave取得的結果明顯優于Sigrity。Sigrity結果中高電平幅值一致性非常差,導致“眼皮”厚度明顯大于Siwave結果。

圖17、Byte0結果對比

圖18、Byte1結果對比

圖19、Byte2結果對比

圖20、Byte3結果對比

4、模型的處理

4.1、IBIS模型

按照Wei-hsing Huang(SPISim USA的首席顧問,后被ANSYS收購)的博客文章,IBIS模型的使用存在頻率上限,超出使用頻率上限,緩沖器將沒有足夠的時間來完成上升、下降或兩者間的轉換。這種情況會導致模擬過程中存在不連續、故障甚至不收斂的情況。我們將這種現象定義為Overclocking。

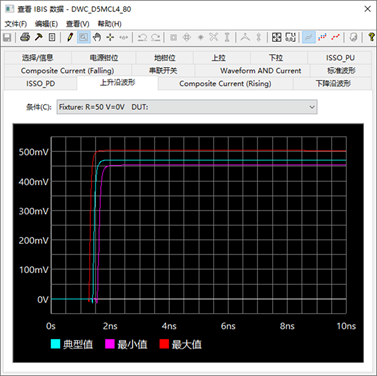

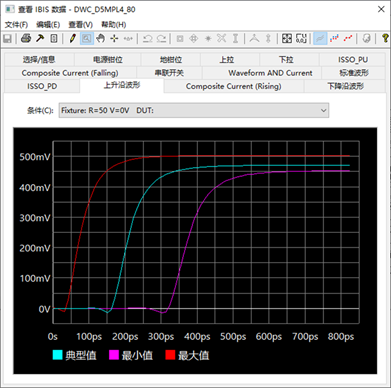

NXP官網提供的MCU模型便存在Overclocking情況,打開其DDR的驅動波形可以看到,其上升沿長度達到了10ns之久,已經嚴重超出4.266Gbps最小碼型寬度。

圖21、初始MCU模型上升沿波形

Siwave內部集成了IBIS模型預處理功能,可以最大化的對波形寬度部分進行裁剪,使其滿足更高頻率的要求。從下圖中可以看到,優化后的波形上升沿寬度降低到不到800ps。

圖22、優化后MCU模型上升沿波形

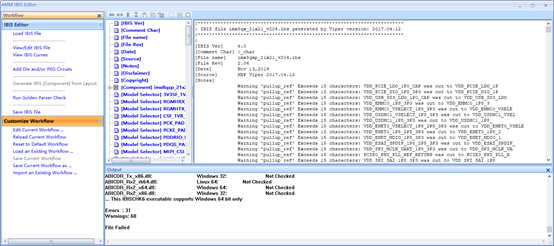

Sigrity中也包含了IBIS模型的檢查功能,會對合規性進行檢查。但僅限于檢查,并未發現進一步優化處理的部分。正因如此,兩者在寫模式下結果才會出現較大的差異。

圖23、Sigrity中的IBIS模型檢查功能

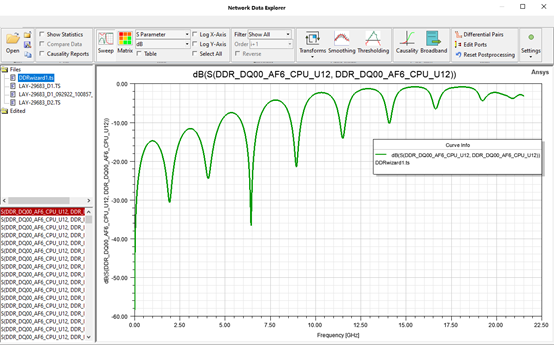

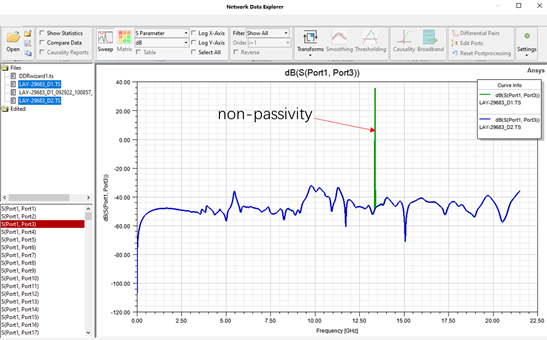

4.2、S參數模型

在Sigrity的使用中,發現其Power Si在生成S參數模型時存在不收斂的情況,將兩次仿真結果放在一起進行對比,可以看到其中一次存在明顯的Non-Passivity情況。筆者也不清楚為何會出現這種情況,希望了解的老師能夠解答這個疑問。

圖24、PowerSI兩次仿真得到S參數對比

5、報告生成

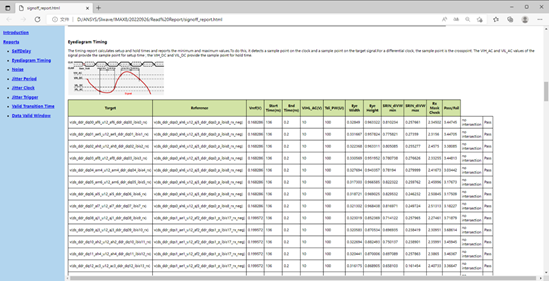

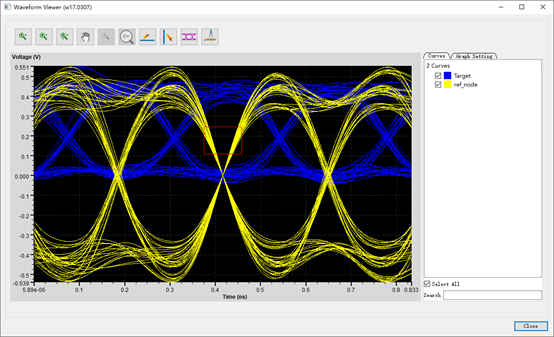

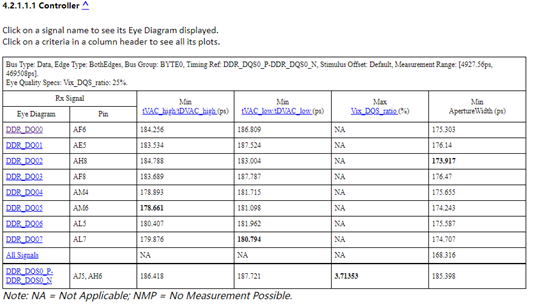

對于復雜的DDR仿真結果,查看JEDEC標準文檔逐個進行合規性檢查是一件繁瑣的事情。Siwave和Sigrity作為成熟的商業軟件,均具備完整的報告生成功能。其內置的報告生成功能極大的簡化了這部分工作,可以自動對仿真結果進行檢查,并且輸出合規性報告。

相比之下,Siwave的報告生成功能較為繁瑣,使用者需要去對結果信號重新定義,才能得到相應的仿真報告,同時,Siwave的仿真報告中缺乏如疊層信息、去耦電容信息、模型驅動設置等關鍵信息,且網頁格式的結果文檔中不能夠再次打開波形查看。

圖25、Siwave合規性報告(部分截圖)

圖26、Siwave合規性報告(部分截圖)

Sigrity的報告生成相對來講更為簡單便捷,用戶不需要重新對信號間關系進行重新定義,僅需要簡單的幾步操作即可得到完整包含信號波形的結果文件。這點相較于Siwave來講還是很人性化的。

圖27、Sigrity合規性報告(部分截圖)

圖28、Sigrity合規性報告(部分截圖)

6、總結

從簡單的橫向對比可以看到,主流商業SI仿真工具均可以完成大部分的仿真需求。但現階段下沒有一家可以做到盡善盡美的。若要在產品的研發過程中充分發揮SI的價值,使用者就需要克服軟件中存在的不足之處。

本文中使用的PCB文件和IBIS模型已經在網盤中共享給各位讀者(鏈接:https://pan.baidu.com/s/13_ojhpP0glnzss8cXx8a_w提取碼:b10s),歡迎大家下載學習,也希望有朋友能夠使用其它工具復現本文結果,對市面上的商業軟件進行一個橫向大比拼!

審核編輯:湯梓紅

-

信號完整性

+關注

關注

68文章

1410瀏覽量

95515 -

SIGRITY

+關注

關注

1文章

6瀏覽量

7741 -

SIwave

+關注

關注

0文章

3瀏覽量

9655

原文標題:SIwave與Sigrity在信號完整性方面的對比

文章出處:【微信號:EMC_EMI,微信公眾號:電磁兼容EMC】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

SIwave與Sigrity在信號完整性方面的對比

SIwave與Sigrity在信號完整性方面的對比

評論