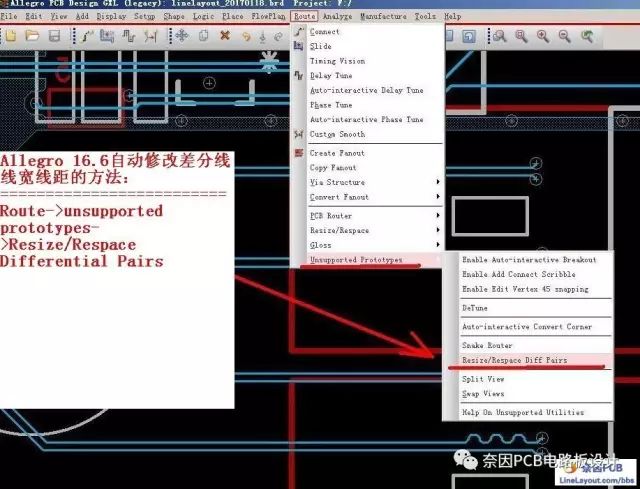

Allegro 16.6自動修改差分線線寬線距的方法:

Route->unsupported prototypes->Resize/Respace Differential Pairs

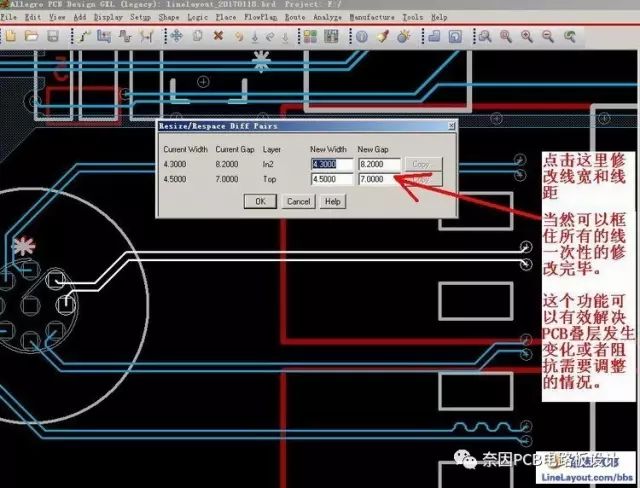

1.

2.

審核編輯:劉清

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

-

Allegro設(shè)計

+關(guān)注

關(guān)注

0文章

10瀏覽量

5609

原文標(biāo)題:Allegro 16.6自動修改差分線線寬線距的方法

文章出處:【微信號:pcbgood,微信公眾號:奈因PCB電路板設(shè)計】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

PCB設(shè)計中線寬、線距設(shè)置規(guī)則

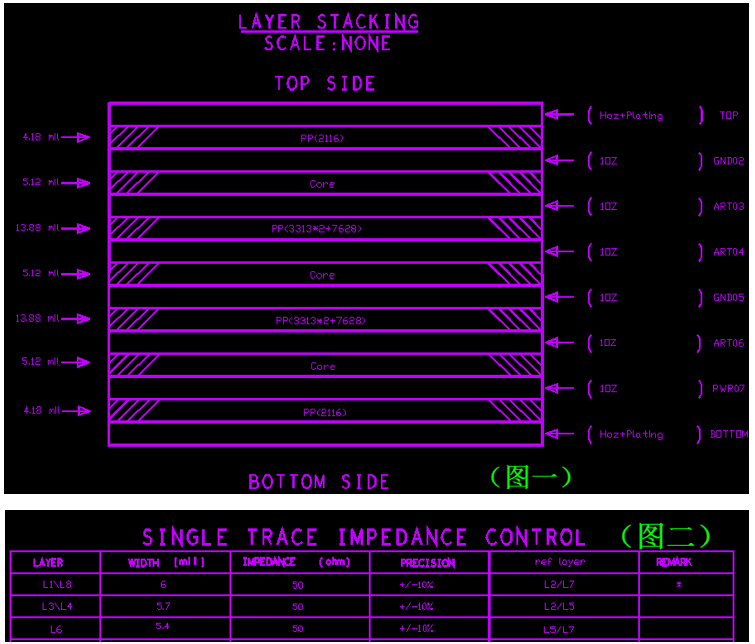

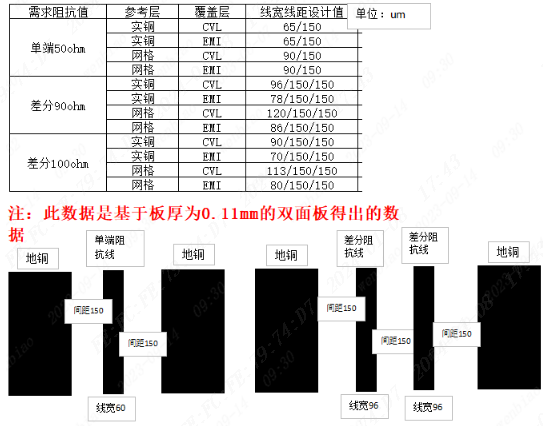

需要要做阻抗的信號線,應(yīng)該嚴(yán)格按照疊層計算出來的線寬、線距來設(shè)置。比如射頻信號(常規(guī)50R控制)、重要單端50R、差分90R、

發(fā)表于 10-14 09:27

?7499次閱讀

PCB設(shè)計軟件allegro16.6演示區(qū)域規(guī)則的設(shè)置

的特殊線寬、線距要求在某些區(qū)域中又不適于使用,這就需要進(jìn)行區(qū)域規(guī)則的設(shè)置。首先,同樣需要打開allegro16.6菜單欄選擇setup->constraints->constraint

發(fā)表于 12-28 10:45

allegro差分線的設(shè)置步驟

一般的,需要自己先提前計算好層疊,阻抗,計算好單端和差分的線寬,線距,計算之前,需要自己根據(jù)BGA間距,走線密度等,做一個預(yù)估,這樣,計算出

發(fā)表于 05-22 06:57

PCB設(shè)計的線寬和線距規(guī)則

應(yīng)該按照疊層計算出來的線寬、線距來設(shè)置。比如射頻信號(常規(guī)50R控制)、重要單端50R、差分90R、差分100R等信號

發(fā)表于 07-19 08:23

AD19:如何設(shè)置 差分線對與單端線之間的線間距?

有一組線:里面有多對差分線對,有多根單端線,差分線對的走線規(guī)則已經(jīng)設(shè)置了(線寬5MIL,

發(fā)表于 11-19 14:17

需要做阻抗的信號線時應(yīng)該怎樣計算線寬、線距規(guī)則?

1需要要做阻抗的信號線,應(yīng)該嚴(yán)格按照疊層計算出來的線寬、線距來設(shè)置。比如射頻信號(常規(guī)50R控制)、重要單端50R、差分90R、

發(fā)表于 09-08 11:20

?1.6w次閱讀

線寬、線距規(guī)則設(shè)置到底怎樣最合適?

線寬線距最小控制到 3.5/3.5mil,過孔選擇 8mil(0.2mm),這時候有部分PCB生產(chǎn)廠商生產(chǎn)不了,價格會更貴一點。線寬線

PCB設(shè)計如何設(shè)置時線寬、線距規(guī)則

一丶 需要要做阻抗的信號線,應(yīng)該嚴(yán)格按照疊層計算出來的線寬、線距來設(shè)置。比如射頻信號(常規(guī)50R控制)、重要單端50R、差分90R、

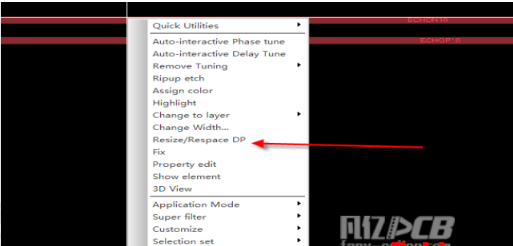

pcb設(shè)計:Allegro自動修改差分線寬方法

在pcb設(shè)計過程中,有時候因為阻抗的變化,我們需要更改已經(jīng)布好的走線,單根走線非常好更改,直接使用change命令修改線寬即可,對于差分信號,有線寬

怎樣去修改Allegro 16.6差分線線寬線距呢

怎樣去修改Allegro 16.6差分線線寬線距呢

評論