ME32 ADC 應用指南

1、概述

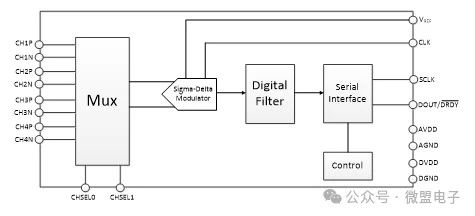

ME32 系列是內嵌 ARM Cortex M0 核的 32 位微控制器。該系列控制器由敏矽微電子有限公司自主開發,并具有自主知識產權。敏矽微電子的微控制器通用功能有高精度 ADC,UART 串口,SPI 接口,I2C 總線接口,看門狗定時器(WDT),通用計數器/定時器和馬達控制功能模塊。

ME32 系列 ADC 采用 SAR(電容式漸次逼近)設計,具有采樣轉換速度快,成本低特點。但 SRA ADC 在使用上與傳統的ADC 有一些差別,我們就此做一些討論(以下整理的資料來源于網上)。

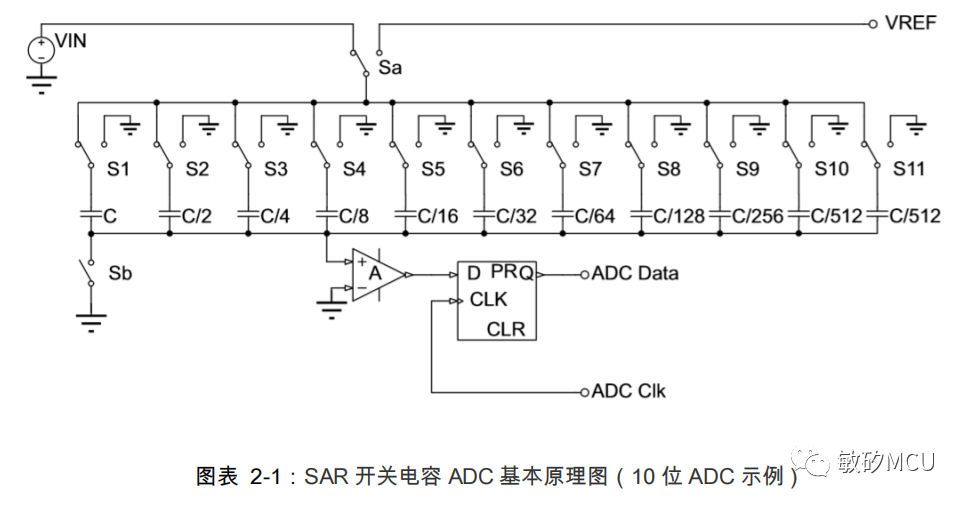

2、SAR ADC 原理

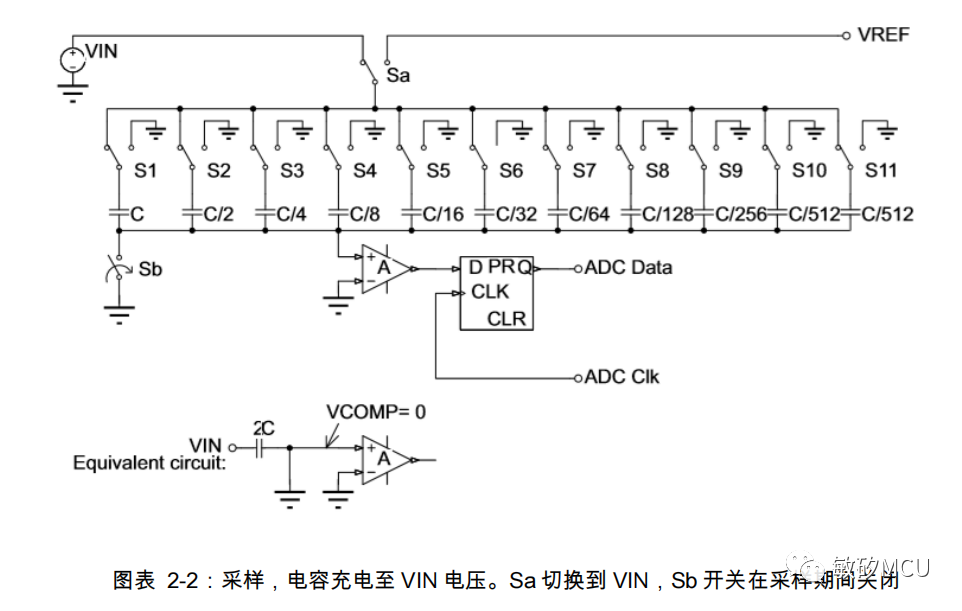

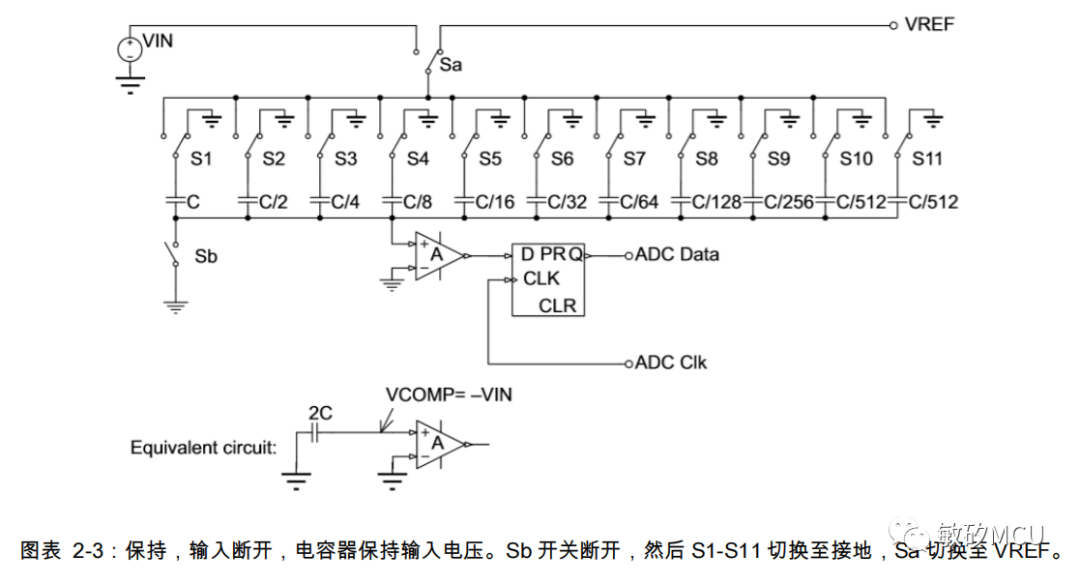

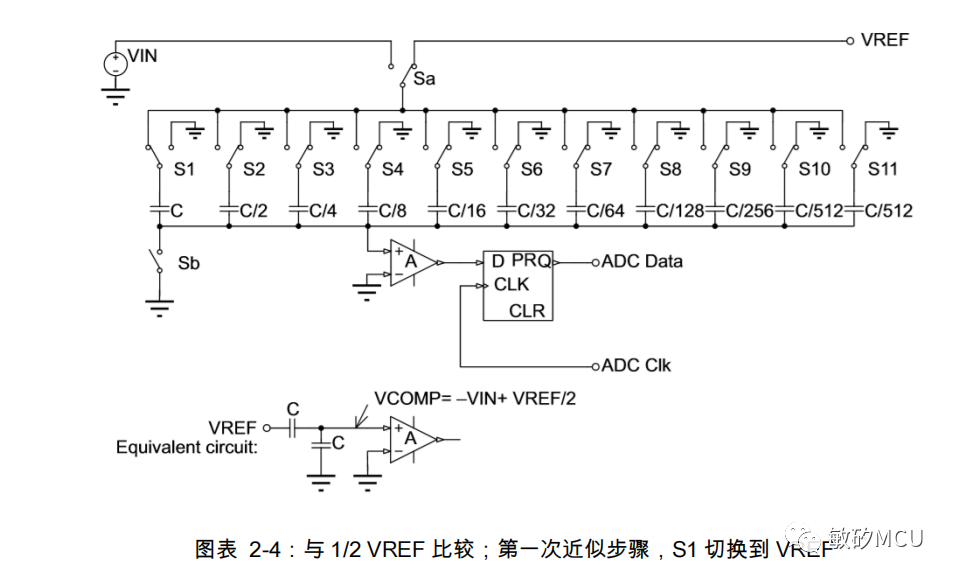

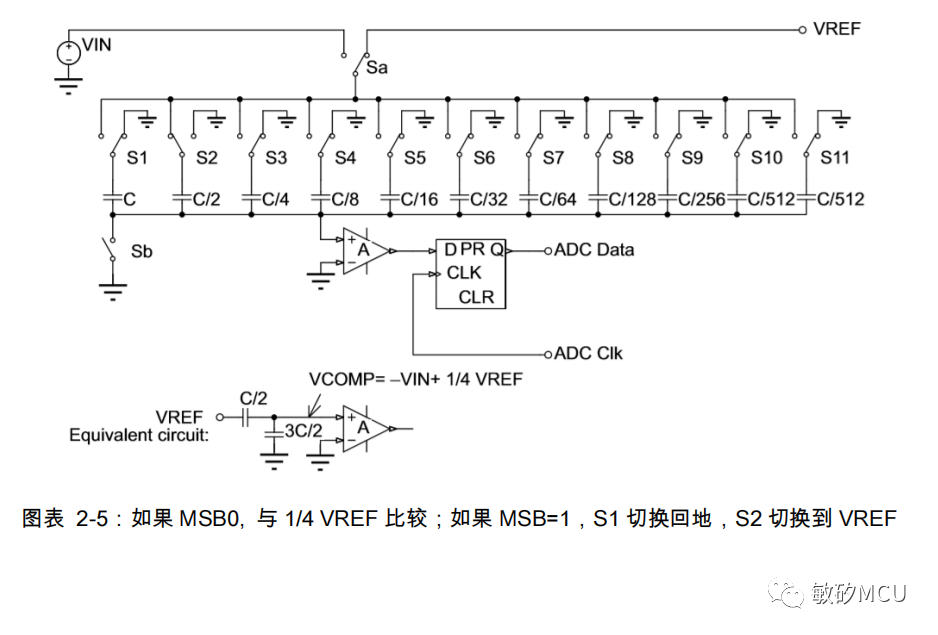

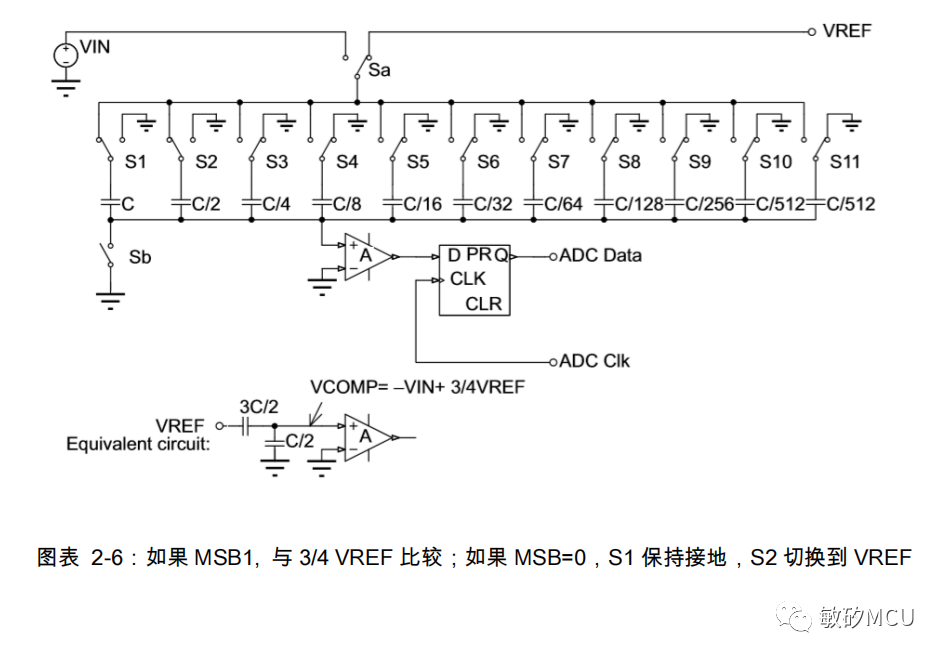

ME32 微控制器中嵌入的 ADC 使用 SAR(逐次逼近寄存器)原理,可以分以下步驟執行轉換。每個轉換步數等于 ADC 轉換器中的位數,而每一步都由 ADC 時鐘驅動,每個 ADC 時鐘輸出產生一位結果。所有 ADC 內部設計基于開關電容技術。下面給出的示例僅顯示了 ADC 近似逼近工作原理的第一步,但該過程將一直持續到達到 LSB 為止。

3、環境對 ADC 轉換結果的影響

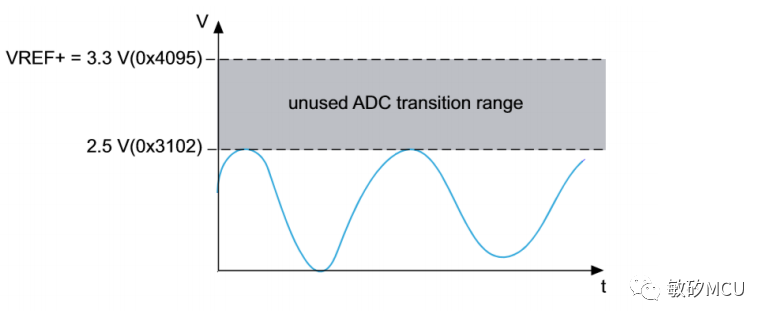

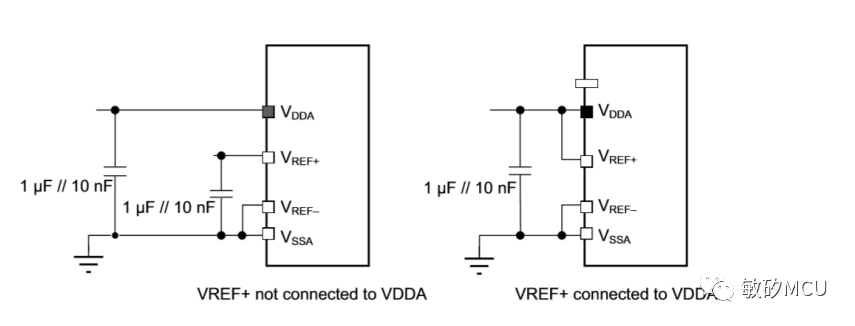

3.1 ADC 參考電壓噪聲 由于 ADC 輸出是模擬信號電壓和參考電壓之間的比率,模擬參考上的任何噪聲都會導致轉換后的數字值發生變化。部分封裝采用 VDDA 模擬電源作為參考電壓(VREF+),因此 VDDA 電源的質量對 ADC 誤差有影響。例如,當模擬基準電壓為 3.3 V (VREF+=VDDA)和 1 V 信號輸入時,轉換結果為: (1/3.3)×4095=0x4D9 然而,當模擬基準電壓為 40 mV 峰間紋波時,轉換值變為: (1/3.34)×4095=0x4CA(VREF+在其峰值處) Error=0x4D9–0x4CA=15lsb 因此我們可以得出,參考電壓噪聲對 ADC 轉換精度至關重要。而開關電源通常采用內部快速開關功率晶體管,這會在輸出中引入高頻噪聲,開關噪聲在 15 千赫至 1 兆赫之間。 3.2 參考電壓/供電電源 電源調節對于 ADC 精度非常重要,因為轉換結果是模擬輸入電壓與 VREF+值的比值。如果在連接到 VDDA 或 VREF+時,由于這些輸入上的負載及其輸出阻抗而導致電源輸出降低,則會在轉換結果中引入錯誤。 轉換結果=VAIN(2N-1)/VRef+,其中 N 是 ADC 的分辨率(在我們的情況下 N=12)。如果參考電壓改變,數字結果也會改變。例如:如果所使用的電源是 3.3 V 的參考電壓,而 VAIN=1 V,則數字輸出為:如果電源提供的電壓等于 3.292 V(在其輸出連接到 VREF+之后),則:電壓降引入的錯誤為:0x4DC–0x4D9=3 LSB 3.3 參考電壓解耦和阻抗 參考電壓源必須具有低輸出阻抗,以在各種負載條件下提供標稱電壓。輸出阻抗的電阻和電感部分都很重要。在模數轉換器轉換過程中,參考電壓是連接到開關電容網絡的。在連續近似(一個近似周期對應于一個 ADC 時鐘周期)期間,該網絡的電容器在很短的時間內從/到參考電壓充電/放電,因此參考電壓必須為電容器提供高電流峰值。在每個近似周期結束時,電容器上的電壓必須穩定(參考電壓的零電流)。因此,參考電壓必須具有非常低的輸出阻抗,包括低電感(以便在非常短的時間內提供高電流峰值)。寄生電感可以防止充電過程在接近周期結束時完全完成,或者在 LC 電路中出現振蕩(寄生電感與電容網絡一起)。在這種情況下,近似循環的結果是不準確的。所以參考電壓上正確的去耦電容器必須非常靠近管腳,提供低源阻抗。 3.4 外部參考電壓參數 如果使用外部參考電壓源(在 VREF+pin 上),則該外部參考電壓源有重要參數。必須考慮三種參考電壓規格:溫度漂移、電壓噪聲、長期穩定性。 3.5 模擬輸入信號噪聲 小但頻率高的信號變化在采樣時會導致較大的轉換誤差。這種噪音是由電機、發動機點火裝置、電源線等電氣設備產生的。它通過添加不需要的信號來影響源信號(如傳感器)。因此,ADC 轉換結果也會不準確。 3.6 ADC 動態范圍與最大輸入信號幅度不匹配 要獲得最大 ADC 轉換精度,ADC 動態范圍與要轉換信號的最大幅度匹配非常重要。假設要轉換的信號在 0 V 和 2.5 V 之間變化,且 VREF+等于 3.3 V。ADC 轉換的最大信號值為 3102(2.5 V),如圖所示。在這種情況下,有 993 個未使用的轉換(4095–3102=993)。這意味著轉換信號精度的損失。

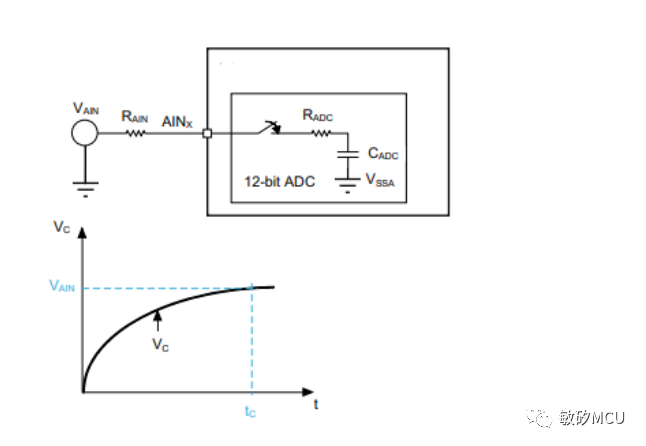

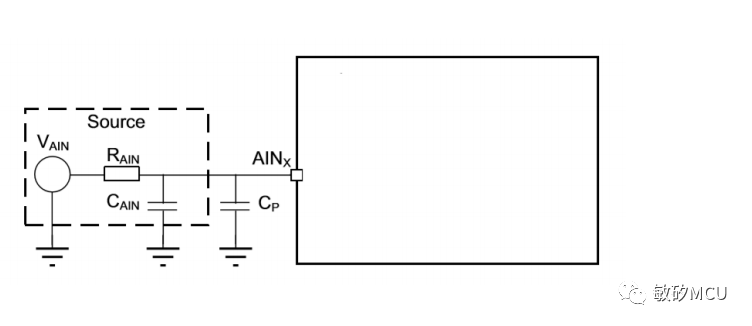

3.7 模擬信號源電阻的影響 模擬信號源的阻抗,或源和管腳之間的串聯電阻(RAIN),由于流入管腳的電流而引起電壓下降。內部采樣電容器(CADC)的充電由帶電阻的開關控制。隨著源電阻的增加(使用 RADC),保持電容器完全充電所需的時間增加。下圖顯示了模擬信號源電阻效應。

CADC 的有效充電受 RADC+RAIN 控制,充電時間常數為 tc=(RADC+RAIN)×CADC。如果采樣時間小于通過 RADC+RAIN(ts

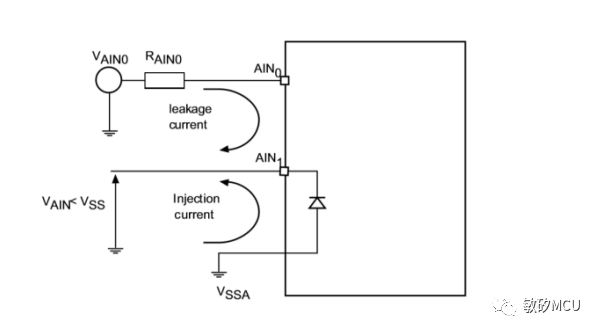

3.9 注入電流效應 任何模擬管腳(或緊密定位的數字輸入管腳)上的負注入電流可能會將泄漏電流引入 ADC 輸入。最壞的情況是相鄰的模擬信道。當 VAIN

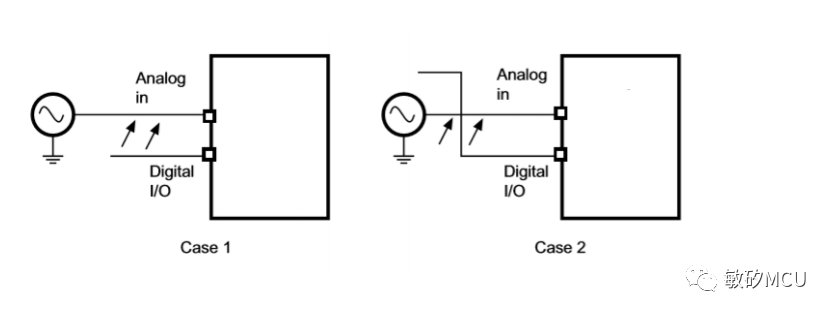

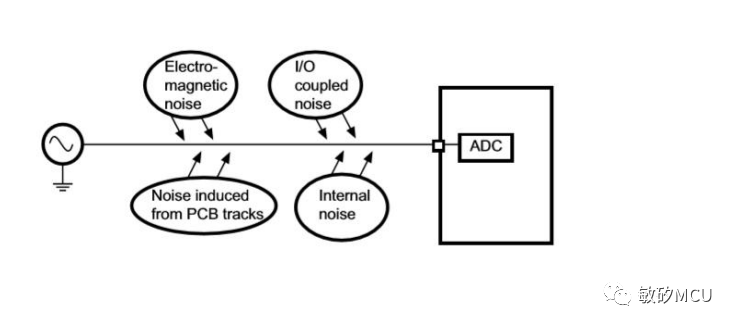

3.10 溫度影響 溫度對 ADC 的精度有很大的影響。主要導致兩大誤差:偏移誤差漂移和增益誤差漂移。這些錯誤可以在微控制器固件中進行補償 3.11 I/O 管腳串擾 由于 I/O 之間的電容耦合,切換 I/O 可能會在 ADC 的模擬輸入中產生一些噪聲。串擾可能是由相互靠近或相互交叉的 PCB 磁道引起的。內部交換數字信號和 I/O 引入高頻噪聲。切換 I/O 輸入輸出可能會導致電源中的電壓驟降,這是由電流浪涌引起的。穿過 PCB 上模擬輸入軌跡的數字軌跡可能會影響模擬信號。

3.12 電磁干擾引起的噪聲 來自鄰近電路的電磁輻射可能會在模擬信號中引入高頻噪聲,因為 PCB 軌跡可能像天線一樣工作。

4、硬件設計4.1 系統供電電源及 ADC 參考電源要求 雖然 MCU 可以工作從 2.2V~5.5V 寬電壓范圍,但電源的噪聲對 MCU 的正常工作還是至關重要的,好供電電源設計,系統便成功了一半。系統電源必須至少有一個 10uF 的穩壓電容和一個 0.1uF 的去藕電容,而且在 PCB 布板時去藕電容必須最大限度的靠近 MCU 的 VDD 管腳。 由于 ADC 使用 VREF+或 VDDA 作為模擬基準,并且數字值是模擬輸入信號與該電壓基準的比值,因此電源應具有良好的線路和負載調節。因此,VREF+必須在不同負載下保持穩定,接通電路的一部分增加負載,電流的增加決不能導致電壓降低。如果電壓在較寬的電流范圍內保持穩定,則該電源具有良好的負載調節能力。 例如,對于 LD1086D2M33 電壓調節器,當輸入電壓從 2.8 伏到 16.5 伏(Iload=10 毫安)變化時,線路調節率為 0.035%,當 Iload 從 0 到 1.5 安變化時,負載調節率為 0.2%(詳情請參閱 LD1086 系列數據表)。線路調節值越低,調節效果越好。同樣,負載調節值越低,電壓輸出的調節性和穩定性越好。也可以使用 VREF+的參考電壓,例如 LM236,它是 2.5v 的電壓參考二極管(有關更多詳細信息,請參閱 LM236 數據表)。 參考電壓源設計必須提供低輸出阻抗(靜態和動態)。寄生串聯電阻和電感必須最小化。參考電壓上的正確去耦電容器位于非常靠近管腳的位置,提供低參考電壓源阻抗。

4.2 ADC 信號源

4.2.1添加外部濾波器

添加外部 RC 濾波器可消除高頻。處理頻率成分高于感興趣頻率范圍的信號不需要昂貴的濾波器。在這種情況下,一個相對簡單的低通濾波器,其截止頻率 fC 剛好高于感興趣的頻率范圍,就足以限制噪聲和混疊。與最高關注頻率一致的采樣率就足夠了,通常是 fC 的 2 到 5 倍

4.2.2添加白噪聲或三角掃描以提高分辨率

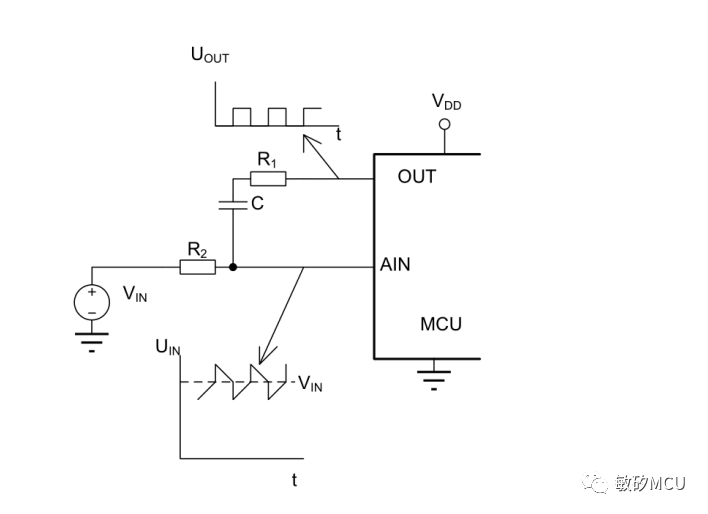

該方法將硬件技術和軟件技術相結合,提高了測量精度。從軟件的角度來看,該方法使用平均(過采樣),從硬件的角度來看,它使用信號修改/擴頻/抖動。在輸入信號有噪聲(為了能夠計算平均值,需要對信號進行一些改變)并且要求獲得信號的平均值的情況下,可以使用平均值。當輸入信號是一個非常穩定的無噪聲電壓時就會出現問題。在這種情況下,當測量輸入信號時,每個數據樣本是相同的。這是因為輸入信號電平介于兩個 ADC 字電平之間(例如,在 0x14A 和 0x14B 之間)。因此,無法更精確地確定輸入電壓電平(例如,如果電平接近 0x14A 或接近 0x14B 電平)。解決方案是向輸入信號添加噪聲或一些信號變化(具有均勻的信號分布,例如三角形掃描),輸入信號將其電平推過 1 位 ADC 電平(以便信號電平在 0x14A 以下和 0x14B以上變化)。這會導致 ADC 結果發生變化。將軟件平均應用于不同的 ADC 結果,產生原始輸入信號的平均值。作為一個例子,該方法可以通過使用與輸入信號耦合的三角形發生器來實現(白噪聲的產生更為復雜)。必須注意不要修改原始輸入信號的平均值(因此,必須使用電容耦合)。下圖是微控制器直接生成的準三角形源的一個非常簡單的實現

4.2.3小信號/弱信號考慮 對于小信號/弱信號(電阻分壓的電池電壓信號,NTC 信號),由于信號內阻大,最好的辦法是在 MCU 外部采用運放(OP),對信號進行增益和加強,從而一勞永逸解決信號的噪聲和易受干擾等問題。但出于成本的壓力和本身對測量精度要求不高,信號也變化緩慢,這時候可以加入一個 0.1u~1u 的電容,來消除 ADC 轉換時由于信號弱對測量精度的影響。 4.2.4電阻分壓信號源與參考電壓的一致性問題 對電阻分壓信號源(如 NTC)來講,ADC 輸入端口的電容和分壓電阻可能會導致與電源電壓的變化形成相位差,如果電源電壓正好是 ADC 的參考電壓,那么電源的波動就可能使參考電壓和信號不匹配,測量的結果也是不準確的。所以減小分壓電阻和 AD 端口的電容來縮小相位差是非常必要的。采用 NTC 時,建議分壓電阻不要超過 10K,AD 端口電容在 0.1u。 4.3 PCB 注意事項

VDDA 管腳的濾波電容要大于 0.1u,噪聲大時加大到 1u。

信號源遠離強電和大電流信號,避免與其他高頻信號并行行成串擾。

ADC 信號盡可能采用地和電源進行屏蔽。

5、軟件采樣

有如下幾個方法可以用來提高 ADC 轉換和采樣的精度:

平均樣本 – 平均會降低速度,但可以提高精度

數字濾波(直流值 50/60Hz 抑制)

– 設置了適當的采樣頻率(定時器觸發在這種情況下很有用)。

– 對采樣數據進行軟件后處理(例如 50 Hz 的梳狀濾波器噪聲及其諧波抑制)。

交流測量的快速傅里葉變換(FFT)

–這種方法允許在測量信號中顯示諧波部分。

–由于使用了更多的計算能力,因此速度較慢。

ADC 校準:偏移、增益、位重校準 ADC 校準減少內部 ADC 錯誤。然而,內部 ADC 結構必須知道。

最小化 CPU 內部和系統受控部分噪聲 必須設計應用程序 – 在 ADC 轉換過程中使用來自微控制器的最小干擾。

– 盡量減少采樣和轉換過程中的數字信號變化(數字沉默)。

5.1 平均法 平均是一種簡單的技術,在這里你可以對一個模擬輸入進行多次采樣,然后用軟件計算結果的平均值。這種技術有助于在模擬電壓不經常變化的情況下消除噪聲對模擬輸入的影響。必須對幾個讀數進行平均,這些讀數都對應于相同的模擬輸入電壓。確保在轉換完成的時間段內,模擬輸入保持在相同的電壓,否則您將累積對應于不同模擬輸入的數字值,并且您將引入錯誤。

另外拋棄一些明顯的因干擾而突變的結果(最低最高法則),對使用平均法也是非常有利的。

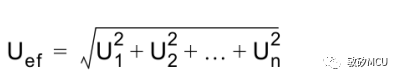

5.2 用于交流測量的 FFT 在某些特定情況下,應用程序需要知道帶有給定頻率。在這種情況下,交流信號的有效值也可以通過使用相對較慢的采樣速度(與測量的信號頻率相比)。 例如,當測量交流電源信號時(接近正弦且具有相對較低的諧波含量),足以選擇 32 次采樣頻率大于電源頻率(50 赫茲)。 在這種情況下,高達 15 階的諧波可以獲得。主信號中 15 次諧波的振幅很小(下一次階次諧波可以忽略不計)。電源信號的計算有效值為由于諧波的有效值被加到總交流諧波值為:

因此,如果第 15 次諧波振幅僅為第 1 次諧波(50 赫茲)的 1%(0.01),則其對總有效值的貢獻僅為 0.01%(因為上述公式得出:0.01 2=0.0001)。因此,該方法的原理是用已知頻率對交流信號進行采樣然后對每個測量周期的 FFT 進行后處理。因為每個測量信號周期的采樣點數量很小(例如 32 個點),則 FFT 處理所需的性能并不高(例如,僅 32 點 FFT)。該方法適用于低失真信號的交流測量。這個缺點是它需要精確的信號采樣:

測量信號的頻率必須已知,且 ADC 采樣頻率必須精確設置為測量頻率的 2N 倍增。

輸入信號頻率通過另一種方法測量。

通過對預分頻器和 MCU 主控器進行編程,調整 ADC 采樣頻率時鐘選擇(如果使用不準確的時鐘執行采樣,則插值可以用于在要求的點處獲取樣品)。

5.3 最小化內部 CPU 噪聲 當 CPU 工作時,它產生大量的內部和外部信號變化通過電容耦合傳輸到 ADC 外圍設備。這種干擾影響 ADC 精度(由于不同的微控制器操作而產生的不可預測的噪聲)。為了最小化 CPU(和其他外圍設備)對 ADC 的影響,有必要盡量減少采樣和轉換期間的數字信號變化(數字靜音)。這是使用以下方法之一完成(在采樣和轉換期間應用):

最小化 I/O 管腳更改

最小化內部 CPU 更改(CPU 停止、等待模式)

為不必要的外圍設備(計時器、通信……)停止時鐘

選擇系統相對安靜的時候進行采樣

審核編輯 :李倩

-

cpu

+關注

關注

68文章

10889瀏覽量

212389 -

adc

+關注

關注

98文章

6524瀏覽量

545206

原文標題:敏矽微 ME32 ADC實用指南

文章出處:【微信號:mcugeek,微信公眾號:MCU開發加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

EE-380:ADSP-CM40x電路板設計指南,實現最佳ADC性能

【敏矽微ME32G070開發板免費體驗】+ADC測試與LED點亮

【敏矽微ME32G070開發板免費體驗】串口通信、WS2812和PWM 呼吸燈、ADC 讀取

ADC12J2700EVM和ADC12J1600EVM用戶指南

adc參數解析及選擇指南

24位高精度ADC ME9603產品特點

ME32 ADC應用指南

ME32 ADC應用指南

評論