隨著晶體管尺寸的不斷縮小,為保證柵控能力,需要維持足夠的柵電容,因此要求柵氧厚度繼續減薄。然而,當柵氧物理厚度減薄到低于 1.5nm時,由于直接隧道效應指數級增加,器件漏電隨之大幅增加,從而導致器件無法實際工作。通過將相對介電常數(Relative Dielectrie Constant) 遠大于 SiO2(K大約3.9)的高K柵介質材料導入集成電路工藝,如HfO2(相對介電常數為 24~40),可以在保證等效柵氧厚度(Equivalent Oxide Thickness, EOT)持續縮小的前提下,使柵介質的物理厚度相對較大,以抑制柵泄漏電流。然后用TaN、TiN 、TiAI、W 等金屬合金或化合物疊層結構取代多晶硅柵,金屬疊層具有功函數調節和降低電阻率等作用,可避免多晶硅柵的耗盡效應,同時保證高k柵介質材料與金屬柵有較好的接觸效果。

目前,高K柵介質與金屬柵極技術已廣泛應用于 28mmn 以下高性能產品的制造,它在相同功耗情況下可以使集成電路的性能大幅度提高,泄漏電流大幅下降。高K金屬柵的應用經歷了較長的探索過程:在很長的時間里,晶體管的柵氧化層都是采用高溫干法或濕法熱氧化硅形成氧化層;后來為了提高 氧化層的介電常數,在氧化過程中摻入N元素形成 SiON柵介質層;隨著柵多晶硅厚度的降低,不僅導致電阻變大,還列起器件延遲和柵耗盡效應。在此背景下,在28nm這個工藝節點,工業界大多開始使用 HKMG 作為超大規模集成電路的標準工藝,雖然性能得到大幅提升,但也大大增加了工藝復雜度。

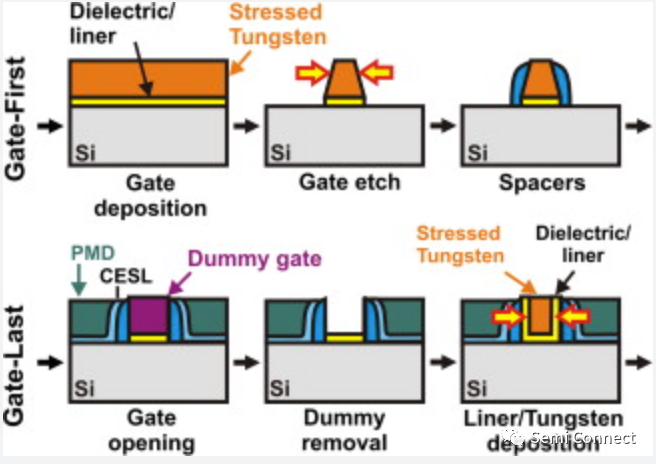

由于HKMG與 Poly/SiO2的 MOSFET結構有很大的不同,導致整個器件的工藝條件發生巨大變化,而且大量的 IP 核需要重新設計。 在最初的工藝開發階段,業內存在兩種制作HKMG 結構晶體管的工藝技術路線,分別是 Gate-Fiest(先柵極)工藝和 Gate-Last(后柵極)工藝。 Gate-First 工藝相對簡單,但是 p-MOS 閾值電壓很難控制;而 Gate-Last 工藝比較復雜,但它可以有效地調節柵極材料的功函數值,方便調節閾值電壓,還可以在p-MOS 的溝道實現改善溝道載流子遷移率的硅應變力。在同時兼顧高性能與低功耗的情況下(如手機應用處理器和基帶芯片等),Gate-Last 工藝逐漸取得優勢,是目前大規模生產中的主流工藝。

審核編輯 :李倩

-

晶體管

+關注

關注

77文章

9705瀏覽量

138468 -

介電常數

+關注

關注

1文章

108瀏覽量

18476

原文標題:高K金屬柵工藝(HKMG)

文章出處:【微信號:Semi Connect,微信公眾號:Semi Connect】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

激光焊接技術在焊接鎳鈦金屬的工藝應用

折疊共源共柵放大器的優缺點

柵介質層的發展和挑戰

PMOS工藝制程技術簡介

通過工藝建模進行后段制程金屬方案分析

MOSFET的柵源振蕩究竟是怎么來的?柵源振蕩的危害什么?如何抑制

高k金屬柵(HKMG)工藝詳解

高K金屬柵工藝(HKMG)

高K金屬柵工藝(HKMG)

評論