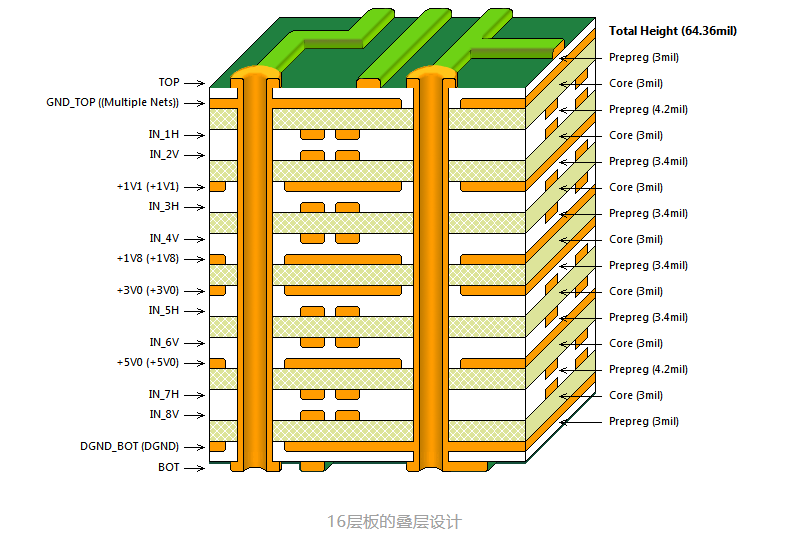

大家在畫多層PCB的時候都要進(jìn)行層疊的設(shè)置,其中層數(shù)越多的板子層疊方案也越多,很多人對多層PCB的層疊不夠了解,通常一個好的疊層方案可以降低板子產(chǎn)生的干擾,我們的層疊結(jié)構(gòu)是影響PCB板EMC性能的重要因素,下面我們以四層板和六層板為例介紹一下他們的層疊方案,讓我們從中選出最優(yōu)的層疊結(jié)構(gòu)。

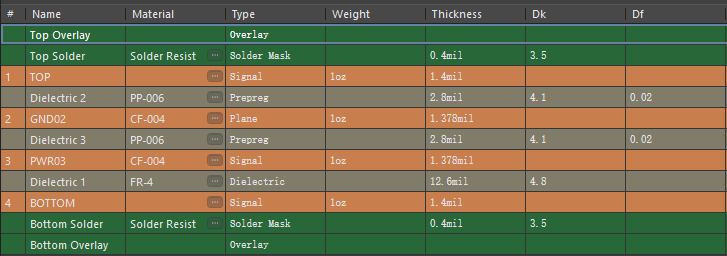

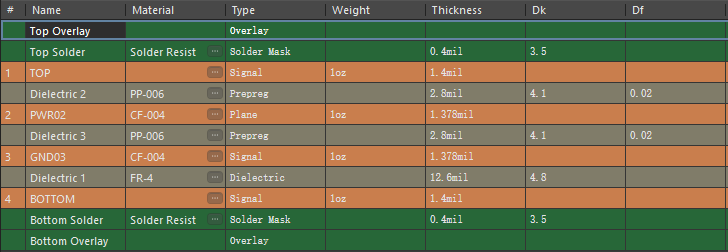

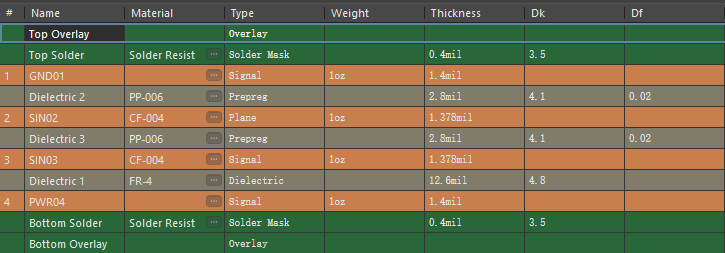

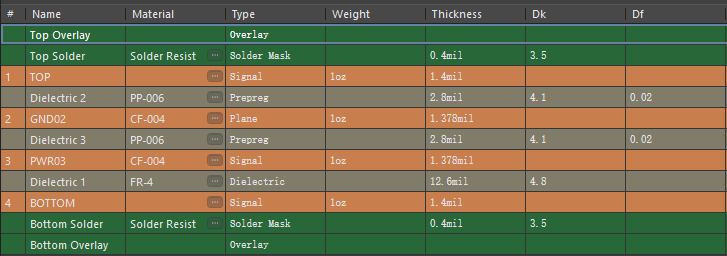

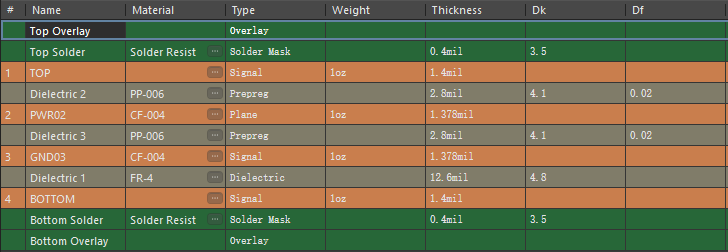

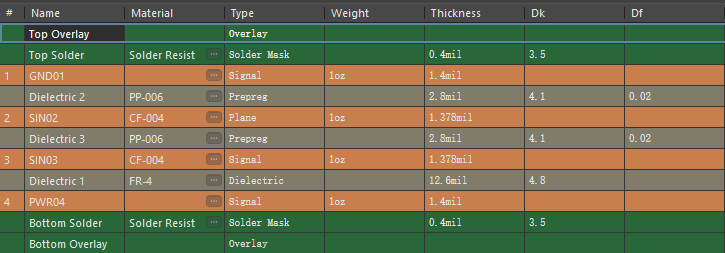

其中四層板的層疊結(jié)構(gòu)有如下三種:?

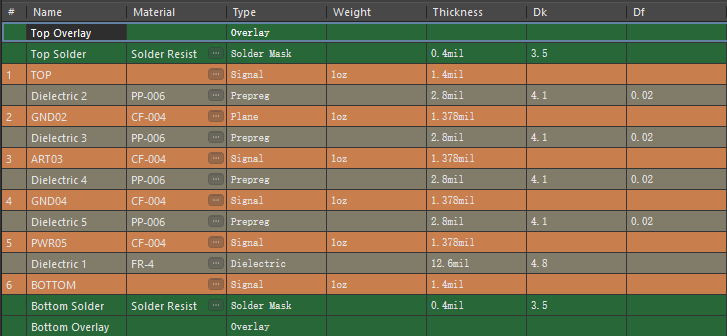

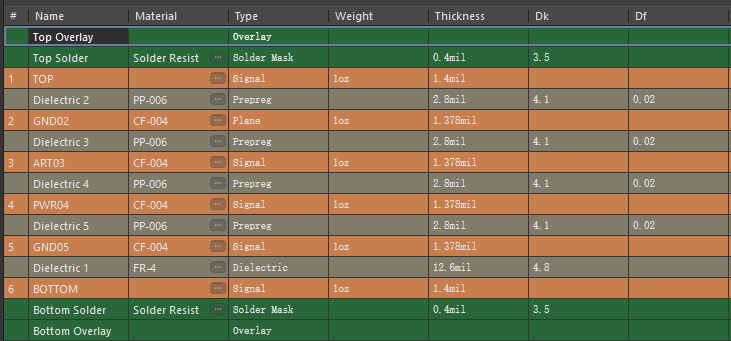

我們首先分析一下第一種和第二種疊層,這兩個疊層的區(qū)別時第二層和第三層相反,這兩個也是四層板用的比較多的疊層方案,這兩種疊層方案都是可行的,只是需要根據(jù)我們板子的實際情況進(jìn)行選取,通常在四層板設(shè)計的時候我們主要看器件主要是放置在頂層還是底層,我們的GND層主要是靠近器件層放置,這樣可以為器件提供完整的地平面從而也能屏蔽干擾等,我們的走線也盡量走在靠近底層的布線層當(dāng)中,這樣可以保證信號的穩(wěn)定性,也可以避免跨分割的情況產(chǎn)生,這就是這兩種疊層方案的區(qū)別。接下來我們看一下第三種層疊方案,這個層疊方案是把層和電源分布在第一層和第四層,如果是兩層板的話我們是需要在頂?shù)讓犹幚淼粑覀兊男盘柧€和地以及電源的,但是我們這是四層板,如果這樣疊層就沒有四層板的優(yōu)勢了,而且信號質(zhì)量也不太好,二三層是走線層,首先我們要知道的是我們的器件需要放置在頂?shù)讓拥模绻秧數(shù)讓臃峙錇榈睾碗娫吹脑捨覀兙筒荒鼙WC地平面的完整性了,電源也是如此,這樣第二層第三層的走線很有可能沒有完整的參考平面,此層疊方案的干擾屏蔽性也是較差的,通常我們畫完板子之后都是需要在頂?shù)讓愉伾险娴牡劂~皮,這個層疊方案把第一層作為地層實在是有點多余,所以這個層疊對于正常的四層板PCB設(shè)計來說都不會選取的。上面就是四層板的常見疊層方案,我們可以根據(jù)板子的實際情況對第一種和第二層疊層做一個選取,下面我們介紹一下常見六層板的疊層.

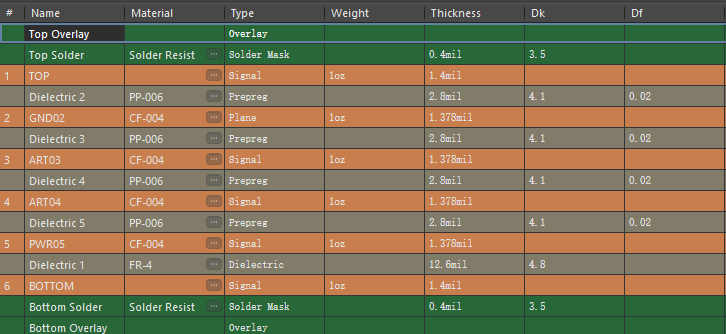

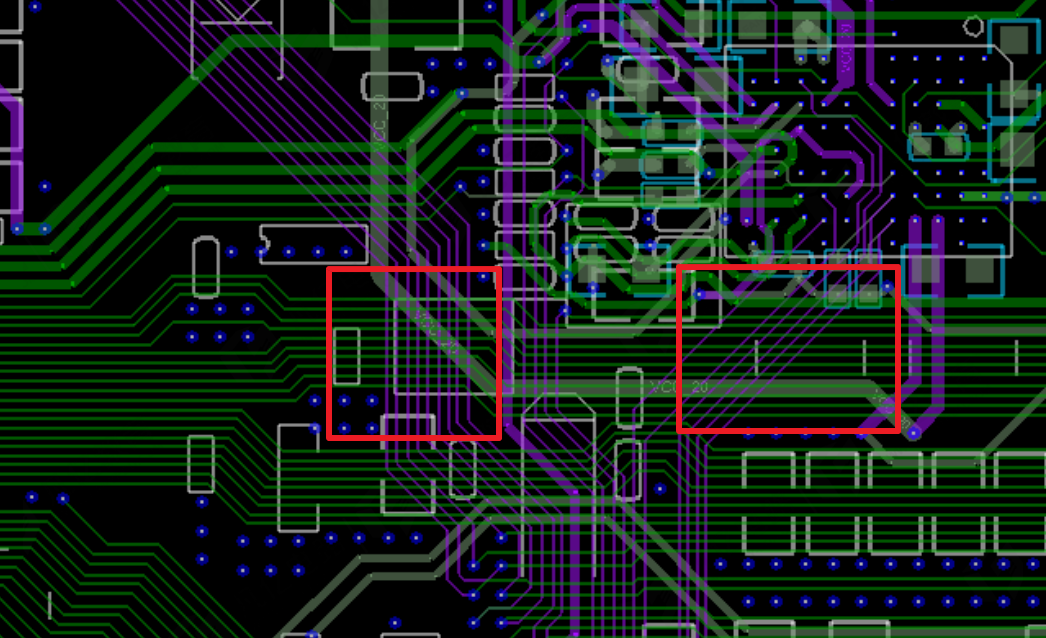

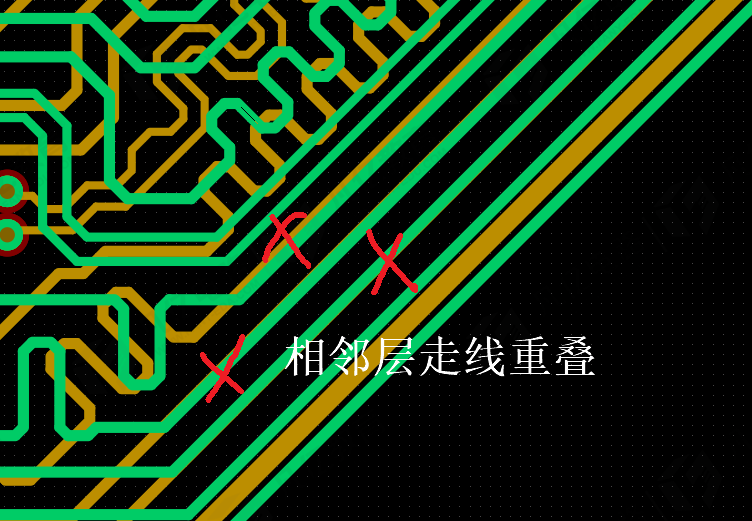

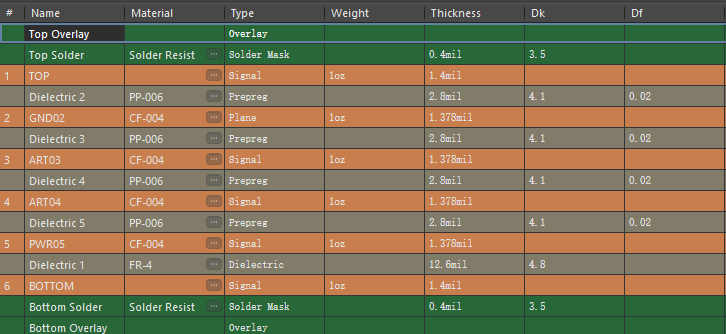

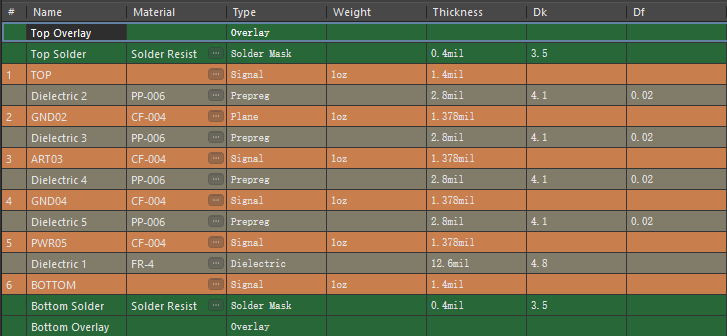

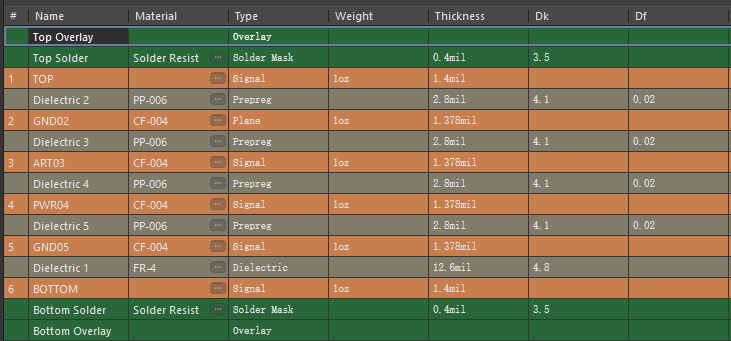

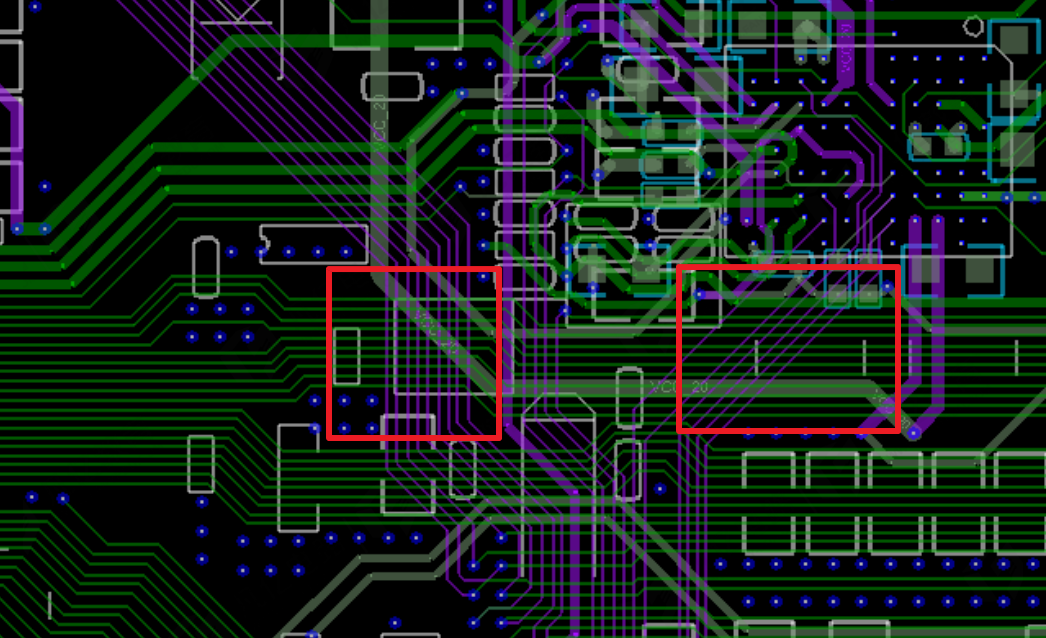

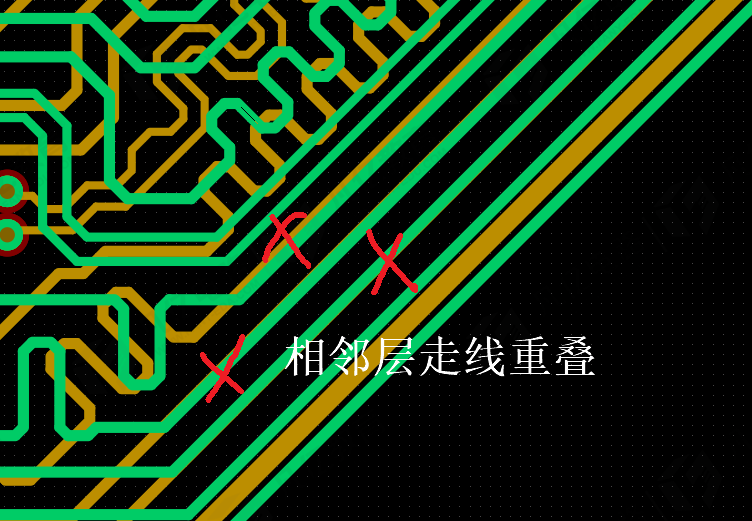

第一種層疊方案內(nèi)部有兩個布線層可以降低我們的布線難度,但是用于第三層和第四層是相鄰布線層,這樣容易產(chǎn)生串?dāng)_,所以我們在采用這一種層疊方案的時候要特別注意相鄰層要采用垂直布線,避免平行走線。(如下圖所示)。

第二種層疊方案,第三層為信號層,其相鄰層都是GND,可以和其他層做有效的隔離,也不容易產(chǎn)生串?dāng)_,但是只有一個內(nèi)布線層的情況對于我們布線的難度可能會有所增加,所以在布線時需要規(guī)劃好我們的布線通道和路徑,確保能處理完全部信號線,然后由于前三層只有一個內(nèi)電層,后三層有兩個內(nèi)電層,這樣我們的內(nèi)電層不對稱,就會產(chǎn)生翹曲的風(fēng)險。第三種層疊方案和第二層層疊方案相比只是第四層和第五層互換了一下,這個疊層也能為我們的信號做有效的隔離,但是此層疊方案也是存在內(nèi)電層不對層的情況,所以也會有翹曲的情況產(chǎn)生,這個層疊方案,有相鄰兩個地層,信號也會更好一些,在設(shè)計的時候也會有很多的客戶要求為需要控阻抗的線提供兩個參考平面,更嚴(yán)格的還需要參考兩個地平面,這就需要保證參考平面的完整性,一般地平面相對來說都是完整的,電源平面通常需要走不同的電源信號,如果需要參考兩個相鄰平面的話就會有跨分割的風(fēng)險產(chǎn)生。通過上面的介紹我們發(fā)現(xiàn)每個層疊方案都有利有弊,我們需要根據(jù)板子的實際情況來選取合適的疊層,在實際的設(shè)計當(dāng)中,我們發(fā)現(xiàn)第一種疊層方案使用的頻率是特別高的,因為對于普通的公司也需要考慮成本,能不加層就不加層,加層所增加的成本時非常高的,通常在大批量生產(chǎn)的時候尤為明顯,在我們線不是特別多的情況下我們優(yōu)先選取第二種和第三種層疊方案,對于信號質(zhì)量來說也是有保障的,對于軍工類的公司來說,成本就是次要的,他們首先考慮的是板子的信號質(zhì)量,在保證信號質(zhì)量的前提下再考慮成本。以上就是四層板和六層板的層疊方案,我們雖然只介紹了四層板個六層板的疊層,但是對于更高層數(shù)的PCB疊層我們也可以這樣分析一下,結(jié)合板子密度和結(jié)構(gòu)確定層數(shù),再根據(jù)層數(shù)選取一個合適的層疊方案。投稿/招聘/廣告/課程合作/資源置換請加微信:13237418207掃碼添加客服微信,備注“入群”拉您進(jìn)凡億教育官方專屬技術(shù)微信群,與眾位電子技術(shù)大神一起交流技術(shù)問題及心得~

點擊“閱讀原文”查看更多精彩文章

原文標(biāo)題:PCB設(shè)計時如何選擇合適的疊層方案

文章出處:【微信公眾號:凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

聲明:本文內(nèi)容及配圖由入駐作者撰寫或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問題,請聯(lián)系本站處理。

舉報投訴

原文標(biāo)題:PCB設(shè)計時如何選擇合適的疊層方案

文章出處:【微信號:FANYPCB,微信公眾號:凡億PCB】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

相關(guān)推薦

精密ADC ADS1263在PCB設(shè)計時,芯片底部需要鋪銅接地嗎?

發(fā)表于 11-28 08:33

如何根據(jù)貼片疊層電感參數(shù)進(jìn)行選型 gujing 編輯:谷景電子 對于大部分電子設(shè)備來說,貼片疊層電感的選擇是一個特別重要的部分,它直接影響到

![的頭像]() 發(fā)表于

發(fā)表于 10-18 19:14

?205次閱讀

OPA29U作為電荷放大器,在PCB設(shè)計時如何設(shè)計保護(hù)環(huán),如果正想輸入端不接地而是接在一個2.5V上是否可以,這種情況下如何設(shè)計保護(hù)環(huán)?

發(fā)表于 09-26 06:41

一站式PCBA智造廠家今天為大家講講pcb疊層設(shè)計為偶數(shù)層的原因有哪些?PCB疊

![的頭像]() 發(fā)表于

發(fā)表于 07-03 09:36

?560次閱讀

Allegro環(huán)境介紹Allegro環(huán)境設(shè)定 焊盤制作 元件封裝制作 電路板創(chuàng)建PCB疊層設(shè)置和網(wǎng)表導(dǎo)入 約束規(guī)則管理布局 布線 覆銅PCB設(shè)計后處理

發(fā)表于 07-02 17:22

?0次下載

對于信號層,通常每個信號層都與內(nèi)電層直接相鄰,與其他信號層有有效的隔離,以減小串?dāng)_。在設(shè)計過程中,可以考慮多層參考地平面,以增強(qiáng)電磁吸收能力。

![的頭像]() 發(fā)表于

發(fā)表于 04-10 16:02

?2450次閱讀

的要求。 ? 什么是PCB扇孔? PCB扇孔:PCB設(shè)計中的一個術(shù)語,這個是一個動作,通俗的理解就是拉線打孔。 PCB設(shè)計中對PCB扇孔的要

![的頭像]() 發(fā)表于

發(fā)表于 04-08 09:19

?1106次閱讀

合適的PCB尺寸和層數(shù):根據(jù)電源模塊的尺寸和功能需求,選擇合適的PCB尺寸和層數(shù)。注意保持足夠的空間來布置元件和散熱器。 DC電源模塊的

![的頭像]() 發(fā)表于

發(fā)表于 03-05 14:30

?1289次閱讀

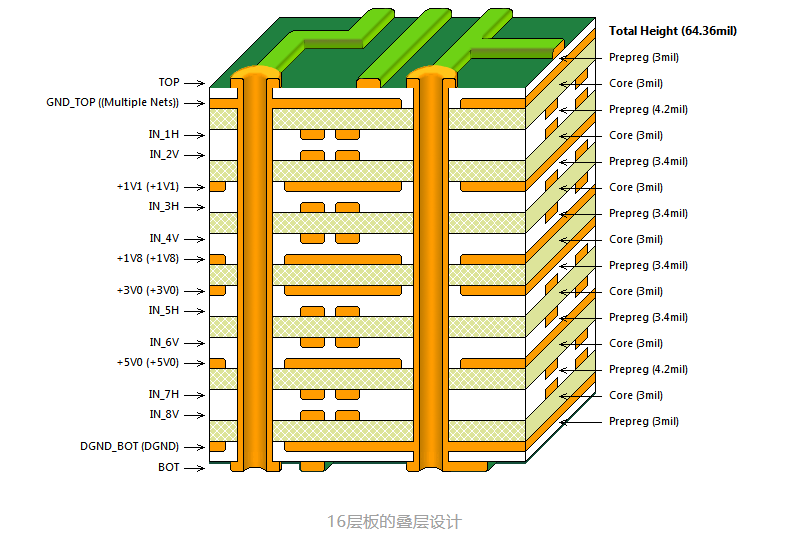

1.PCB疊層結(jié)構(gòu)與阻抗計算1.1.Core和PPPCB由Core和Prepreg(半固化片)組成。Core是覆銅板(通常是FR4—玻璃纖維&環(huán)氧基樹脂),Core的上下表面之間填充的是固態(tài)

![的頭像]() 發(fā)表于

發(fā)表于 01-25 17:15

?1.2w次閱讀

良好的PCB疊層設(shè)計能夠為高速信號回流提供完整的路徑,縮小信號環(huán)路面積,降低信號耦合靜電放電噪聲干擾的能力。良好的PCB疊

發(fā)表于 01-19 10:00

?585次閱讀

一站式PCBA智造廠家今天為大家講講PCB板設(shè)計時,鋪銅有什么技巧和要點?高速PCB設(shè)計當(dāng)中鋪銅處理方法。在高速PCB設(shè)計當(dāng)中,鋪銅處理方法是非常重要的一環(huán)。因為高速

![的頭像]() 發(fā)表于

發(fā)表于 01-16 09:12

?1179次閱讀

對于兩層板來說,由于板層數(shù)量少,已經(jīng)不存在疊層的問題。控制EMI輻射主要從布線和布局來考慮;單層板和雙層板的電磁兼容問題越來越突出。造成這種現(xiàn)象的主要原因就是因信號回路面積過大,不僅產(chǎn)生了較強(qiáng)的電磁輻射,而且使電路對外界干擾敏感

發(fā)表于 01-03 15:06

?375次閱讀

如果主元件面設(shè)計在BOTTOM層或關(guān)鍵信號線在BOTTOM層的話,則第三層需排在一個完整地平面。在層厚設(shè)置時,地平面層和電源平面層之間的芯板厚度同樣不宜過厚。

發(fā)表于 01-03 15:04

?961次閱讀

LTM4644和LTM4618在做PCB設(shè)計時支持遠(yuǎn)端反饋嗎?也即是否支持remote sensing?

如下面的這種示意圖

發(fā)表于 01-03 07:52

今天畫了幾張多層PCB電路板內(nèi)部結(jié)構(gòu)圖,用立體圖形展示各種疊層結(jié)構(gòu)的PCB圖內(nèi)部架構(gòu)。

發(fā)表于 01-02 10:10

?906次閱讀

PCB設(shè)計時如何選擇合適的疊層方案

PCB設(shè)計時如何選擇合適的疊層方案

評論