簡介

3DIC Compiler具有強大的Bump Planning功能。它可在系統設計初期階段沒有bump library cells的情況下,通過定義pseudo bump region patterns、創建bump regions以及填充pseudo bumps、創建Bumps的連接關系、為不同net的Bumps著色等操作,快速實現bump原型創建以及復雜bump規劃設計。

本視頻將展示在沒有bump library cells的情況下,3DIC Compiler 如何在GUI界面使用“pseudo” bumps 快速實現Bump Planning,流程包括:

定義bump region patterns

創建bump regions以及填充pseudo bumps

快速assign nets到對應的Bumps

為不同net的Bumps著色

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

原文標題:【芯和設計訣竅視頻】如何使用3DIC Compiler實現Bump Planning

文章出處:【微信號:Xpeedic,微信公眾號:Xpeedic】歡迎添加關注!文章轉載請注明出處。

相關推薦

近日,芯華章正式推出了其新一代高性能FPGA原型驗證系統——HuaPro P3。這款系統集成了最新一代的可編程SoC芯片,并配備了芯華章自主研發的HPE Compiler工具鏈,為用戶

![的頭像]() 發表于

發表于 12-11 09:52

?235次閱讀

芯和半導體將于11月5-6日參加在深圳福田會展中心7號館舉辦的國際集成電路展覽會暨研討會(IIC Shenzhen 2024),并在DesignCon專區中展示其3DIC Chiplet先進封裝一體化EDA設計平臺的最新解決方案。

![的頭像]() 發表于

發表于 11-01 14:12

?291次閱讀

DIC EXPO 2024在陪伴中國顯示產業走過14個春秋之際,DIC系列會展活動將于下周引爆年度顯示盛典,以全球顯示產業交流合作的紐帶,助力產業可持續化健康發展。

![的頭像]() 發表于

發表于 09-27 10:06

?445次閱讀

新思科技宣布推出面向英特爾代工EMIB先進封裝技術的可量產多裸晶芯片設計參考流程,該流程采用了Synopsys.ai EDA全面解決方案和新思科技IP。此外,新思科技3DSO.ai與新思科技3DIC

![的頭像]() 發表于

發表于 08-12 09:50

?628次閱讀

提供了一個統一的協同設計與分析解決方案,通過新思科技3DIC Compiler加速從芯片到系統的各個階段的多裸晶芯片設計的探索和開發。此外,新思科技3DSO.ai與新思科技3DIC

![的頭像]() 發表于

發表于 07-16 09:42

?623次閱讀

近日,在備受矚目的DIC EXPO 2024國際(上海)顯示技術及應用創新展上,天馬展出多項健康顯示技術,并憑借卓越的視覺體驗與技術創新,斬獲“DIC國際顯示技術創新大獎”,全面展示出了天馬在健康

![的頭像]() 發表于

發表于 07-10 16:23

?1019次閱讀

3DIC Compiler協同設計與分析解決方案結合新思科技IP,加速英特爾代工EMIB技術的異構集成 摘要: 新思科技人工智能(AI)驅動型多裸晶芯片(Multi-die)設計參考流程已擴展至

發表于 07-09 13:42

?818次閱讀

7月3日,2024 DIC AWARD國際顯示技術創新大獎頒獎典禮在上海舉行。本屆DIC 展會,維信諾國內首發多款顯示器件產品,全場景顯示應用終端新品齊亮相,一舉斬獲7項DIC AWA

![的頭像]() 發表于

發表于 07-04 16:03

?1716次閱讀

7月2日至5日,2024年中國國際顯示產業高峰論壇暨國際顯示技術及應用創新展(DIC 2024)在上海隆重舉辦。

![的頭像]() 發表于

發表于 07-04 11:27

?1018次閱讀

新思科技EDA事業部戰略與產品管理副總裁Sanjay Bali表示:“新思科技在可投產的EDA流程和支持3Dblox標準的3DIC Compiler光子集成方面的先進成果,結合我們廣泛的IP產品組合,使得我們與臺積公司能夠助力

![的頭像]() 發表于

發表于 05-11 16:25

?467次閱讀

套件賦能可投產的數字和模擬設計流程能夠針對臺積公司N3/N3P和N2工藝,助力實現芯片設計成功,并加速模擬設計遷移。 新思科技物理驗證解決方案已獲得臺積公司N3P和N2工藝技術認證,可

發表于 05-11 11:03

?454次閱讀

報道指出,此次訂單主要由蘋果的功率放大器供應商威訊聯合半導體(Qorvo)下達。威訊方面主要負責設計iPhone天線組件,并集成新芯片以及提供Qorvo功率放大器。這些新芯片采用聯電的3DIC先進工藝進行制造。

![的頭像]() 發表于

發表于 04-02 11:26

?597次閱讀

; 新思科技廣泛的高質量 IP組合降低集成風險并加快產品上市時間,為采用Intel 18A 工藝的開發者提供了競爭優勢; 新思科技 3DIC Compiler提供了覆蓋架構探索到簽收的統一平臺,可實現采用

發表于 03-05 10:16

?397次閱讀

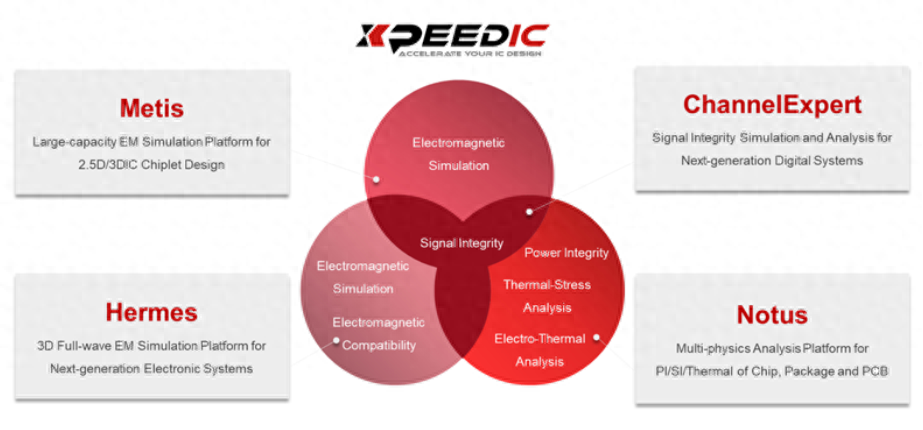

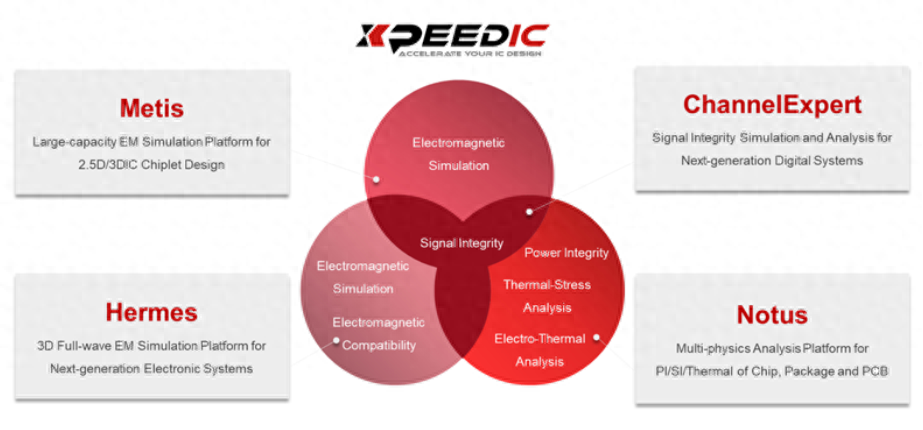

如下: 一、2.5D/3DIC Chiplet先進封裝電磁仿真平臺Metis 具有豐富的布線前仿真分析功能,集成業界2.5D/3D主流制程工藝的Interposer模板,用戶可自定義布線形式和設置參數

![的頭像]() 發表于

發表于 02-18 17:52

?651次閱讀

三天。 針對下一代電子系統的SI/PI/多物理場分析EDA解決方案 發布亮點 2.5D/3DIC Chiplet先進封裝電磁

發表于 02-02 17:19

?772次閱讀

芯和設計訣竅概述 如何使用3DIC Compiler實現Bump Planning

芯和設計訣竅概述 如何使用3DIC Compiler實現Bump Planning

評論