在過去幾年中,多層陶瓷電容器(MLCC)的價格急劇上漲,跟蹤了汽車,工業,數據中心和電信行業中使用的電源數量的擴展。陶瓷電容器用于輸出端的電源中,以降低輸出紋波,并控制由于高壓擺率負載瞬變引起的輸出電壓過沖和欠沖。輸入端需要陶瓷電容器進行去耦和濾除EMI,因為它們在高頻下具有低ESR和低ESL。

為了提高工業和汽車系統的性能,需要將數據處理速度提高幾個數量級,越來越多的高功耗設備被擠入微處理器、CPU、片上系統 (SoC)、ASIC 和 FPGA。這些復雜器件類型中的每一種都需要多個穩壓軌:通常,內核為 0.8 V,DDR3 和 LPDDR4 分別為 1.2 V 和 1.1 V,外設和輔助組件分別為 5 V、3.3 V 和 1.8 V。降壓轉換器廣泛用于從電池或直流母線產生穩壓電源。

例如,高級駕駛輔助系統(ADAS)在汽車中的普及大大提高了陶瓷電容器的使用率。隨著5G技術在電信領域的興起,需要高性能電源,陶瓷電容器的使用也將顯著增加。內核電源電流已從幾安培增加到數十安培,對電源紋波、負載瞬態過沖/欠沖和電磁干擾 (EMI) 的控制非常嚴格,這些功能需要額外的電容。

在許多情況下,傳統的電源方法無法跟上變化的步伐。整體解決方案尺寸太大,效率太低,電路設計太復雜,物料清單(BOM)成本太高。例如,為了滿足快速負載瞬變的嚴格電壓調節規范,輸出端需要大量陶瓷電容器來存儲和源出負載瞬變產生的大量電流。輸出陶瓷電容器的總成本可以達到功率IC的幾倍。

較高的電源工作(開關)頻率可以降低瞬變對輸出電壓的影響,降低電容要求和整體解決方案尺寸,但較高的開關頻率通常會導致開關損耗增加,從而降低整體效率。是否有可能避免這種權衡,并在高級微處理器、CPU、SoC、ASIC 和 FPGA 所需的非常高電流水平下滿足瞬態要求?為了考慮這個問題,讓我們看一下SoC的20 V輸入至1 V/15 A輸出。

15 A 從 20 V 輸入

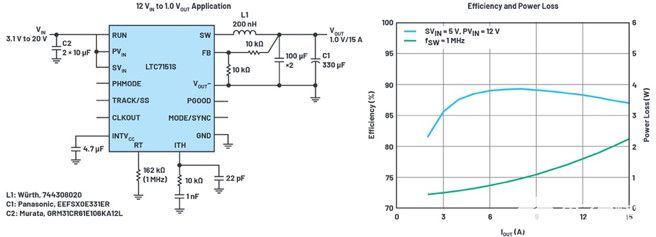

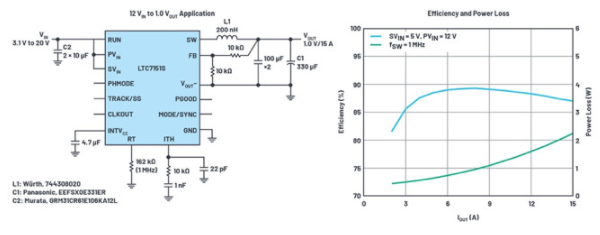

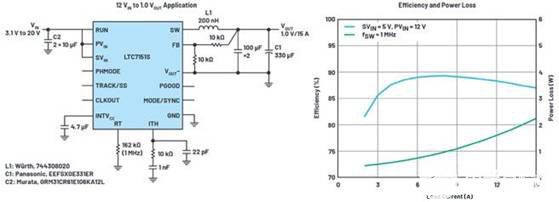

圖1顯示了適用于SoC和CPU電源應用的1 MHz、1.0 V、15 A架構,其輸入典型值為12 V或5 V,可在3.1 V至20 V范圍內變化。只需輸入和輸出電容器、一個電感器以及幾個小電阻器和電容器即可完成電源。可以輕松修改該電路,以產生低至0.6 V的其他輸出電壓,例如1.8 V、1.1 V和0.85 V。輸出軌的負回路(V– 引腳)可實現對靠近負載的輸出電壓進行遠程反饋檢測,從而最大限度地減少由電路板走線壓降引起的反饋誤差。

圖1所示的方法使用具有高性能集成MOSFET的穩壓器。該特定穩壓器是一款LTC7151S單片式降壓穩壓器,它采用靜音開關 2 架構來簡化 EMI 濾波器設計。采用 28 引腳、耐熱性能增強型 4 mm × 5 mm × 0.74 mm LQFN 封裝。通過谷值電流模式進行控制,降低了輸出電容要求。內置保護功能,以最大限度地減少外部保護組件的數量。

頂部開關的最短導通時間僅為20 ns(典型值),能夠以非常高的頻率直接降壓至內核電壓。熱管理功能可在輸入電壓高達 20 V 的情況下實現高達 15 A 的可靠和連續傳輸電流,無需散熱器或氣流,使其成為電信、工業、運輸和汽車應用中 SOC、FPGA、DSP、GPU 和微處理器的熱門選擇。該穩壓器具有寬輸入范圍,可用作第一級中間轉換器,在5 V或3.3 V時支持高達15 A的電流,支持多個下游負載點或LDO穩壓器。

圖1.適用于 SoC 和 CPU 的 1 MHz、15 A 降壓穩壓器的原理圖和效率。

以最小的輸出電容滿足嚴格的瞬態規格

通常,輸出電容會進行縮放,以滿足環路穩定性和負載瞬態響應的要求。對于為處理器內核電壓提供服務的電源,這些規格尤其嚴格,在這些電源中,負載瞬態過沖和下沖必須得到很好的控制。例如,在負載階躍期間,輸出電容必須步進,瞬時提供電流以支持負載,直到反饋環路使開關電流足以接管。通常,通過在輸出側安裝大量多層陶瓷電容器來抑制過沖和下沖,從而滿足快速負載瞬變期間的電荷存儲要求。

此外,將開關頻率推高可以改善快速環路響應,但代價是開關損耗增加。

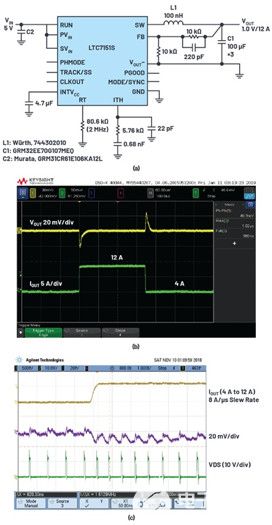

還有第三種選擇:具有谷值電流模式控制的穩壓器可以動態改變穩壓器的開關TON和TOOFF時間,幾乎可以瞬間滿足負載瞬變的需求。這樣可以顯著降低輸出電容,以滿足快速響應時間。圖2顯示了LTC7151S靜音開關穩壓器以8 A/μs壓擺率立即響應4 A至12 A負載階躍的結果。LTC7151S的受控導通時間(COT)谷值電流模式架構允許開關節點脈沖在4 A至12 A負載階躍轉換期間壓縮。上升沿開始后約1 μs,輸出電壓開始恢復,過沖和下沖峰峰值限制為46 mV。圖2a所示的三個100 μF陶瓷電容足以滿足典型的瞬態規格,如圖2b所示。圖2c顯示了負載階躍期間的典型開關波形。

圖2.(a) 此 5 V 輸入至 1 V 輸出應用以 2 MHz 運行,輸出端需要最小電容,以便快速、干凈地響應 (b) 負載階躍以及 (c) 負載階躍期間的開關波形。

3 MHz 時的高效率降壓適合狹小空間

使用高集成度穩壓器可使 MOSFET、驅動器和熱回路電容器保持緊密連接。這減少了寄生效應,并允許以非常窄的死區時間快速打開/關閉開關。開關反并聯二極管的導通損耗大大降低。集成的熱回路去耦電容和內置補償電路也消除了設計復雜性,從而最大限度地減小了解決方案的總尺寸。

如前所述,頂部開關的最小值為20 ns(典型值),允許在高頻下進行非常低的占空比轉換,使設計人員能夠利用超高頻工作(如3 MHz)來減小電感、輸入電容和輸出電容的尺寸和值。極其緊湊的解決方案適用于空間有限的應用,例如汽車和醫療應用中的便攜式設備或儀器。使用 LTC7151S 時,不需要龐大的熱緩解組件,例如風扇和散熱器,這得益于其高性能電源轉換,即使在非常高的頻率下也是如此。

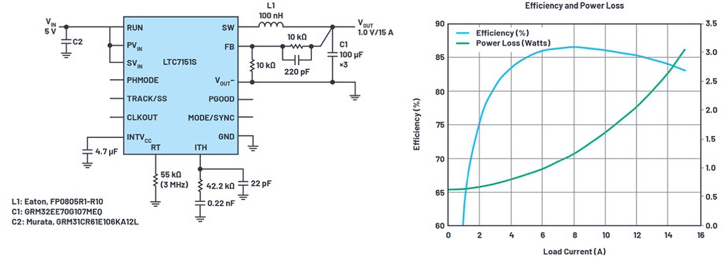

圖3所示為5 V至1 V解決方案,工作在3 MHz開關頻率。伊頓的小尺寸 100 nH 電感器與三個 100 μF/1210 陶瓷電容器相結合,為 FPGA 和微處理器應用提供了超薄的緊湊型解決方案。效率曲線如圖3b所示。室溫下滿載時溫升約15°C。

圖3.5 V 輸入至 1 V/15 A 的原理圖和效率,f西 南部= 3 兆赫。

提高電磁干擾性能

滿足已發布的EMI規范,例如CISPR 22/CISPR 32傳導和輻射EMI峰值限值,應用15 A可能意味著許多迭代電路板旋轉,涉及解決方案尺寸、總效率、可靠性和復雜性的眾多權衡。傳統方法通過減慢開關邊沿和/或降低開關頻率來控制EMI。兩者都有不良影響,例如效率降低、最小開關時間增加以及解決方案尺寸增大。暴力EMI抑制,如復雜而笨重的EMI濾波器或金屬屏蔽,大大增加了所需的電路板空間、元件和組裝成本,同時使熱管理和測試復雜化。

EMI可以通過多種方式降低,包括集成熱回路電容器,以最大限度地減少噪聲天線尺寸。LTC7151S 通過集成高性能 MOSFET 和驅動器來保持低 EMI,從而使 IC 設計人員能夠生產出具有內置最小開關節點振鈴的器件。結果是,即使開關邊沿具有高壓擺率,存儲在熱回路中的相關能量也受到高度控制,從而實現出色的EMI性能,同時最大限度地降低高工作頻率下的交流開關損耗。

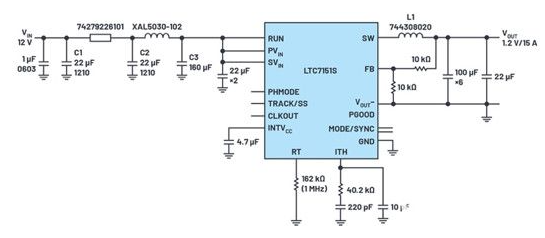

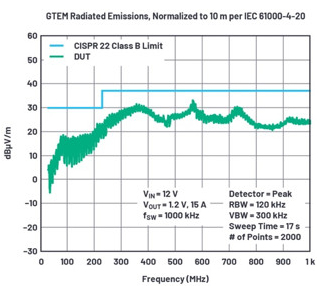

LTC7151S 已在 EMI 測試室中進行了測試,并通過了 CISPR 22 / CISPR 32 傳導和輻射 EMI 峰值限制,前面有一個簡單的 EMI 濾波器。圖4顯示了1 MHz、1.2 V/15 A電路的原理圖,圖5顯示了千兆赫茲橫向電磁(GTEM)電池的輻射EMI CISPR 22測試結果。

圖4.開關頻率為1 MHz的1.2 V穩壓器原理圖。

圖5.GTEM 中的輻射 EMI 超過 CISPR 22 B 類限制。

智能電子、自動化和傳感器在工業和汽車環境中的激增推動了電源所需的數量和性能要求。特別是低EMI,作為關鍵的電源參數考慮因素,以及對小解決方案尺寸、高效率、熱能力、魯棒性和易用性的通常要求,已經越來越受到重視。借助集成穩壓器,開發人員可以在非常緊湊的環境中滿足嚴格的EMI要求。通過谷值電流模式控制和高頻操作,穩壓器可以動態改變TON和TOOFF時間,以近乎瞬時主動支持負載瞬變,從而實現更小的輸出電容和快速響應。最后,集成的 MOSFET 和熱管理可在高達 20 V 的輸入范圍內連續穩定可靠地提供高達 15 A 的電流。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17718瀏覽量

250170 -

MLCC

+關注

關注

46文章

695瀏覽量

45634 -

微處理器

+關注

關注

11文章

2263瀏覽量

82448

發布評論請先 登錄

相關推薦

片式疊層陶瓷介質電容器基礎介紹

汽車和工業用陶瓷盤電容器的設計

降低工業和汽車應用中陶瓷電容器的電源要求

降低工業和汽車應用中陶瓷電容器的電源要求

評論