我們生活在一個模擬世界中,盡管數字技術占主導地位。在域之間移動會導致量化錯誤;這是不可避免的。工程師的工作是使這種過渡盡可能無縫,這就是ADC和DAC的用武之地。

模數轉換(ADC)可以采取多種形式,并有許多折衷方案。從根本上說,關鍵品質因數是準確性和速度。更復雜的是,這兩個參數通常是相反的;更高的精度需要更多的位,但添加更多的位會降低采樣率。更快的轉換通常以有效位數為代價。從廣義上講,選擇由Δ-Σ轉換拓撲(高分辨率,長延遲)或閃存轉換器(高速,但以功耗和面積為代價)結束。介于這兩個極端之間的是逐次逼近寄存器或SAR轉換器。這種“金發姑娘”技術在分辨率和速度之間提供了很好的折衷,但它也有其局限性。

一般來說,SAR轉換器一直是無線通信中使用的模擬前端(AFE)的不錯選擇,這要歸功于它們兼具精度和速度。隨著物聯網的覆蓋范圍從核心進一步延伸,將邊緣永遠向外推,對AFE的需求不斷增長,AFE能夠以更高的頻率(因此更高的采樣率)處理更復雜的協議,但功耗更低。我們不要稱其為問題,而是將其稱為機會,以找到一種技術,可以在無線連接需要安裝到足夠小的東西中佩戴在耳朵中的時代實現更小,更快,更低功耗的AFE,并且可能由從其操作環境中收集的能量供電。

特區的一些背景

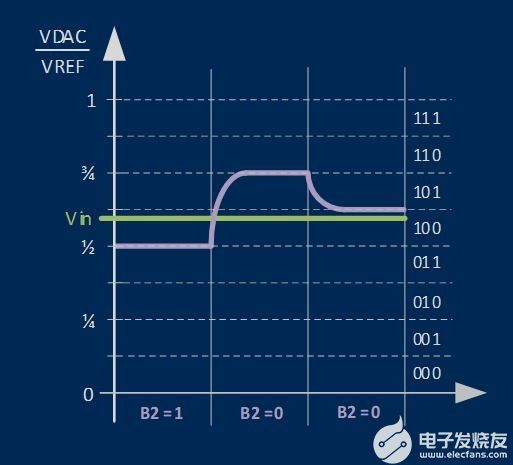

顧名思義,SAR的工作原理是連續近似模擬輸入的值,反復將輸入電壓與反復減半的基準電壓進行比較,直到基準電壓源和源極之間的差異無法區分或滿足設計要求。每次比較都會生成一個“更高”或“更低”的結果,該結果在數字輸出中形成一個位,從最高有效位開始。這種情況一直持續到轉換器以足夠的精度產生足夠的位來表示模擬輸入。

圖 1:3 位 SAR ADC 示例

由于所有步驟都需要在采樣周期內完成,因此可能的位數將主要取決于電路中需要更改的元件的響應時間。這包括用于與輸入電壓進行比較的基準電壓(通常存儲在由開關和電容器組成的采樣保持電路中)。反過來,該基準電壓(通常)由數模轉換器或DAC產生。因此,SAR轉換器的采樣速率將在一定程度上由用于產生基準電壓和控制邏輯的DAC決定,但通常SAR性能實際上受到比較器速度的限制。輸入端的開關電容(實際上是一個低通濾波器)引入了一個較高的頻率閾值,但由于開關的電阻較低,電容很小,這意味著轉換器通常可以處理數百MHz或更高的信號;特區的另一個積極特征。

就整體精度而言,而不僅僅是分辨率,重要的是DAC產生的基準電壓(而不是比較器的DAC產生的電壓)也盡可能準確,因為所有其他測量值都與此相關。盡可能多地集成整體解決方案的SAR,包括開關電容S&H和DAC參考電壓發生器,將提供最佳性能。

克服SAR轉換器的局限性

流水線ADC具有多個級,每個級處理轉換過程的一部分。隨著每個階段完成其操作,它可以自由地接受下一個樣品。流水線ADC提供的主要優勢之一是其速度;一旦管道完全啟動,它就可以在新樣本“推送”數據時生成新的輸出。SAR 的架構通常基于多次使用的單級,而流水線轉換器使用并行性來加快速度。

將SAR和流水線方法相結合,可以產生所謂的SAR輔助流水線ADC。Adesto的工程師已經實施了這種方法,以創建一個ADC,該ADC可以在高帶寬下以最大的速度和精度運行,但需要最小的功率和面積。

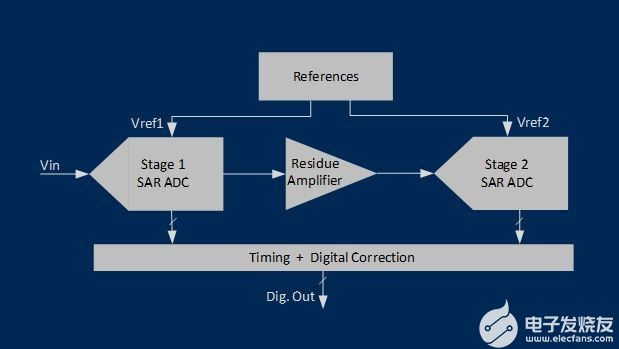

阿德斯托開發的轉換器使用兩個SAR級;第一級處理輸出的最高有效位,而第二級處理最低有效位。通過添加數字模塊來處理時序和校正(見圖2),SAR輔助流水線轉換器生成結果的時間不到同類SAR轉換器的一半,而不會受到傳統流水線ADC相關的損失(包括物理尺寸和功耗)。

圖 2:SAR 輔助流水線 ADC 架構

簡單來說,一旦第一個SAR階段完成轉換,它就可以接受新樣本,而第二個SAR階段完成第一個樣品的轉換。兩級之間的放大器增益放寬了對第二個SAR的要求,從而形成了比SAR本身更節能的解決方案。

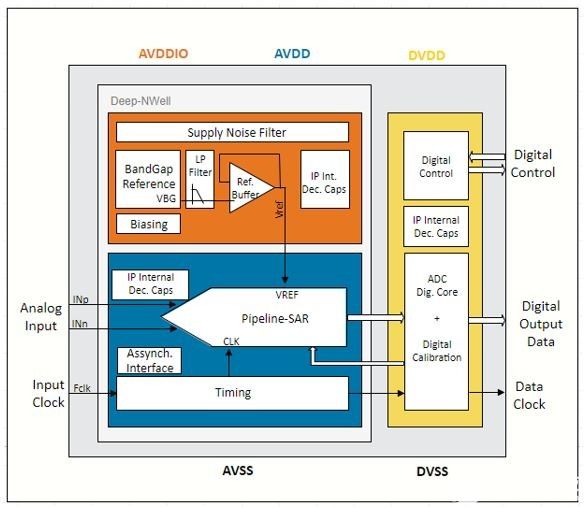

圖3顯示了Adesto的SAR輔助管道ADC的框圖。

圖 3:Adesto 的單通道 SAR 輔助流水線 ADC

如圖3所示,Adesto開發的IP集成了所有關鍵功能,包括基準電壓發生器、定時和控制邏輯、數字校準以及去耦電容。對所有模擬模塊使用深n阱技術可提供對基板噪聲的抗擾度,當IP被許可供客戶在可能沒有專用模擬電源的設計中使用時,這一點尤其重要。該設計非常全面,因為它不需要外部基準電壓源或穩壓器。

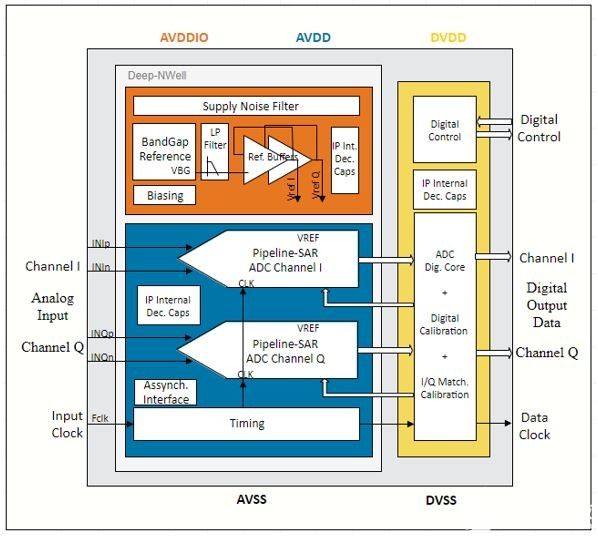

相同的內核 IP 已用于開發針對正交 I/Q 調制架構的雙通道解決方案(圖 4)。可以看出,某些功能可以在兩個通道之間共享,同時包括單獨的基準電壓緩沖器和時鐘樹,以最大程度地減少通道之間的串擾。

圖 4:Adesto 的雙通道 SAR 輔助流水線 ADC

這種方法提供的主要優點之一是其低功耗操作。Adesto部署在現已上市的批量IP中,包括采用28nm工藝的雙通道解決方案,每個通道提供160M樣本/秒,總功耗僅為18mW。該ADC的總芯片面積僅為0.055mm2,因此具有極高的面積效率。盡管集成度如此之高,但它可以提供63.1dB的SNDR,通道之間的串擾低于-80.0dB。

同一轉換器的八通道版本可以同時處理四個I/Q通道,工作速率為122.88Msamples/s,功耗僅為45mW。它的有效位數(ENOB)為10.2位,但仍然只需要0.3mm2的芯片面積。Adesto還可以提供12位SAR輔助流水線ADC,在僅0.05mm2的芯片面積內實現200M采樣/秒的采樣速率,耗散10mW。

AFE在很大程度上依賴于ADC的性能,而不起眼的SAR是工程師可用的最可靠和最通用的架構之一。這只是Adesto提供的IP的一個例子,該IP已經過優化,可滿足最新應用的需求。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8736瀏覽量

147549 -

adc

+關注

關注

98文章

6524瀏覽量

545206 -

物聯網

+關注

關注

2911文章

44824瀏覽量

375134

發布評論請先 登錄

相關推薦

FPGA算法工程師、邏輯工程師、原型驗證工程師有什么區別?

嵌入式軟件工程師和硬件工程師的區別?

更低功耗、更低價格!廣和通Cat.1 bis模組LE370-CN規模量產

更低功耗、更低價格!廣和通Cat.1 bis模組LE370-CN規模量產

工程師對以更低功耗實現更快采樣的回答

工程師對以更低功耗實現更快采樣的回答

評論