大規模多輸入多輸出(mMIMO)的出現為基站硬件帶來了新的射頻挑戰,而新的無線電技術則促進了5G無線的發展。因此,已經面臨日益增加的RF復雜性的5G基礎設施現在要求半導體公司進行另一輪創新,以通過適應性更強的解決方案來提高網絡效率。

到目前為止,通信設備制造商勢必會創建具有特定頻率的多個卡,以滿足無線行業對全球各種許可和未授權5G頻段的要求。以愛立信為例,該公司每周創建兩個電路板設計,以跟上全球所有頻率計劃。

那么,我們如何開發一個與頻率無關且可以在多個地區使用的單一平臺呢?特別是對于mMIMO無線電,它在面板中使用大量天線,這使得網絡效率至關重要。賽靈思聲稱其ZynqUltraScale+ ? RF?片上系統 (SoC) 提供單芯片自適應平臺,可針對多種 5G 標準進行重新配置。

直接射頻采樣

在傳統的模擬方法中,RF信號鏈通過JESD204接口連接到數字前端,RF采樣由分立元件執行。它還涉及每個芯片一個或兩個轉換器。在這里,從一個芯片到另一個芯片的數據轉換可能需要高達8瓦的功率來傳輸320 Gb的數據。

但是,當您使用大量發射器和接收器時,就像在mMIMO設計中一樣,您必須非常注意功耗。因此,Zynq UltraScale+ 提供了一個單芯片自適應無線電平臺,可對射頻信號進行直接采樣。

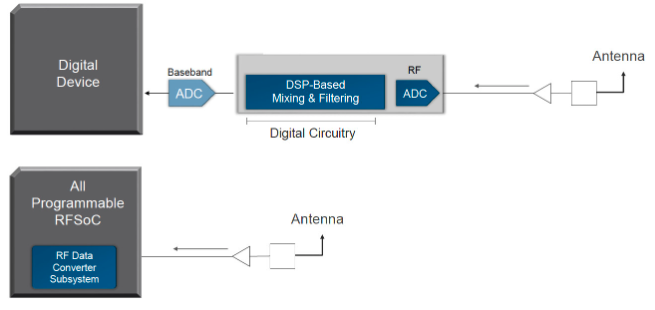

圖 1:傳統基于模擬的方法(上圖)和直接射頻采樣方法(下圖)之間的比較。

直接RF采樣直接處理輸入信號,無需下變頻至中頻(IF)信號,并應用DSP技術在數字域中執行信號調理等任務。這消除了JESD204在RF電路進入下一個芯片執行網絡路由等任務時的瓶頸。

這反過來又簡化了模數信號鏈,并允許處理更多數據,這是5G系統中mMIMO基站的關鍵優勢。該單芯片自適應平臺集成了基帶、無線電IP、MAC、DSP信令和濾波以及具有通用數字處理器和DDR4存儲器子系統的數據轉換器。

例如,RF數據轉換器的集成為降低功耗、占位面積和物料清單(BOM)成本提供了寶貴的途徑。ZynqUltraScale+ 使用 14 位模數轉換器 (ADC) 支持高達 5 Giga 樣本/秒的直接射頻采樣,使用 14 位數模轉換器 (DAC) 支持高達 10 G 采樣/秒的直接射頻采樣。?

在 Zynq UltraScale+ 中,RF ADC 的采樣速率從 4 G 采樣/秒提高到 5 G 采樣/秒,RF DAC 的采樣速率從 6 G 采樣/秒提高到 10 G 采樣/秒。對于時分雙工(TDD)用例,RF數據模塊的功耗降低了20%。在這里,值得一提的是,大多數5G無線電都是基于TDD技術的。

FPGA 如何助力射頻設計

以FPGA為中心的設計通常需要數據轉換器,但到目前為止,只有低性能轉換器被集成到FPGA中,用于系統監控等應用。這主要是因為模擬和數字處理器是由半導體公司的不同集團甚至完全由不同的公司開發的。

數字團隊致力于節點遷移以縮小節點大小,而模擬工程師則使用穩定的舊處理節點。但是,在像mMIMO這樣的現代無線電用例中,它必須改變,這些用例要求更高的集成度。

Xilinx 聲稱,采用 16 nm 鰭式場效應晶體管工藝制造的 Zynq UltraScale+ 是這種更高集成度的體現;它將模擬域和數字域集成到一塊硅片中,以通過可編程邏輯優化信號流。

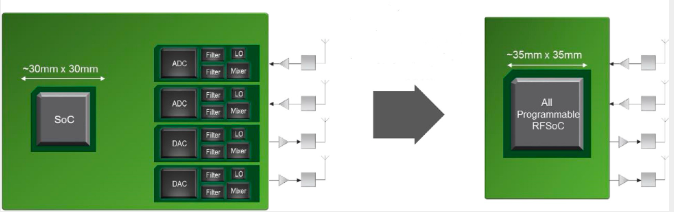

硬件和軟件可編程引擎的集成消除了分立元件,從而將功耗和設計尺寸降低了多達 50%。例如,Zynq UltraScale+ 通過將外部 PLL 振蕩器的數量從四個減少到一個來降低 BOM 成本。

圖 2:集成模擬和數字部件的單芯片射頻解決方案如何降低功耗、占位面積和 BOM 成本。

除了 5G 基站設計,Xilinx 還將這種多頻段無線電芯片用于其他射頻應用,如相控陣雷達網絡和天氣監視系統。然后,還有一些用例,例如用于電纜接入的遠程PHY節點,汽車中的激光雷達系統,測試和測量以及衛星通信。

適應5G世界

5G標準將在未來幾年內不斷發展,這將繼續改變系統要求。因此,與通信設備制造商一直在使用ASIC的3G和4G設計領域不同,靈活的邏輯方法更有可能經受住增量5G部署。

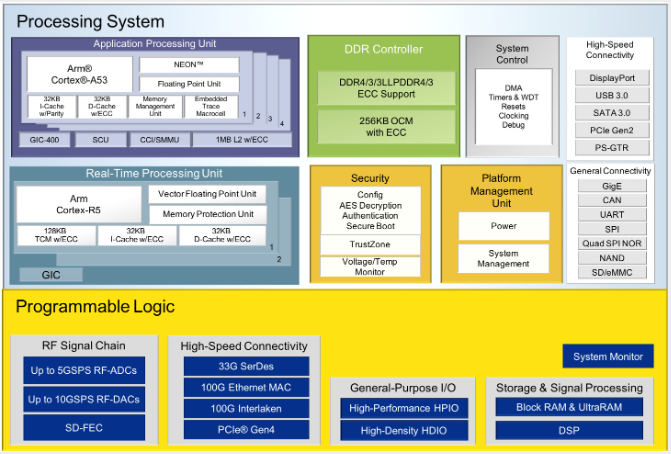

當今5G設計環境中的ASIC解決方案很可能在一年內過時。另一方面,連接模擬域和數字域的可編程解決方案(圖3)可以針對各種5G安裝進行重新配置。

圖 3:顯示不同子系統的 Zynq UltraScale+ 射頻芯片框圖。

本文介紹了一種高度集成的RF芯片的概況,該芯片在數字域內執行下變頻過程,從而繞過了傳統的模擬RF采樣方式,該方式涉及分立元件的下變頻。

生活筆記本:郭婷

-

芯片

+關注

關注

456文章

50954瀏覽量

424779 -

射頻

+關注

關注

104文章

5594瀏覽量

167928 -

無線電

+關注

關注

60文章

2144瀏覽量

116601

發布評論請先 登錄

相關推薦

為什么WBG材料是5G系統未來發展的關鍵?

智能駕駛所需的基礎設施

我國5G發展成就顯著,面臨挑戰與對策

我國5G基站突破400萬個

5G基礎設施開啟射頻芯片內部的新集成前沿

5G基礎設施開啟射頻芯片內部的新集成前沿

評論