“比起削足適履,做一雙合腳的鞋,才是中國(guó)半導(dǎo)體產(chǎn)業(yè)換道超車(chē)的機(jī)會(huì)所在。”

芯片高水平自立自強(qiáng)是我國(guó)偉大復(fù)興征程必須邁過(guò)的“婁山關(guān)”。我國(guó)芯片領(lǐng)域嚴(yán)重受制于人,如果一味在別人的地基上蓋房子,樓越高,國(guó)之重器被“卡脖子”就越嚴(yán)重,常規(guī)跟蹤思路根本難以追趕、更無(wú)法超越,唯有守正創(chuàng)新、另辟蹊徑才能換道超車(chē)。

“比起削足適履,做一雙合腳的鞋,才是中國(guó)半導(dǎo)體產(chǎn)業(yè)換道超車(chē)的機(jī)會(huì)所在。”中國(guó)工程院院士鄔江興對(duì)本刊表示。

于是,2019年鄔江興院士基于系統(tǒng)工程論,融合體系結(jié)構(gòu)和集成工藝創(chuàng)新,帶領(lǐng)團(tuán)隊(duì)提出“可基于落后一至兩代的材料與工藝實(shí)現(xiàn)一流系統(tǒng)”的軟件定義晶上系統(tǒng)(Software Defined System on Wafer,SDSoW),為我國(guó)芯片破解“卡脖子”困局并實(shí)現(xiàn)“換道超車(chē)”提供了戰(zhàn)略支撐,并有望走出一條與封鎖工藝弱相關(guān)的中國(guó)芯片自主創(chuàng)新、換道超車(chē)與戰(zhàn)略突圍之路。

什么是軟件定義晶上系統(tǒng)?

隨著摩爾定律日漸趨緩,當(dāng)前的集成電路產(chǎn)業(yè)發(fā)展正面臨來(lái)自“三堵墻”——“封裝極限”、“良率極限”和“物理極限”的挑戰(zhàn)。簡(jiǎn)單而言,就是當(dāng)前制程工藝逐漸向3nm/1nm發(fā)展逼近物理極限,隨著芯片尺寸增大良率控制會(huì)變得越來(lái)越難,先進(jìn)封裝技術(shù)在散熱、功耗、封裝規(guī)模等方面的問(wèn)題也日益凸顯。

鄔江興院士指出,現(xiàn)有信息系統(tǒng)采用的是“晶圓-芯片-模組-機(jī)匣-機(jī)架-系統(tǒng)”架構(gòu)和基于PCB板與板間互連的“低密度、低帶寬、低能效”稀疏集成技術(shù),這種“堆砌式”、“逐級(jí)插損式”的二流工程技術(shù)路線越來(lái)越難以提高自身的性能和效能,必須要走出一條能夠?qū)ⅰ俺呙芏冉M裝、多維智能連接和軟件定義系統(tǒng)”等諸多要素融合在一起的創(chuàng)新之路。于是,SDSoW技術(shù)應(yīng)運(yùn)而生。

該技術(shù)的核心思想是結(jié)構(gòu)創(chuàng)新連乘工藝創(chuàng)新,旨在對(duì)國(guó)家層面的戰(zhàn)略問(wèn)題進(jìn)行破局,總體包括兩部分:

“軟件定義”晶圓級(jí)系統(tǒng),作為系統(tǒng)之系統(tǒng),以面向領(lǐng)域應(yīng)用的高性能、高效能與高靈活為目標(biāo),遵從“結(jié)構(gòu)適配應(yīng)用”的軟硬件協(xié)同技術(shù)路線,既有領(lǐng)域內(nèi)的靈活性,又有專(zhuān)用級(jí)高性能、高效能,并天然匹配開(kāi)放式復(fù)雜性系統(tǒng)乃至智能系統(tǒng)的靈活高效結(jié)構(gòu)內(nèi)涵,屬于一種新的技術(shù)物理形態(tài)。

可能我們會(huì)更熟悉軟件定義芯片,那么當(dāng)軟件開(kāi)始定義晶圓級(jí)系統(tǒng)時(shí),會(huì)存在哪些差異?鄔江興院士解釋說(shuō),軟件定義芯片的性能/效率增益是線性的,當(dāng)然也存在集成方面的瓶頸,其整體效率的提高是有“線性增益瓶頸”的;然而軟件定義晶圓級(jí)系統(tǒng)則是從系統(tǒng)工程論的角度出發(fā),以提升全系統(tǒng)效能為目的,以體系結(jié)構(gòu)創(chuàng)新和集成工藝創(chuàng)新為手段,以軟件定義晶圓級(jí)系統(tǒng)為基礎(chǔ)達(dá)到1+1》2的非線性效能增益

“晶上系統(tǒng)”是工藝創(chuàng)新,徹底改變傳統(tǒng)單芯片封裝、載芯片于板卡、集板卡成機(jī)柜、組機(jī)柜成系統(tǒng)的“低密度、低帶寬、低能效”逐級(jí)堆砌計(jì)算系統(tǒng)構(gòu)建方式,屬于超高密度、異構(gòu)異質(zhì)、多維拼裝集成的“超微系統(tǒng)”工程技術(shù)路線。

“軟件定義晶上系統(tǒng)是站在信息系統(tǒng)整體的角度對(duì)集成電路設(shè)計(jì)、加工、封測(cè)和應(yīng)用等進(jìn)行‘體系架構(gòu)’與‘工程技術(shù)’的雙重變革。”鄔江興院士說(shuō),SDSoW系統(tǒng)最大的優(yōu)勢(shì)是以晶圓級(jí)系統(tǒng)為基礎(chǔ)載體集成計(jì)算、存儲(chǔ)、通信、網(wǎng)絡(luò)、安全、IO等各種功能,可以是不同工藝節(jié)點(diǎn)的芯粒,也可以是不同材料的芯粒,實(shí)現(xiàn)晶圓上基于“智能韌帶”的“無(wú)插入或低插入損耗”的集成,獲得互連密度、帶寬、延遲和功耗等方面的增益。

其次,SDSoW晶上資源規(guī)模相比于SoC有數(shù)量級(jí)的提升,可以顯著提高體系架構(gòu)創(chuàng)新的增益,不僅可以通過(guò)軟硬件協(xié)同,以變結(jié)構(gòu)實(shí)現(xiàn)高效能,而且還可以隨著運(yùn)行“閱歷”的積累,能夠使運(yùn)行結(jié)構(gòu)自我優(yōu)化、自動(dòng)演化,具有1-3個(gè)數(shù)量級(jí)的性能與效能增益。

這意味著,基于國(guó)內(nèi)二流乃至三流工藝實(shí)現(xiàn)超高密度、異構(gòu)異質(zhì)拼裝集成的“超微系統(tǒng)”工程技術(shù)路線,完全可以與采用一流工藝器件、傳統(tǒng)工程技術(shù)路線的系統(tǒng)相媲美,甚至實(shí)現(xiàn)超越。

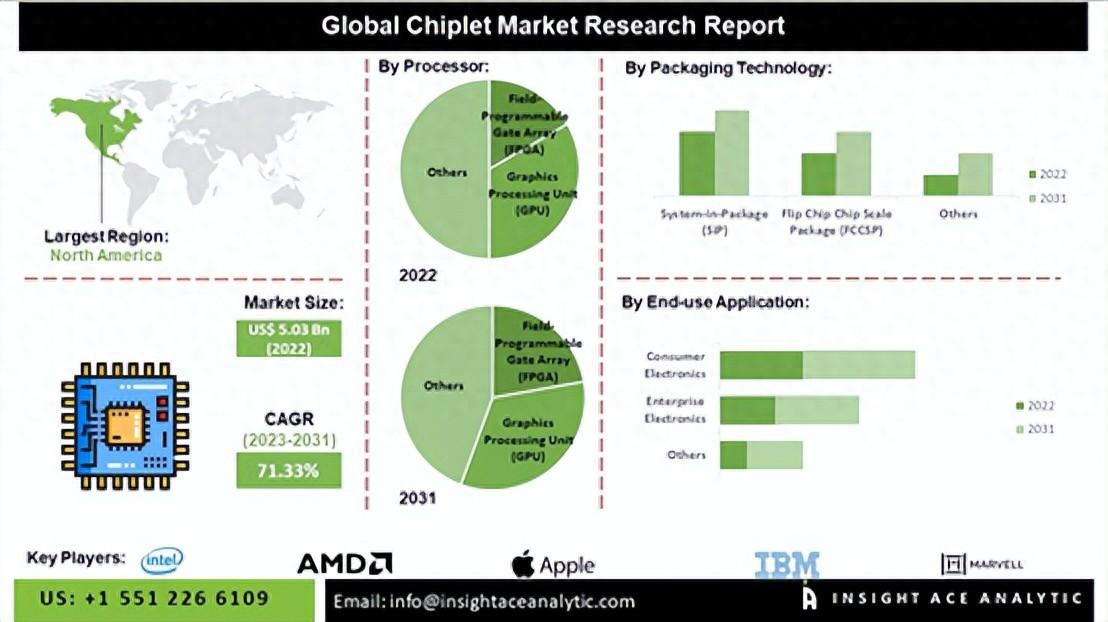

僅靠Chiplet不能救中國(guó)

熟悉Chiplet技術(shù)的人士都懂得,該技術(shù)是將大型單芯片劃分為多個(gè)相同或者不同的小芯片,這些小芯片可以使用相同或者不同的工藝節(jié)點(diǎn)制造,再基于傳統(tǒng)的PCB封裝技術(shù)或者硅基板實(shí)現(xiàn)跨芯片互連和封裝級(jí)別集成。那么,它和SDSoW系統(tǒng)之間存在哪些異同?

資料顯示,SDSoW采用了Wafer(晶圓)級(jí)的硅基板和封裝技術(shù),可以將不同構(gòu)造、不同功能、不同工藝的芯粒(Dielet)像拼積木—樣組裝或集成到晶圓上,通過(guò)復(fù)用芯粒可快速組裝成異構(gòu)、異質(zhì)、異工藝的晶圓級(jí)復(fù)雜系統(tǒng),并能極大的縮小信息系統(tǒng)的體積與功耗,指數(shù)量級(jí)的提升系統(tǒng)性能。

相比于傳統(tǒng)的Chiplet封裝技術(shù),SDSoW集成規(guī)模要大得多,即能將更多的系統(tǒng)功能微縮至單片或多個(gè)可拼接的Wafer上,具有更高的集成密度、更小的片間互連延遲和更為智能的連接韌帶。SDSoW制造過(guò)程中要求突破晶圓中跨光罩區(qū)域之間的大規(guī)模互連技術(shù)以及TSV(硅通孔)工藝技術(shù),晶圓級(jí)硅基板制造不需要先進(jìn)的制造工藝,可利用當(dāng)前次代或成熟的半導(dǎo)體前道/后道金屬工藝,即能采用二流的制造工藝+創(chuàng)新的系統(tǒng)設(shè)計(jì)實(shí)現(xiàn)一流的系統(tǒng)。

在鄔江興院士看來(lái),Chiplet是面向后摩爾時(shí)代的微電子技術(shù),SDSoW是面向信息基礎(chǔ)設(shè)施與信息物理系統(tǒng)所面臨的瓶頸問(wèn)題與發(fā)展方向提出的系統(tǒng)級(jí)技術(shù)體系,兩者之間并沒(méi)有對(duì)立之處,只是技術(shù)思想提出的“原點(diǎn)”不一樣。換句話說(shuō),SDSoW融合了結(jié)構(gòu)創(chuàng)新與工藝創(chuàng)新,集成規(guī)模更大,集成資源更多,是一條包含Chiplet,又可以超越Chiplet的具有中國(guó)創(chuàng)新內(nèi)涵的自主發(fā)展路線。

在回答“為什么中國(guó)需要SDSoW技術(shù)”時(shí),鄔江興院士說(shuō),美國(guó)發(fā)展Chiplet,中國(guó)同樣發(fā)展Chiplet,但我們?nèi)匀幻媾R材料、工藝和工具的落后,一樣處于在同一賽道上、同一游戲規(guī)則下的追趕囧境,因此僅靠Chiplet不能救中國(guó),也不能支撐偉大復(fù)興戰(zhàn)略。

尤其是在當(dāng)下,我國(guó)的材料乃至工藝落后國(guó)際先進(jìn)水平兩代以上,而自2018年以來(lái),主要競(jìng)爭(zhēng)對(duì)手利用其在微電子領(lǐng)域的絕對(duì)技術(shù)優(yōu)勢(shì),對(duì)我信息技術(shù)發(fā)展的物理基礎(chǔ)實(shí)施釜底抽薪式的絞殺,封鎖層層加碼,絞殺步步緊逼,我國(guó)微電子產(chǎn)業(yè)與相關(guān)技術(shù)領(lǐng)域發(fā)展面臨斷崖式下降的風(fēng)險(xiǎn),亟待走出一條以國(guó)內(nèi)大循環(huán)為主體結(jié)合廣泛的國(guó)際合作的“雙循環(huán)”的自主創(chuàng)新、戰(zhàn)略突圍之路。

SDSoW的應(yīng)用之路

軟件定義晶上系統(tǒng)從提出到現(xiàn)在,經(jīng)歷了從懷疑到追隨的過(guò)程,到目前為止已經(jīng)在國(guó)內(nèi)蓬勃發(fā)展起來(lái)。鄔江興院士透露,目前SDSoW已列入國(guó)家2035的相關(guān)規(guī)劃以及“十四五”科技規(guī)劃,依托之江實(shí)驗(yàn)室、嵩山實(shí)驗(yàn)室、紫金山實(shí)驗(yàn)室等重點(diǎn)實(shí)驗(yàn)室的先導(dǎo)項(xiàng)目研究,SDSoW系統(tǒng)已經(jīng)在快速推進(jìn)關(guān)鍵技術(shù)的研究和核心工藝的研發(fā),力爭(zhēng)在“十四五”完成軟件定義晶上系統(tǒng)的關(guān)鍵技術(shù)突破、關(guān)鍵工藝研發(fā)和系統(tǒng)生態(tài)構(gòu)建。

具體而言,圍繞“十四五”規(guī)劃,科技部在微納電子等五個(gè)方向重點(diǎn)專(zhuān)項(xiàng)中進(jìn)行了任務(wù)規(guī)劃,并陸續(xù)立項(xiàng)相關(guān)課題,國(guó)防領(lǐng)域也啟動(dòng)了相關(guān)任務(wù)布局。后續(xù)將著重聚焦國(guó)內(nèi)集成電路整體上下游產(chǎn)業(yè)和技術(shù)的聯(lián)動(dòng),聚焦高算力、AI等領(lǐng)域應(yīng)用,率先從互連標(biāo)準(zhǔn)制定、核心技術(shù)研究和關(guān)鍵工藝研發(fā)上實(shí)現(xiàn)突破,解決超算、智算、數(shù)據(jù)中心、核心網(wǎng)絡(luò)、自動(dòng)駕駛等高算力領(lǐng)域和智能AI領(lǐng)域的“卡脖子”問(wèn)題。

例如在高性能計(jì)算領(lǐng)域,傳統(tǒng)超級(jí)計(jì)算機(jī)采用超大規(guī)模計(jì)算芯片堆砌的方式構(gòu)建,不僅體積大,且功耗極高,E級(jí)機(jī)功耗近百兆瓦量級(jí),已經(jīng)成為難以逾越的功耗墻,陷入即便“能買(mǎi)得起馬也配不起鞍”的窘境。但是,針對(duì)大部分應(yīng)用的計(jì)算效率卻僅有峰值效率的10-20%。SDSoW通過(guò)高密度集成、“結(jié)構(gòu)適配應(yīng)用”的變結(jié)構(gòu)計(jì)算、剝離SerDes等芯片接口模塊等方式,能夠?qū)崿F(xiàn)計(jì)算效能的大幅提升,可以在不需要提升制程工藝的條件下全面滿(mǎn)足需求。

根據(jù)規(guī)劃,SDSoW將經(jīng)歷三個(gè)發(fā)展階段:階段一:做出來(lái),破解卡脖子急需,保證指標(biāo)不倒退、核心不被卡死;階段二:做得好,在規(guī)模性、經(jīng)濟(jì)性、敏捷性和生態(tài)完備性等方面取得突破,擴(kuò)大應(yīng)用場(chǎng)景,形成巨大的新興產(chǎn)業(yè)規(guī)模;階段三:智能晶上系統(tǒng),軟件定義互連(Software Defined Interconnection,SDI)升級(jí)為神經(jīng)網(wǎng)絡(luò),晶上系統(tǒng)演化為智能系統(tǒng),為智能時(shí)代提供物理底座。

不做離開(kāi)生態(tài)系統(tǒng)的“無(wú)源之水”

2017年,由國(guó)家數(shù)字交換系統(tǒng)工程技術(shù)研究中心(NDSC)、清華大學(xué)等牽頭組建了SDI技術(shù)與產(chǎn)業(yè)創(chuàng)新聯(lián)盟,發(fā)展至今成員單位超270家,成功舉辦4屆聯(lián)盟大會(huì),策劃聯(lián)盟互動(dòng)百余次,形成聯(lián)盟生態(tài)合作30余項(xiàng),合作經(jīng)費(fèi)超5億元,極大地促進(jìn)了軟件定義互連產(chǎn)業(yè)聚集及發(fā)展合作。2019年,隨著SDSoW技術(shù)的提出,SDI聯(lián)盟在2022年全面升級(jí)為“軟件定義晶上系統(tǒng)”聯(lián)盟。

鄔江興院士表示,從軟件定義晶上系統(tǒng)技術(shù)本身而言,這一技術(shù)體系是完全開(kāi)放的,對(duì)其他技術(shù)也是包容的,聯(lián)盟不反對(duì)國(guó)外資本乃至企業(yè)加入。然而,在中美科技激烈競(jìng)爭(zhēng)時(shí)代背景下,SDSoW是破解我國(guó)芯片“卡脖子”困局并實(shí)現(xiàn)“換道超車(chē)”的重要戰(zhàn)略支撐,在這種情況下外資企業(yè)會(huì)不會(huì)來(lái)?能不能來(lái)?考驗(yàn)著境外投資者和企業(yè)決策者們的智慧與勇氣。

同樣,“如何把SDSoW的技術(shù)優(yōu)勢(shì)轉(zhuǎn)化為市場(chǎng)優(yōu)勢(shì)?”,也考驗(yàn)著中方。鄔江興院士指出,首先,要堅(jiān)持開(kāi)放共贏,吸引現(xiàn)有的各個(gè)方向技術(shù)優(yōu)勢(shì)單位參與進(jìn)來(lái),進(jìn)行技術(shù)合作;其次,守正創(chuàng)新,軟件定義晶上系統(tǒng)的關(guān)鍵技術(shù)包括預(yù)制件設(shè)計(jì)、軟硬件協(xié)同架構(gòu)設(shè)計(jì)、晶圓級(jí)互連網(wǎng)絡(luò)設(shè)計(jì)、晶圓基板集成設(shè)計(jì)、供電散熱設(shè)計(jì)等,要有打破藩籬的創(chuàng)新思維,不斷進(jìn)行技術(shù)迭代優(yōu)化;第三,要通過(guò)高效合作形成共識(shí)創(chuàng)建中國(guó)自己的行業(yè)標(biāo)準(zhǔn),利于后續(xù)軟件定義晶上系統(tǒng)方向的發(fā)展;最后,對(duì)當(dāng)前的卡脖子、痛點(diǎn)領(lǐng)域進(jìn)行突破,優(yōu)先考慮該類(lèi)領(lǐng)域的產(chǎn)品研制和應(yīng)用推廣。

值得關(guān)注的是,鄔江興院士團(tuán)隊(duì)近期將依托SDSoW聯(lián)盟向聯(lián)盟成員單位免費(fèi)公開(kāi)3項(xiàng)核心專(zhuān)利,分別是《軟件定義晶上系統(tǒng)及數(shù)據(jù)交互方法和系統(tǒng)體系架構(gòu)》、《一種領(lǐng)域?qū)S玫能浖x晶圓級(jí)系統(tǒng)和預(yù)制件互連與集成方法》、《晶上系統(tǒng)開(kāi)發(fā)環(huán)境搭建方法及系統(tǒng)》,涵蓋了系統(tǒng)體系架構(gòu)、拼裝互連集成與開(kāi)發(fā)環(huán)境工具等,共同組成了SDSoW的“根”,對(duì)晶上系統(tǒng)的技術(shù)加速創(chuàng)新和產(chǎn)業(yè)快速普及具有很好的指導(dǎo)意義。

結(jié)語(yǔ)

SDSoW在基于“三流材料、二流工藝”實(shí)現(xiàn)“一流系統(tǒng)”的同時(shí),也要求應(yīng)用、設(shè)計(jì)、工具、制造、工藝等產(chǎn)業(yè)鏈上下游協(xié)同配合。鄔江興院士希望能依托SDSoW聯(lián)盟,最大化匯聚國(guó)內(nèi)晶上系統(tǒng)方向的科技與產(chǎn)業(yè)力量,為我國(guó)芯片高水平自立自強(qiáng)做出“不可替代”的貢獻(xiàn)。

審核編輯 :李倩

-

半導(dǎo)體

+關(guān)注

關(guān)注

334文章

27583瀏覽量

220621 -

摩爾定律

+關(guān)注

關(guān)注

4文章

636瀏覽量

79137 -

chiplet

+關(guān)注

關(guān)注

6文章

434瀏覽量

12609

原文標(biāo)題:如果Chiplet不帶中國(guó)玩了……

文章出處:【微信號(hào):井芯微電子,微信公眾號(hào):井芯微電子】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

解鎖Chiplet潛力:封裝技術(shù)是關(guān)鍵

Cadence推出基于Arm的系統(tǒng)Chiplet

Chiplet技術(shù)有哪些優(yōu)勢(shì)

2035年Chiplet市場(chǎng)規(guī)模將超4110億美元

IMEC組建汽車(chē)Chiplet聯(lián)盟

Primemas選擇Achronix eFPGA技術(shù)用于Chiplet平臺(tái)

2031年全球Chiplet市場(chǎng)預(yù)測(cè)

國(guó)產(chǎn)半導(dǎo)體新希望:Chiplet技術(shù)助力“彎道超車(chē)”!

創(chuàng)新型Chiplet異構(gòu)集成模式,為不同場(chǎng)景提供低成本、高靈活解決方案

西門(mén)子EDA創(chuàng)新解決方案確保Chiplet設(shè)計(jì)的成功應(yīng)用

北極雄芯獲云暉資本投資,加速Chiplet研發(fā)與產(chǎn)品化

前景一片大好的Chiplet,依然存在門(mén)檻問(wèn)題

Chiplet是否也走上了集成競(jìng)賽的道路?

什么是Chiplet技術(shù)?

Chiplet技術(shù)對(duì)英特爾和臺(tái)積電有哪些影響呢?

僅靠Chiplet不能救中國(guó)

僅靠Chiplet不能救中國(guó)

評(píng)論