本系列的前兩期重點介紹嵌入式模數轉換器(ADC)的可配置性,以及如何在所有用例中保持ADC性能。一旦你理解了這一點,你就可以設定適當的期望并繼續實施設計。

本系列的第三部分討論了如何實現設計以滿足預期性能,并介紹了解決噪聲問題的原理圖和布局概念。

電源解耦

為ADC提供穩定的電源和基準電壓源是電路設計中的一個重要因素。對于分布在印刷電路板 (PCB) 上的電源,這意味著在微控制器 (MCU) 和其他集成電路 (IC) 電源和接地引腳之間提供低阻抗路徑,并在電源和接地之間提供低阻抗。這種低阻抗是反比關系,頻率以電容表示,阻抗Z與頻率成反比。相反,更多的電感路徑將是高阻抗,因為阻抗與頻率成正比。

提供低阻抗路徑的最常見方法是使用電源層和去耦電容。然而,由于布局選擇和元件放置不當,這些方法的有效性通常會受到影響。最經典的例子是使用細走線和長走線(電感比電容更感)將去耦電容或過孔(到電源層)連接到電源和接地器件引腳。擁擠的球柵陣列封裝類型可能使避免長而窄的走線更具挑戰性,但在規劃逃生布線時,應優先考慮電源阻抗。

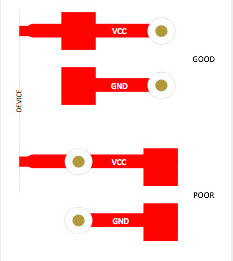

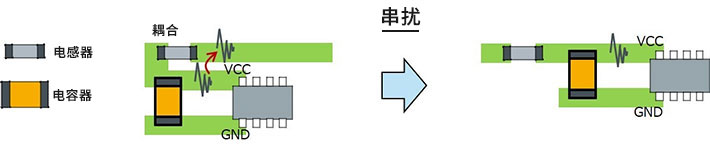

圖1顯示了另一個簡單但經常被忽視的錯誤,即相對于電源層通孔和電源引腳去耦電容放置。由于去耦電容未放置在電源源極和引腳之間,因此額外的走線長度的電感會降低電容的有效性。

圖 1:相對于過孔和器件的去耦電容器位置

雖然大多數MCU具有單個電源軌或建議連接數字和模擬電源軌,但您可以分離模擬和數字電源(以及接地回路),以提供與系統其余部分的隔離。鐵氧體磁珠或通過0Ω電阻短路通常會提供足夠的阻抗來分離電源。提供單獨的模擬和數字電源時,請記住有關這兩個電源之間關系的任何要求。兩者之間允許的電壓差通常相對較小。同樣,鐵氧體磁珠或0Ω電阻提供足夠的阻抗來分離電源,但又足夠小以最小化電壓差。

模數轉換器基準電壓源

一些ADC使用MCU電源作為基準電壓源,因此更加重視電源去耦。其他MCU提供內部帶隙電路,以在內部生成基準電壓源;還有一些提供接口以從外部提供基準電壓源。通常,外部引用可提供最高質量,但您仍然需要良好的布局實踐來實現改進的性能。

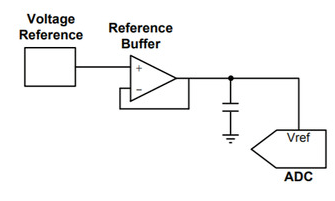

雖然可以將電源層專用于基準電壓,但這通常成本高昂且不受歡迎。為了最小化基準電壓源和ADC基準電壓源輸入之間的阻抗,使走線寬度盡可能寬和短。去耦電容的位置(如圖2所示)提供了一條低阻抗接地路徑,并且還應遵循相同的電源去耦建議[1]。

圖 2:簡單 ADC 基準電壓源電路

信號路由

除了提供干凈的電源外,信號本身還需要沒有任何意外信號或干擾。不需要的信號可能是傳導或輻射發射的結果。由于發射源并不總是可控的,讓我們看一些簡單的方法來降低信號跡線對干擾的敏感性。

在談論易感性時,它可以幫助確定三個組成部分:侵略者、受害者和媒介。侵略者是輻射或傳導干擾的來源。在本討論中,受害者是ADC輸入。介質是傳導或輻射干擾的路徑。本次信號路由討論的目的是解決介質問題,以衰減從攻擊者傳輸到受害者的能量。

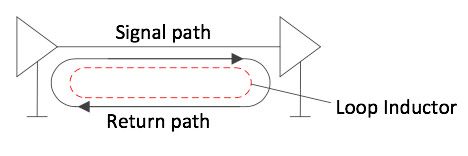

降低敏感性的一種方法是使傳感器和ADC之間的模擬走線盡可能短。圖3顯示了由信號和返回路徑產生的電感環路區域。減小信號路徑將縮小環路面積并降低環路的電感,使其不易受到侵略者電路磁場的影響。

圖3還說明了信號層下方接地層的重要性。通過直接在信號路徑下方提供平面,返回路徑可以遵循阻抗(電感)最小的路徑。接地層中的分離(或不提供任何接地層)將導致返回電流找到備用路徑,這通常會導致更高的阻抗和電磁兼容性(EMC)問題。

圖 3:環路面積和信號路徑距離

使介質效率降低的另一種方法是使其更長,為信號衰減提供更大的距離。這是使敏感的模擬信號遠離數字信號的主要原因,例如脈寬調制器(PWM)和通信線路(I2C、通用異步接收器發射器 [UART]、串行外設接口 [SPI])。一個好的規則是將這些數字信號保持在距離模擬信號至少兩倍的走線寬度。對于某些設計,您必須打破此規則,并且信號必須交叉路徑(在單獨的層上)。在這種情況下,最好通過90度交叉將耦合面積保持在最小水平,并在可能的情況下在信號層之間插入接地層。

接地層和接地走線(保護走線)是衰減介質的另一種有效方法。信號層上的接地澆注(共面澆注)以及保護走線可以進一步降低高頻下信號到地的阻抗。為了確保接地路徑是低阻抗的,保護走線和接地傾倒寬度需要足夠寬以降低電感。一個好的規則是信號跡線寬度的兩倍。使用共面接地澆注和保護走線的另一個好做法是沿信號路徑使用多個過孔。這被稱為通孔“縫合”,因為過孔位于信號的兩側,類似于縫紉圖案。在內部信號層上方和下方使用接地層也可以最大限度地減少耦合并屏蔽敏感的模擬走線。

布局規劃

如果計劃,實現信號路由和使用前面部分中討論的電源層要容易得多。如果沒有重要的規劃步驟,開發人員可以輕松地將自己路由到PCB的角落,除了擦除和重新開始之外,沒有其他恢復方法。

你應該記住兩件事。首先是電路板堆疊。電源層和接地層提供低阻抗路徑,并且是固有的屏蔽,但增加層會增加電路板成本。雖然成本可能是一個驅動因素,但如果不對PCB進行必要的投資,實現精密測量將非常困難。

要記住的第二件事是,從MCU開始將敏感的模擬電路與嘈雜的數字電路分開。一些制造商有意將與模擬相關的功能分組到芯片或封裝的一側,以幫助開發人員將這些信號與器件上的其他數字信號隔離開來。另一個有助于分離模擬和數字信號的MCU功能是引腳映射。引腳映射為自定義數字輸出位置提供了更大的靈活性,以解決應用和與模擬信號分離的問題。

作為旁注,如果模擬信號通過引腳映射器,或者即使模擬信號與其他數字信號多路復用,也應確認專用和多路復用(與數字共享)模擬引腳之間的模擬性能一致。有時(但并非總是如此),數字模塊周圍的保護電路會對共享該引腳的模擬信號的性能產生負面影響。

通過良好的規劃并遵守良好的電路和布局實踐,可以在定制設計中獲得ADC的數據手冊性能。在某些情況下,您無法消除電路設計或PCB布局中的噪聲。這些應用適用于差分信號,其中噪聲被視為共模并由ADC抑制。本系列的最后一期也是最后一期將介紹差分信號,以及它如何解決設計內外的噪聲問題。

審核編輯:郭婷

-

pcb

+關注

關注

4324文章

23135瀏覽量

398883 -

adc

+關注

關注

98文章

6524瀏覽量

545206

發布評論請先 登錄

相關推薦

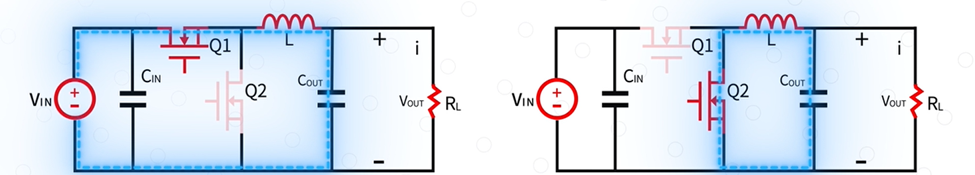

Buck電路中PCB layout布局設計和注意事項

解決噪聲問題的PCB注意事項

解決噪聲問題的PCB注意事項

評論