關于PCIe6.0 你需要知道的都在這里

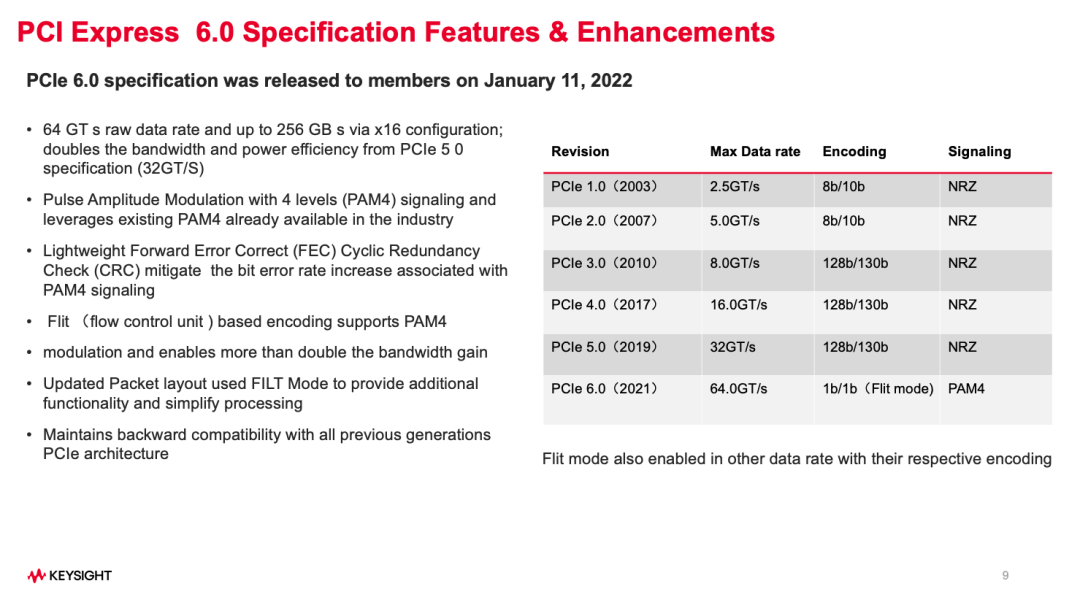

從正式發布至今,PCI Express(PCIe)發展迅速,已經成為高性能計算、人工智能/機器學習(ML)加速器、網絡適配器和固態存儲等應用不可或缺的一項技術。行業永不滿足帶寬需求促使PCIe的協議版本不斷被刷新,2022年1月,PCI-SIG組織宣布PCIe 6.0規范標準v1.0版本正式發布,宣告完工。

?

數據速率從32GT/s翻倍至64GT/s

?

從NRZ編碼轉換到PAM4編碼,可以在單個通道、同樣時間內封包更多數據

?

從傳輸的可變大小TLP到固定大小FLIT,從而提高帶寬效率,降低延時

?

LTSSM新增低功耗狀態L0p

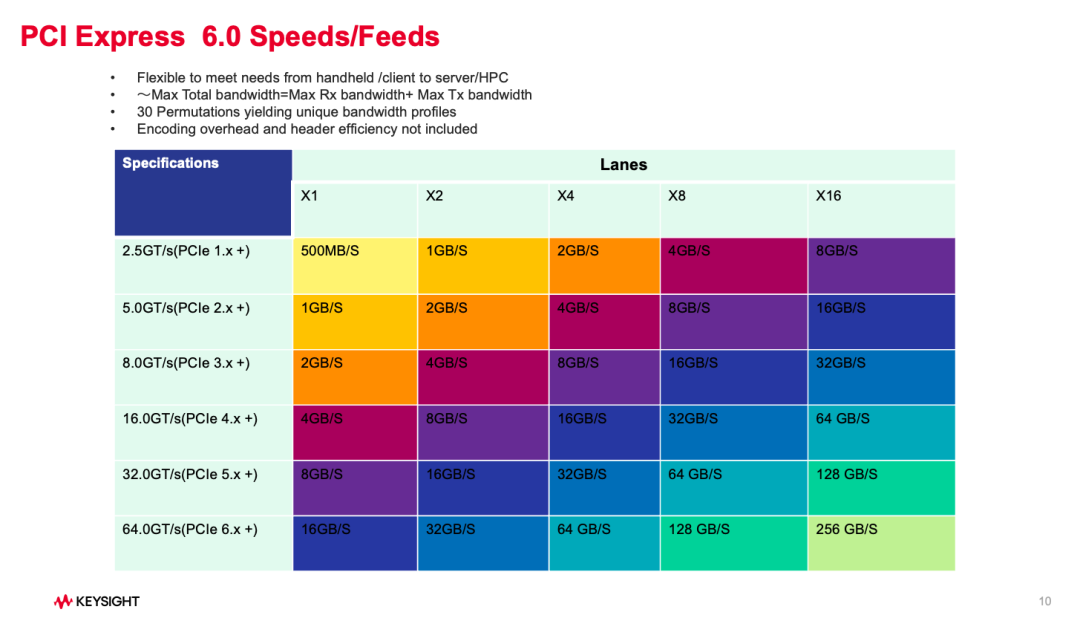

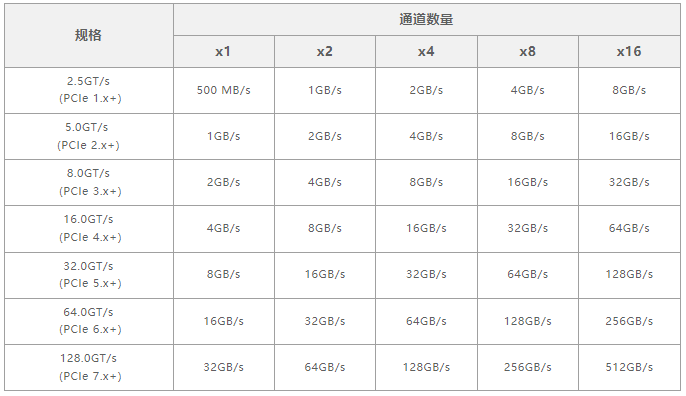

翻倍的64GT/s數據速率

首當其沖的是,從5.0到6.0的數據速率翻倍遞增,6.0支持64GT/s,16路雙向傳輸帶寬可達 256GB/s;對于數據速率翻倍的PCIe 6.0,如何保證系統性能變得尤為重要!PCIe的系統性能取決于RTT(Round-TripTime)及有效負載大小,簡單來說就是工程師們需要確定系統所需的未處理、未發布請求的數量,從而來保證數據流的暢通。該數量轉換為可用標簽的數量,并且是必須根據系統需求正確設置的控制器屬性。相較于PCIe 5.0的768標簽數量,PCIe6.0對其的要求則變成了基于14位的15,360個標簽數量,這樣就滿足了在RTT較長的情況下也能使系統整體保證高性能的工作狀態。

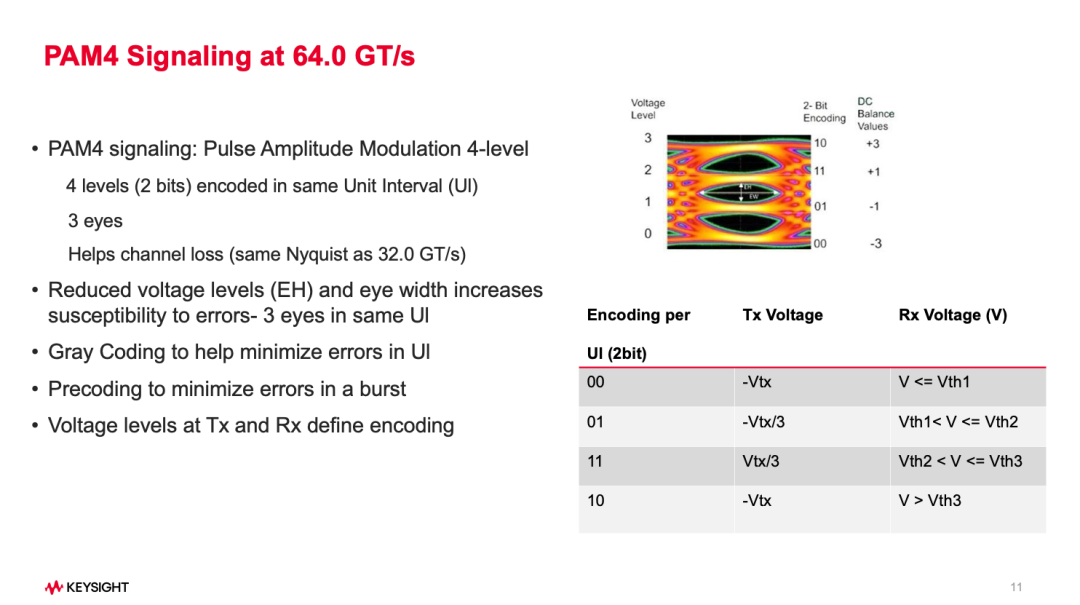

首次采用高階調制格式PAM4

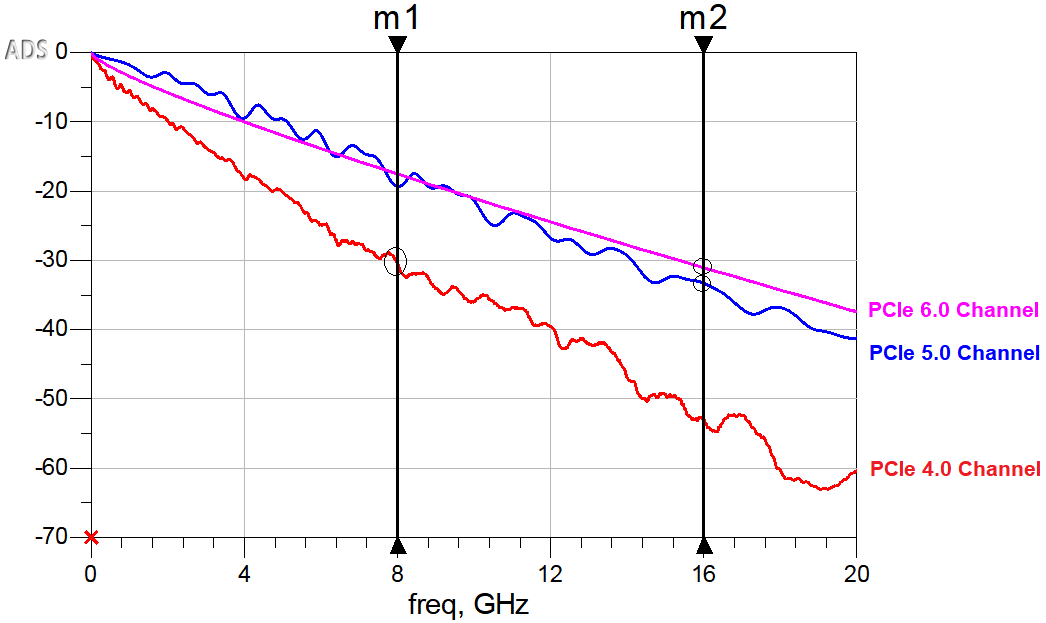

PCIe 5.0采用的32G NRZ編碼已經使得Gen5的頻率相關損耗比之前任意一代的頻率損耗都要嚴重,假設PCIe 6.0 保留NRZ編碼格式,那么它的通道損耗將達到60dB,這顯然是不行的。所以新發布的PCIe 6.0采用高階調制格式PAM4,這樣的做法會使得在信號幅度相同的情況下信噪比天然會下降約9.5dB。但是這樣的做法會使得系統對噪聲更加敏感(比如電源噪聲、串擾、反射等),為降低該影響,新版規范在綜合考量了FBER、FIT、FLIT Retry 概率、帶寬效率、Latency 及 FLIT 的 FEC 能力后,采用了輕量級FEC配合使用循環冗余碼(CRC),那么這種做法就可以在降低噪聲敏感性的基礎上將FEC帶給系統延遲控制在2ns之內。

FLIT模式

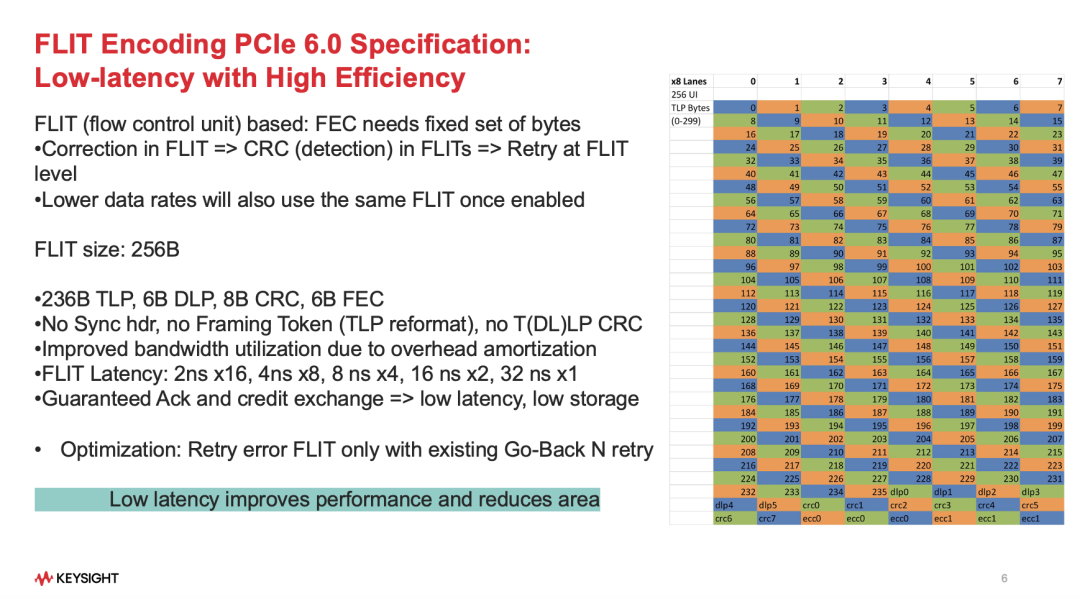

PCIe 6.0引入了FLIT模式(流量控制單元),也是PCIe 6.0標準最大的變化之一,與物理層的PAM4不同,FLIT編碼用于邏輯層,將數據分解為固定大小的數據包。PCIe 6.0以FLIT為單位進行事務傳輸,每個FLIT有256 B數據(1 FLIT=236B TLP+6B DLP+8B CRC+6B FEC=256B),每B數據占用4 UI。以x8為例,一次FLIT傳輸的格式如下圖所示。

最初引入FLIT模式的原因是糾錯需要從而使用固定大小的數據包;然而,FLIT模式也簡化了控制器級別的數據管理,隨之而來的是更高的帶寬效率、更低的延遲和更小的控制器占用空間。帶寬效率:對于固定大小的包,不再需要物理層的包幀,這為每個包節省了4字節。FLIT編碼還消除了以前PCIe規范的128B/130B編碼和DLLP(數據鏈路層數據包)開銷,從而顯著提高了TLP(事務層數據包)效率。

FEC /CRC助力FBER

PCIE6.0規范定義了FBER是1E-6,那么為什么是1E-6呢?能否放寬至1E-4,滿足PCIe 5.0通常的傳輸距離或IL目標呢?答案是否定的。參考以太網標準放寬至1E-4,需要使用復雜RS-FEC糾錯,延時將增加到約100ns量級,這對負載和存儲等對時延敏感的應用是一個很大的挑戰。

為滿足FBER=1E-6目標,PCIe 6.0引入輕量級FEC和魯棒性強的CRC算法實現修正和錯誤檢測。相比100G/400G以太網標準中經常用到的RS(544,514),該FEC實現相對簡單,在固定包長度Flit模式下,6字節的FEC“保護”242字節Payload和8字節CRC,2字節1組實現FEC Group通過交織方式抵抗突發錯誤。如果FEC解碼完成,但CRC仍檢測到錯誤,那么接收側會發送NAK啟動重傳,為提高效率,該模式下不會重傳NOP-only TLP包。通過上述FEC、CRC適配FBER=1E-6要求,同時保證出錯情況下重傳概率在5E-6、帶寬額外消耗約0.05%、FIT接近0。

互連通道與連接器

PCIe 5.0~6.0相比PCIe 1.0~4.0速率高,SI、PI要求也有提高。電源方面,插卡最大功耗可提升至600W,將在6.0 CEM中更新;信號方面為保證信號完整性要求使用表貼連接器;互連通道方面,與PCIe 5.0類似,要求主板支持約12 inch,插卡支持約3-4 inch,可以想象下,如果PCIe 6.0仍舊采用NRZ調制格式,64GT/s速率奈奎斯特頻點在32GHz,那么通道IL將小于-60dB(參考下圖通道仿真結果),很難通過現有技術實現該信號的高頻補償,考慮實現成本和技術復雜度,采用高階調制PAM4是種不錯選擇,相比PCIe 5.0奈奎斯特頻率不變,當前可用板材下可傳輸相似距離。

?不同信道插損仿真圖

PCIe6.0測試方案

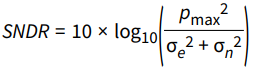

我們先來講一講物理層測試,PCIe6.0采用PAM4的調制方式,與前一代采用NRZ的PCIe 5.0相比,規范對發射端測試增加了全新的測試方法和參數要求,包括SNDR(信噪失真比),RLM-TX(發射端電平等級失配率)和基于PAM4的非相關總抖動、確定性抖動;為此,PCIe 6.0 Base spec v1.0定義了新的64GT/s的一致性測試碼型和抖動一致性測試碼型,有幾個要點需要注意:

1.

規范要求使用33GHz帶寬Bessel-Thomason濾波器頻響進行發射端一致性測試,對應示波器帶寬至少為50GHz,這里推薦UXR0504A示波器。

2.

計算SNDR

計算線性擬合脈沖響應p(k)和矢量誤差e(k),脈沖長度Np=600和脈沖延遲Dp=4,每個UI要有32個采樣點,允許重采樣,其中σn需要對一致性碼型中的4個電平各自的64個長符號中第61個UI進行測量和統計平均,每個UI內需要統計8個采樣點,等效為256GSa/s;

3.

測量需要考慮到示波器的底噪對測量結果影響,需移除示波器底噪對σn的貢獻,這要求示波器軟件能夠對4個電平各自的示波器底噪計算并校準,提供最佳的測試精度。

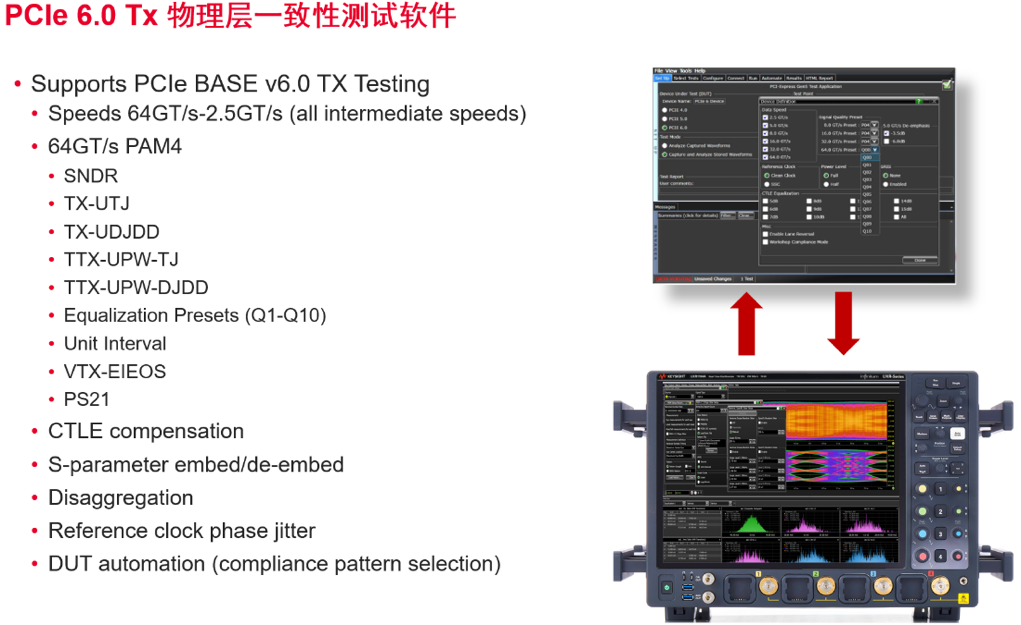

Keysight已經發布基于UXR示波器PCIe 6.0 Tx一致性測試軟件SW00PCIE或包含協議解碼功能的SW02PCIE,軟件內已集成上述PCIe 6.0規范要求的測試參數和算法。下圖為PCIe 6.0 Tx一致性測試軟件SW00PCIE所覆蓋的測試內容、功能和軟件界面。

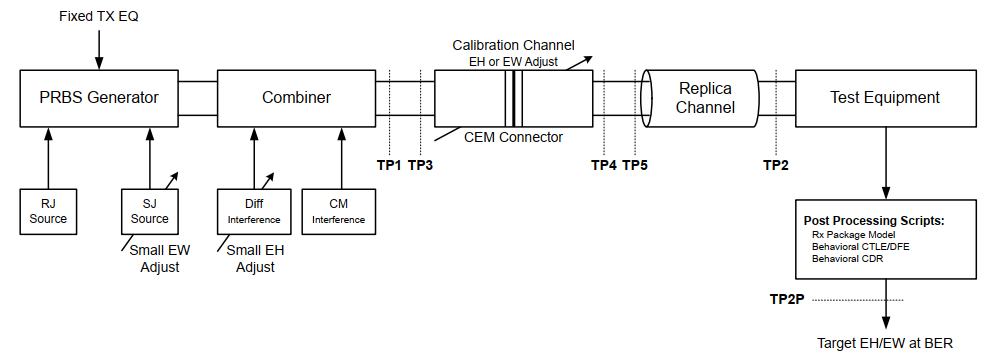

PCIe 6.0接收端一致性測試要求在如下圖的組網環境下進行校準,TP3到TP2P鏈路損耗調整范圍從30dB到33dB,從最大loss開始校準,Sj調整范圍1到3ps,DMI調整范圍5mv~25mV,目標Top Eye眼圖眼高和眼寬(1e-6)分別為6 mV +/- 0.5 mV, 3.125 ps +/- 0.3 ps.

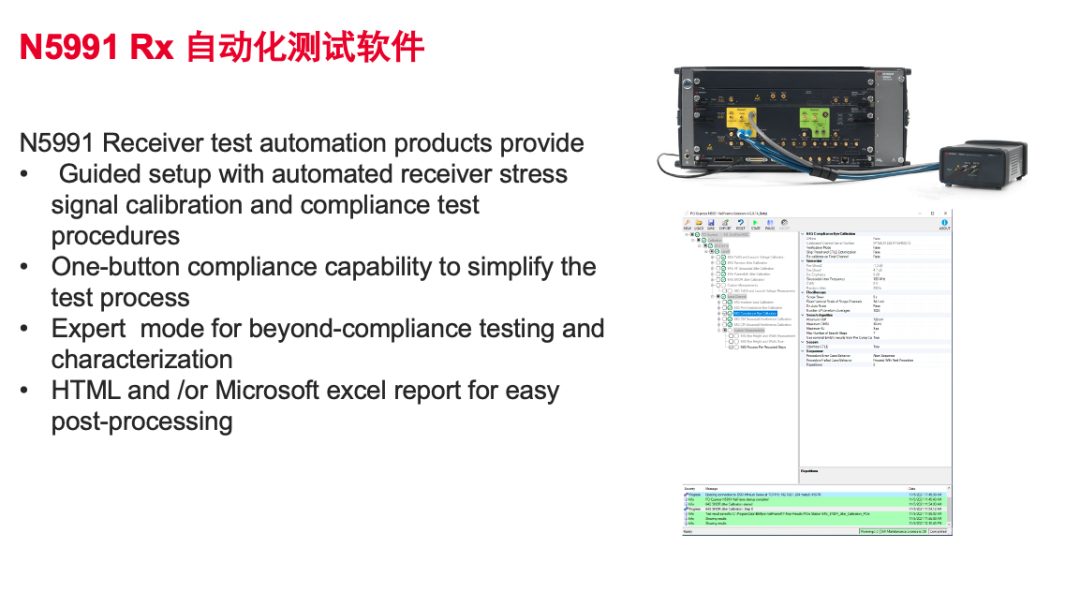

PCIe 6.0 Rx測試使用M8040A誤碼儀,它支持NRZ和PAM4信號產生和信號分析,可以向下兼容PCIe 1.1/2.0,對目前5.0 Rx測試的客戶有很好的擴展性,可以通過軟件許可的方式從NRZ升級PAM4選件支持PCIe 6.0,目前M8040A 分析儀模塊也支持PCIe 6.0 LTSSM選件M8046-0N1,可與PCIe 6.0被測件實現鏈路協商,完成Rx/Tx LEQ測試,另外M8040A也支持PAM3信號生成,可實現對USB4 v.2的支持,除了硬件之外,也有包括豐富的軟件方案支持對802.3CK、802.3BS以及CEI5.0/4.0的測試。N5991PB6A自動化軟件可以實現PCIe 6.0自動校準和接收一致性測試。

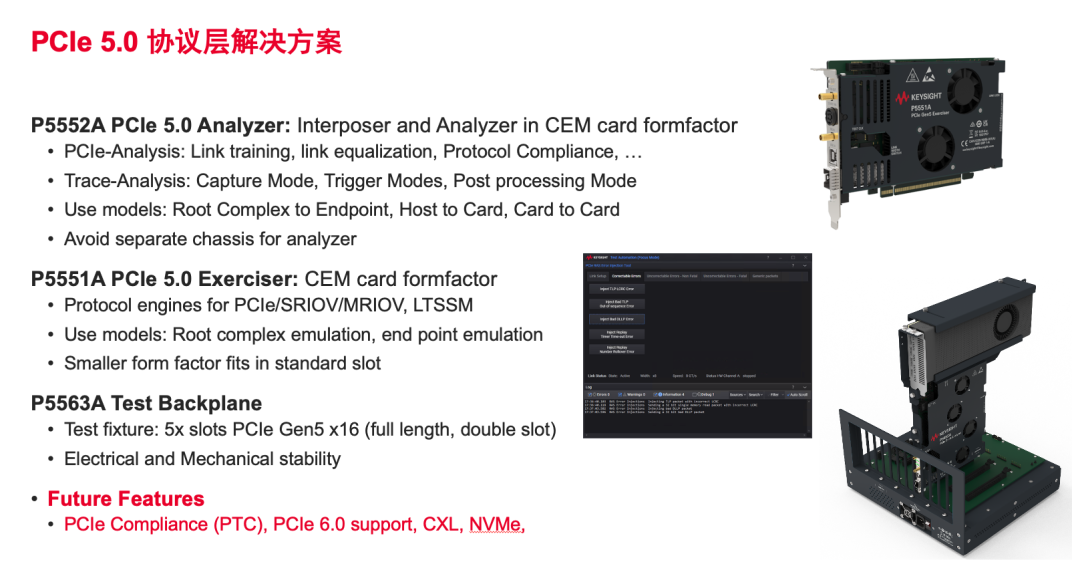

再來講講協議層的測試,芯片回片完成bring up,除基礎規范和物理電氣子層測試外,還需驗證邏輯子層LTSSM鏈路狀態機以及數據鏈路層、事務層等業務,這里需要使用協議分析儀或訓練器。當前已經發布了支持PCIe 5.0的P5551A和P5552A的訓練器和分析儀產品,由于PCIe 5.0和后續的6.0對于分析儀本身的信號完整性挑戰非常高,P5552A協議分析儀創新性地將PCIe 5.0采集與處理硬件和Interposer設計為一體,無需一堆外部長線纜將信號傳給主機處理,減少協議分析儀的欠補償或過補償問題。分析儀注重協議解析、鏈路監控及數據過濾等,訓練器重點在于模擬對端EP或RC完成數據通信、支持注錯和重播等,以及系統的RAS測試。未來也有計劃通過升級支持PCIe 6.0、CXL、NVMe等協議。

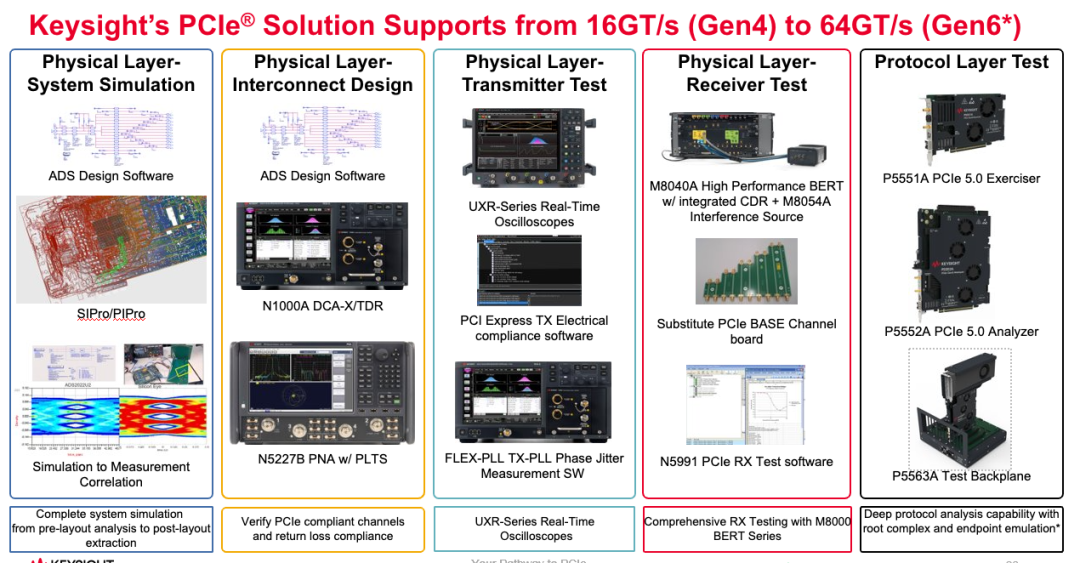

最后總結一下,?是德科技可以提供基于ADS仿真、PLTS信號測量、物理層收發、插卡環路帶寬分析及協議分析等綜合解決方案。

了解更多

更有好禮相送

保溫杯雨傘套裝

* 禮品圖片僅供參考,請以實物為準。請在填寫問卷時留下詳細地址,如遇地址不詳無法寄送,敬請諒解。

關于是德科技

點擊“閱讀原文”立即注冊

原文標題:干貨:PCIE6.0技術剖析

文章出處:【微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

-

是德科技

+關注

關注

20文章

879瀏覽量

81825

原文標題:干貨:PCIE6.0技術剖析

文章出處:【微信號:是德科技KEYSIGHT,微信公眾號:是德科技KEYSIGHT】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe 6.0 互操作性PHY驗證測試方案

4盤位U.2 NVMe SSD抽取盒如何通過MCIO接口打造高性能HPC解決方案

如何測試PCIe插槽的速度

PCIe 4.0與PCIe 3.0的性能對比

藍牙技術聯盟推出藍牙6.0核心規范

PCIe 5.0 SerDes 測試

美光研發出世界首款PCIe Gen6 SSD

如何簡化PCIe 6.0交換機的設計

干貨:PCIE6.0技術剖析

干貨:PCIE6.0技術剖析

評論