作者:Peter Delos and Michael Jones

本文詳細介紹了一種預測大型多通道系統中相位噪聲的系統方法,并將其與16通道S波段演示器的測量結果進行了比較。這種分析方法基于一小組測量值,可用于估計相關與不相關的噪聲貢獻。僅基于少量測量,就可以預測各種條件下的相位噪聲。該觀點認為,任何特定設計都需要自己的系統噪聲分析,16通道演示器提供特定的設計示例作為基礎。本文討論了基于16通道演示器的假設,以及隨著系統復雜性的增加,何時適用這些假設以及何時添加額外噪聲項的限制。所提供的描述基于描述RF系統中相位噪聲優化的一系列工作。1–6在適當的情況下,提供了描述本分析中使用的基本原則的參考資料。

介紹

相位噪聲是所有RF系統設計中的關鍵性能指標。在通道相干組合的大型多通道RF系統中,例如相控陣,一個目標是通過分布式接收器和發射器的相干組合實現陣列級動態范圍的改進。實現此目標的系統工程挑戰是考慮系統中既相關又不相關的噪聲項。本文旨在通過介紹一種用于估計16通道RF演示器相位噪聲的系統方法,幫助系統工程師開發分析方法來估計大型系統的噪聲性能。

相控陣中的任何信號都將包含跨通道不相關的噪聲項和跨通道相關的噪聲項。分布式組件的加性噪聲是不相關的。但是,用于分布式組件的共享信號會產生相關的噪聲分量。挑戰在于如何快速可視化架構中的相關噪聲項。任何常見或共享的內容都可能導致跨通道的相關噪聲。示例包括共享 LO、時鐘或電源。隨著系統復雜性的增加,跟蹤這些噪聲項變得非常麻煩。因此,從噪聲角度重新繪制架構并快速識別相關噪聲貢獻者的直觀方法,對于構建下一代系統的系統工程師是有益的。

在本文中,我們演示了一種使用16通道S波段系統的方法,并表明只需幾次經驗測量,就可以很好地預測各種其他通道組合條件下的相位噪聲。這個經驗模型的關鍵點之一是需要一些測量。從組件仿真直接到具有良好精度的大型多通道相位噪聲估計可能很困難。但是,只需進行少量測量,就可以提取相關和不相關的噪聲項,從而使多通道估計非常準確。我們的測量結果與 16 通道 S 波段演示器的預測值在 1 dB 以內相匹配。

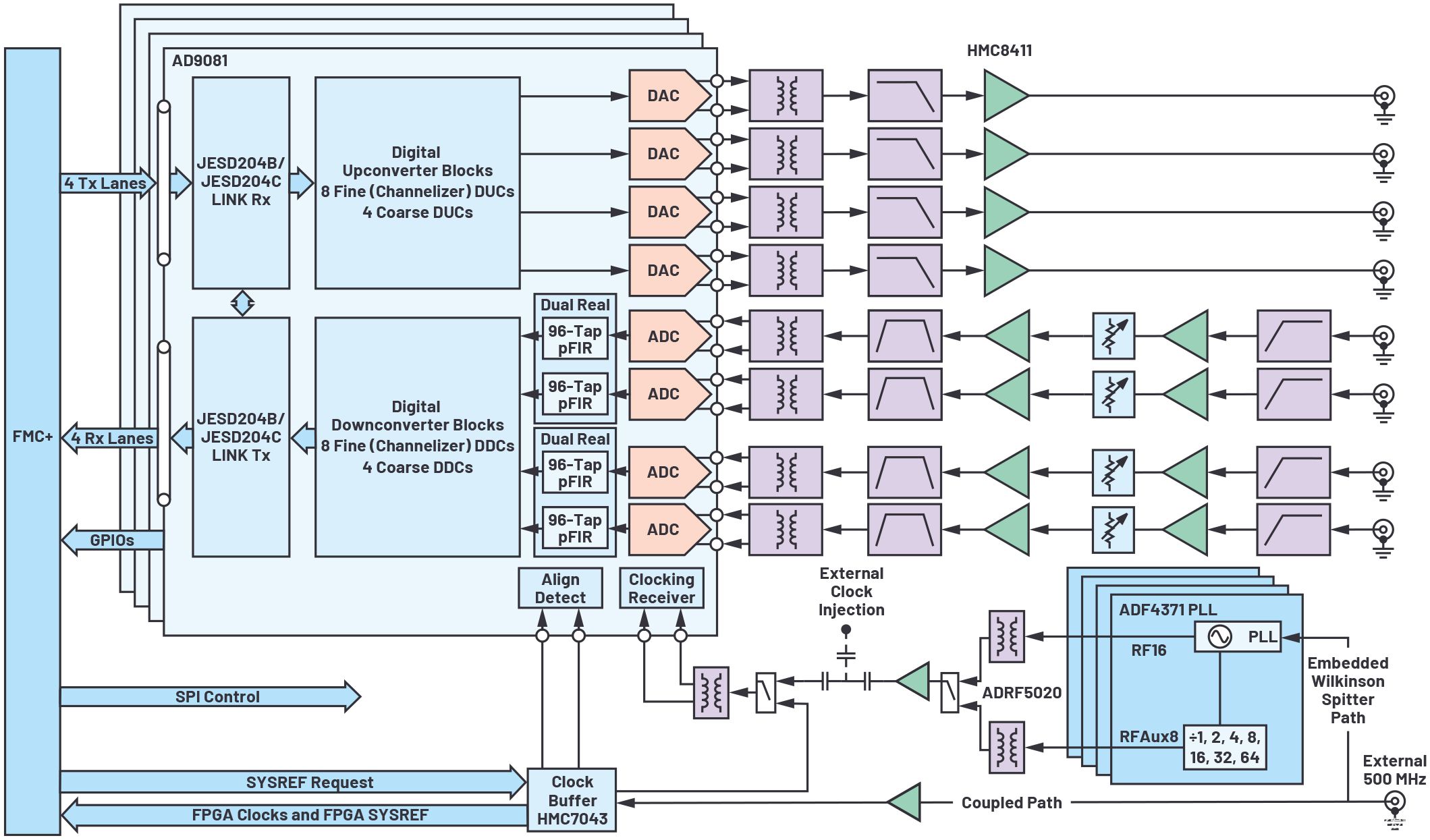

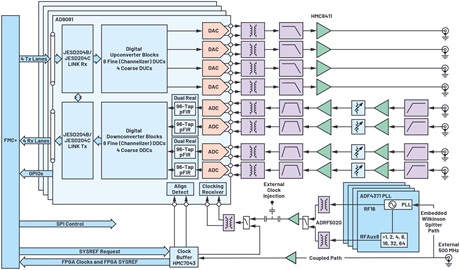

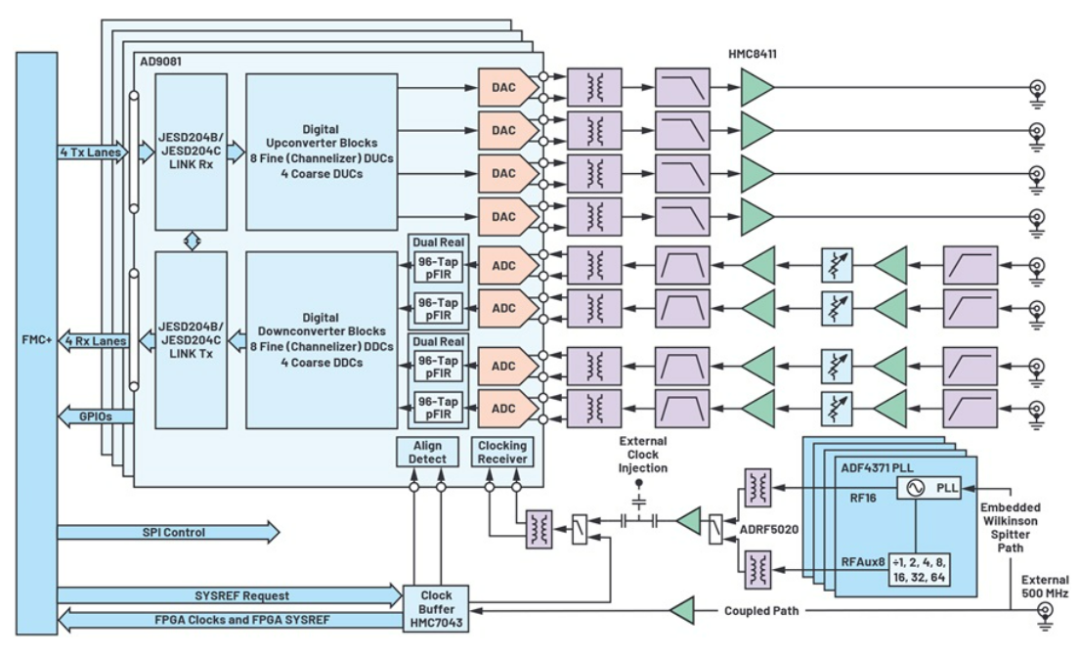

圖1.16通道演示器:該平臺包含4個AD9081 IC。每個AD9081包含4個RF DAC和4個RF ADC,總共提供16個發射通道和16個接收通道。

對相關噪聲和不相關噪聲求和的背景

當信號在自由空間或RF處理中組合時,每個信號的噪聲增加為

其中 c 是相關系數,范圍從 –1 到 +1。如果 c = –1,則噪聲抵消;如果 c = 0,則噪聲不相關;如果c = 1,則噪聲完全相關。

假設有一個校準來相干地組合主信號,主信號將以20logN的水平增加,其中N是通道數。

如果噪聲項不相關(c = 0),則噪聲將增加10logN。隨著信號電平以20logN速率增加(速率比噪聲高10logN),由此產生的SNR改善為10logN。

如果噪聲項相關(c = 1),則噪聲也會以20logN的速率增加,與信號相同,并且不會有SNR改善。對于分布式系統,這不是一個理想的結果。

在降噪電路中,會產生負相關系數。為了公式1,本文對此進行了說明,但不再進一步描述。

實際上,大型分布式系統的噪聲分量在通道之間部分相關。然而,需要一種實用且直觀的方法來開發系統級噪聲模型。

16通道演示器

開發了一個16通道直接S波段RF采樣平臺,用于在多通道環境中評估最新的高速數據轉換器。該平臺包含四個AD9081 MxFE(混合信號前端)IC。每個AD9081包含4個RF DAC和4個RF ADC,總共提供16個發射通道和16個接收通道。?

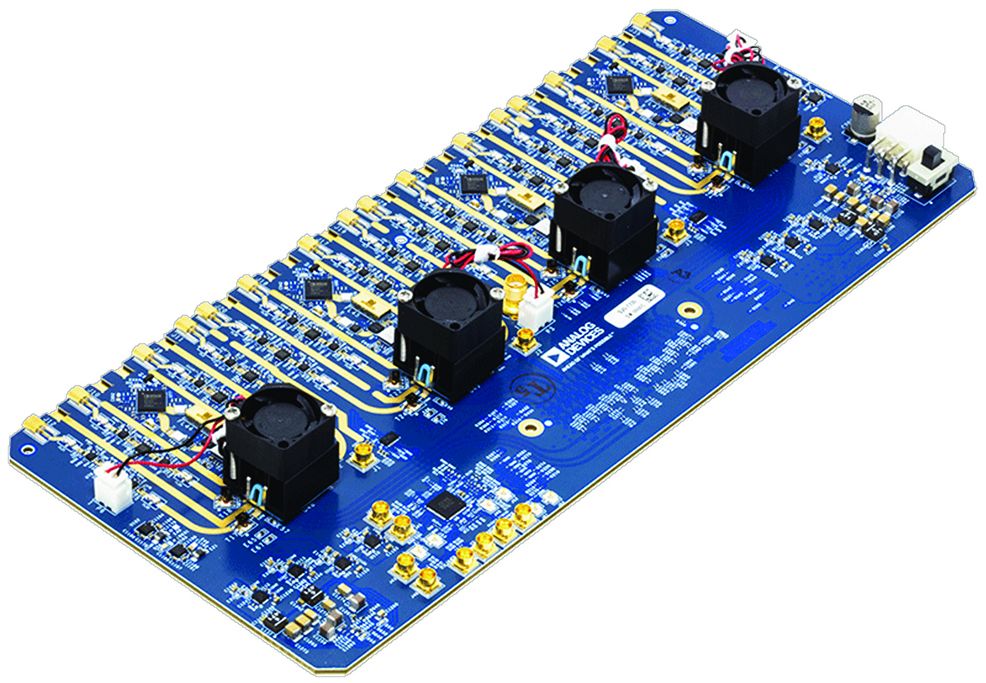

該 16 通道評估平臺因其四個 MxFE IC 而被命名為 Quad-MxFE。整體框圖和電路板照片分別如圖1和圖2所示。

圖2.Quad-MxFE是一款16通道演示器。

多通道相位噪聲模型

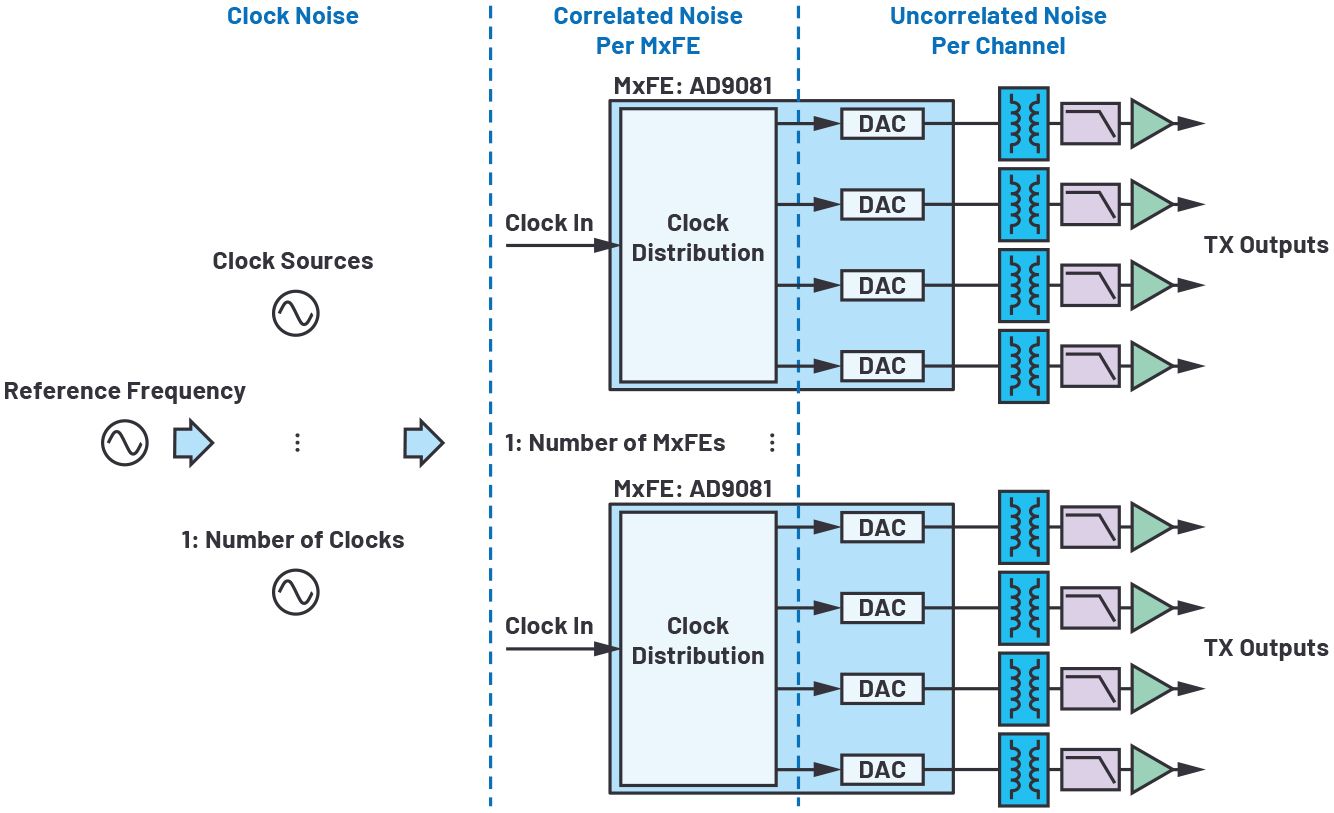

圖 1 中的 16 通道開發平臺框圖顯示了功能范圍。從此圖中,最初并不明顯如何根據相關與不相關的噪聲分量來可視化噪聲貢獻者。需要一種方法從噪聲的角度考慮架構。適當的草圖可以闡明所有通道中通用的噪聲項、僅在通道組之間相關的噪聲項以及跨通道完全不相關的噪聲項。圖3顯示了16通道開發平臺,并將噪聲項分為三類。

圖3.圖1從時鐘相位噪聲角度重繪。

時鐘噪聲:四通道 MxFE 提供多種時鐘配置選項。在相位噪聲模型中需要考慮所使用的特定配置。在我們的測試中,我們在所有通道上使用一個通用的低相位噪聲時鐘,或者使用四個獨立的分布式ADF4371鎖相環(PLL)頻率合成器作為四個MxFE中每個頻率的時鐘輸入。對于單個公共時鐘,該噪聲將與所有16個組合通道相關。對于使用四個ADF4371 PLL(每個MxFE一個)的情況,PLL噪聲將每個MxFE相關,但在MxFE之間不相關,而參考噪聲將在所有通道中相關。

Peter Delos的文章“具有分布式鎖相環的相控陣的系統級LO相位噪聲模型”總結了處理分布式鎖相環的分析方法。本基準電壓源中的分析方法考慮了參考頻率、配電系統和PLL電路的噪聲成分,并考慮了PLL環路帶寬效應。

每個 MxFE 的相關噪聲:這是來自 MxFE 的噪聲,與 MxFE 中的每個通道相關。對于此分析,每個MxFE的相關噪聲包括IC內常見的加性噪聲以及IC內通道常見的任何電源效應。

每個通道的不相關噪聲:這是每個通道不同的噪聲。它包括DAC內核和所有放大器殘余相位噪聲。在公式2中,該術語被注釋為TXNoise。

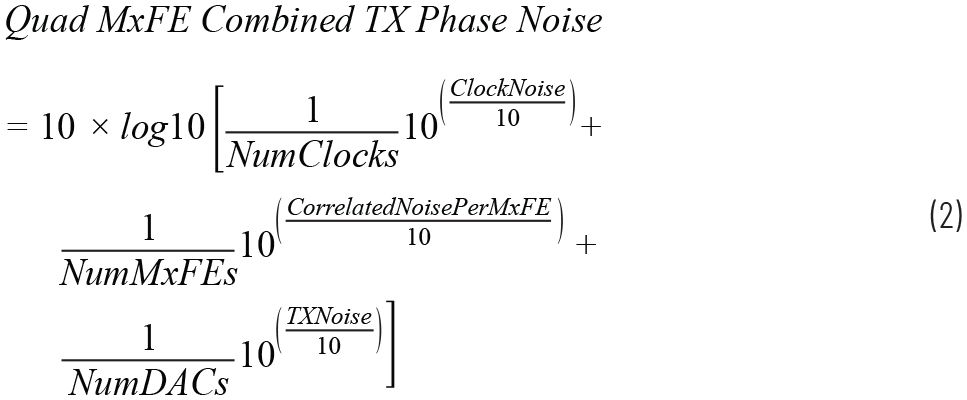

根據所述貢獻因素的相位噪聲,組合相位噪聲可以計算如下。

接下來,還有一些其他細節,允許將模型簡化為此測試平臺的這種形式。

電源效應:電源相位噪聲貢獻是低相位噪聲設計中的一個重要考慮因素。文章“電源調制比揭秘:PSMR與PSRR有何不同?”和“改進的DAC相位噪聲測量可實現超低相位噪聲DDS應用”中介紹了解決電源噪聲問題的方法。對于本文的分析,電源效應被認為是公式2中噪聲項的一個子集。如果電源噪聲是IC的主要相位噪聲貢獻因素,并且跨通道共享,則需要將這種影響視為一個相關術語,類似于本文前面使用的每MxFE的相關噪聲。

參考振蕩器噪聲:在大型系統中,參考振蕩器噪聲貢獻需要按照文章“具有分布式鎖相環的相控陣的系統級LO相位噪聲模型”中所述進行分配。在該測試平臺中,使用了非常低的相位噪聲基準,該基準電壓源遠低于其他貢獻因素,并且在組合噪聲方程中沒有特別指出。

用于通知模型的測量

使用公式2中描述的組合相位噪聲模型,下一個問題是“我們如何得出方程中使用的噪聲貢獻值?對于 Quad-MxFE 測試臺,可以使用三種測量來提取所需的信息:

時鐘源的絕對相位噪聲

來自不同 MxFE 的通道的殘余相位噪聲

來自同一 MxFE 的通道的殘余相位噪聲

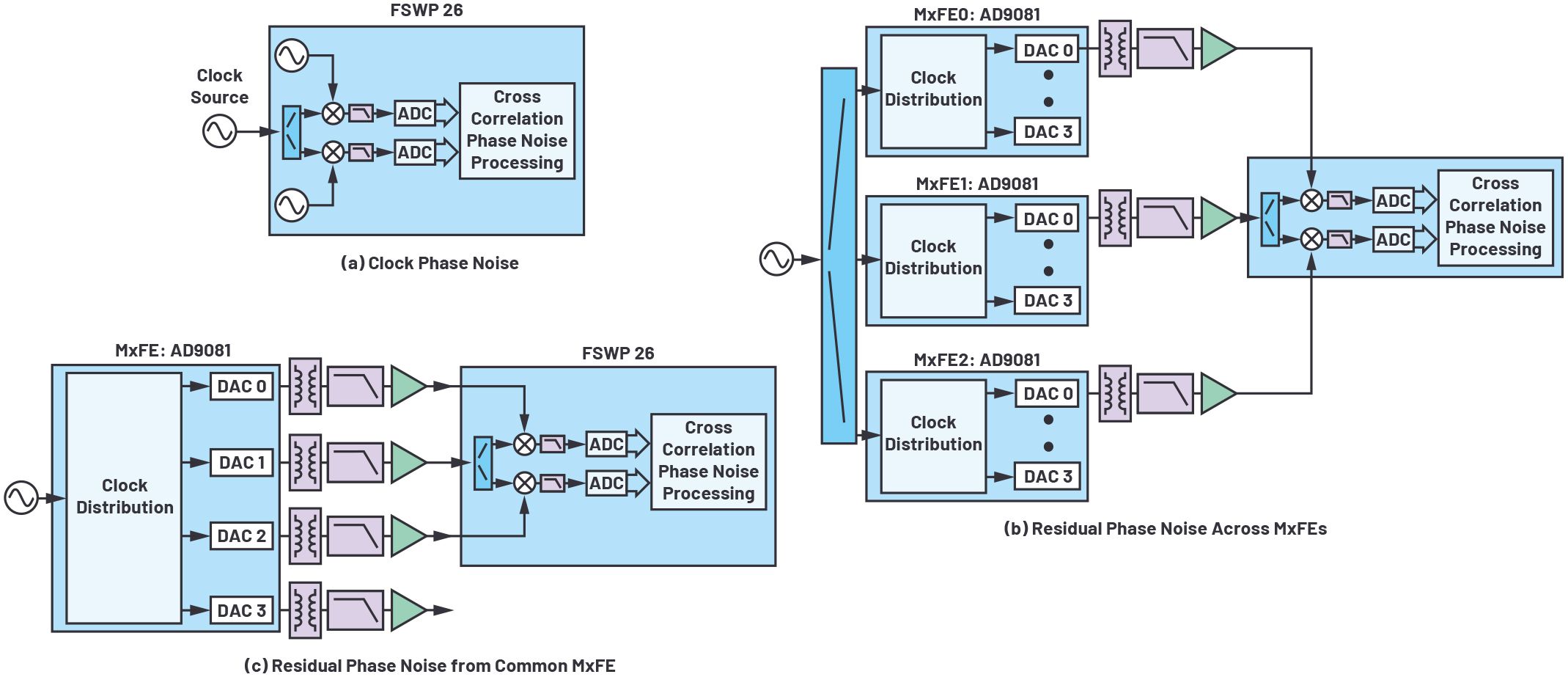

與測量一起使用的測試設置如圖4所示。圖4(b)和圖4(c)均提供消除公共時鐘源的殘余噪聲測量。當測量單個MxFE內的殘余相位噪聲時,MxFE內跨通道的相關噪聲也會被抵消。但是,當測量MxFE上的殘余相位噪聲時,測量中會捕獲MxFE中的相關噪聲。

圖4.使用三種測量來告知相位噪聲模型。

最后一步是將測量數據修改為公式2的三個項,如下所示:

時鐘噪聲 = 時鐘相位噪聲測量(圖 4(a))+ 20log(F外/FCLOCK)

每個 MxFE 的相關噪聲 = MxFE 上的殘余相位噪聲(圖 4(b)) – 來自公共 MxFE 的殘余相位噪聲(圖 4(c))。請注意,對于此計算,您需要轉換為線性功率,然后減去,然后轉換回dB,使得10log(10^(MxFEs/10的殘余相位噪聲)– 10^(來自公共MxFE/10的殘余相位噪聲))

Tx噪聲 = 來自公共 MxFE 的殘余相位噪聲(圖 4(c))。

關于殘余相位噪聲測量的補充說明:我們發現,通過該硬件,上述項目2和3的噪聲項也隨頻率而變化。當轉換為其他頻率時,額外的20log(F外/F多邊環境協定) 是必需的。并非所有硬件都如此,應針對每個設計獨立評估此術語。

測量案例1:普通低相位噪聲時鐘

對于此測量,整個16通道演示器使用單個低噪聲12 GHz時鐘。時鐘源是SMA100B,注入到圖1所示的外部時鐘注入節點中。所示條件適用于 3.2 GHz 發射輸出頻率。

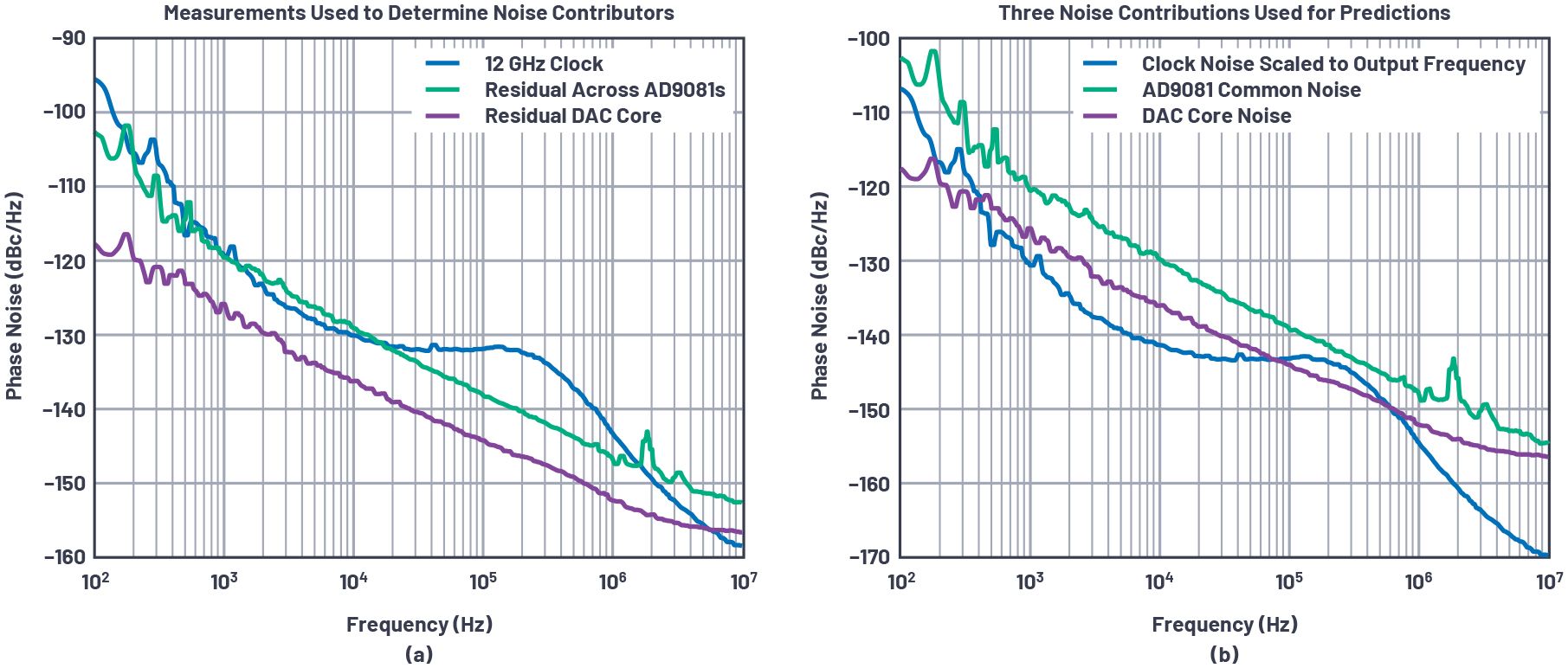

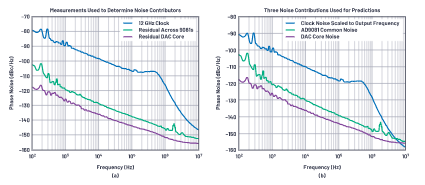

從圖5(b)中,我們看到MxFE之間的相關噪聲是最大的貢獻者。隨著系統中MxFE的增加,這種噪聲貢獻將得到改善,然后受到公共時鐘噪聲的限制。對于每個貢獻者的曲線形狀,僅沿曲線添加幾個點不足以進行準確的預測,因此我們發現最好直接在公式2中使用圖5(b)中的數據。接下來,進行了一系列測量以驗證模型。該模型以驚人的準確性預測結果,在查看圖 6 到圖 8 后可以觀察到。

圖5.a) 為告知相位噪聲模型而進行的測量,以及 b) 計算出要在模型中使用的相位噪聲貢獻者。這適用于所有 MxFE 的單個公共時鐘的情況。

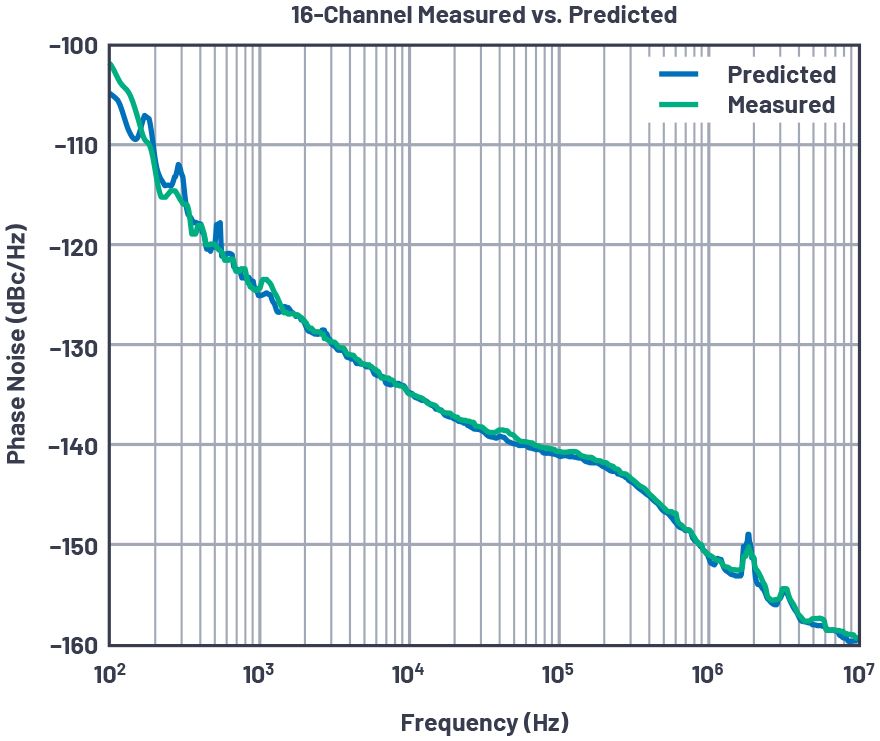

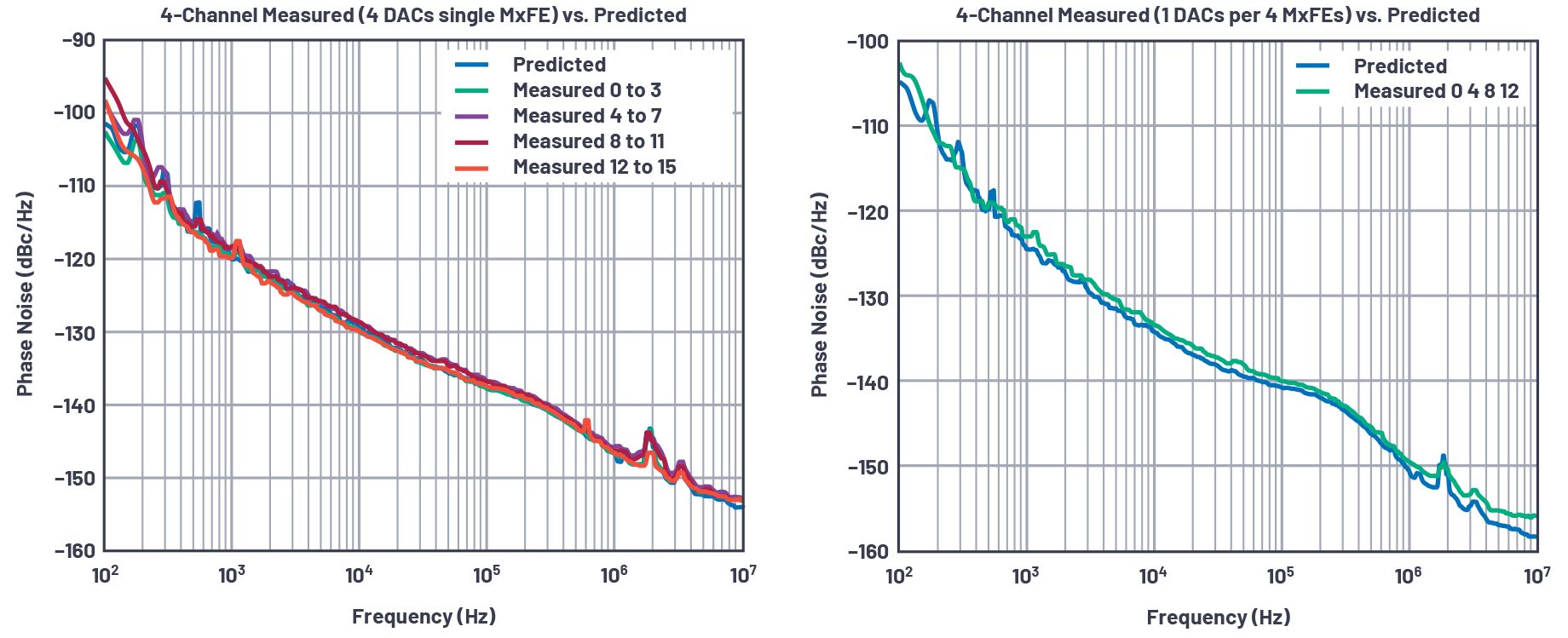

圖6.3.2 GHz 下 16 個通道的測量與模型預測。

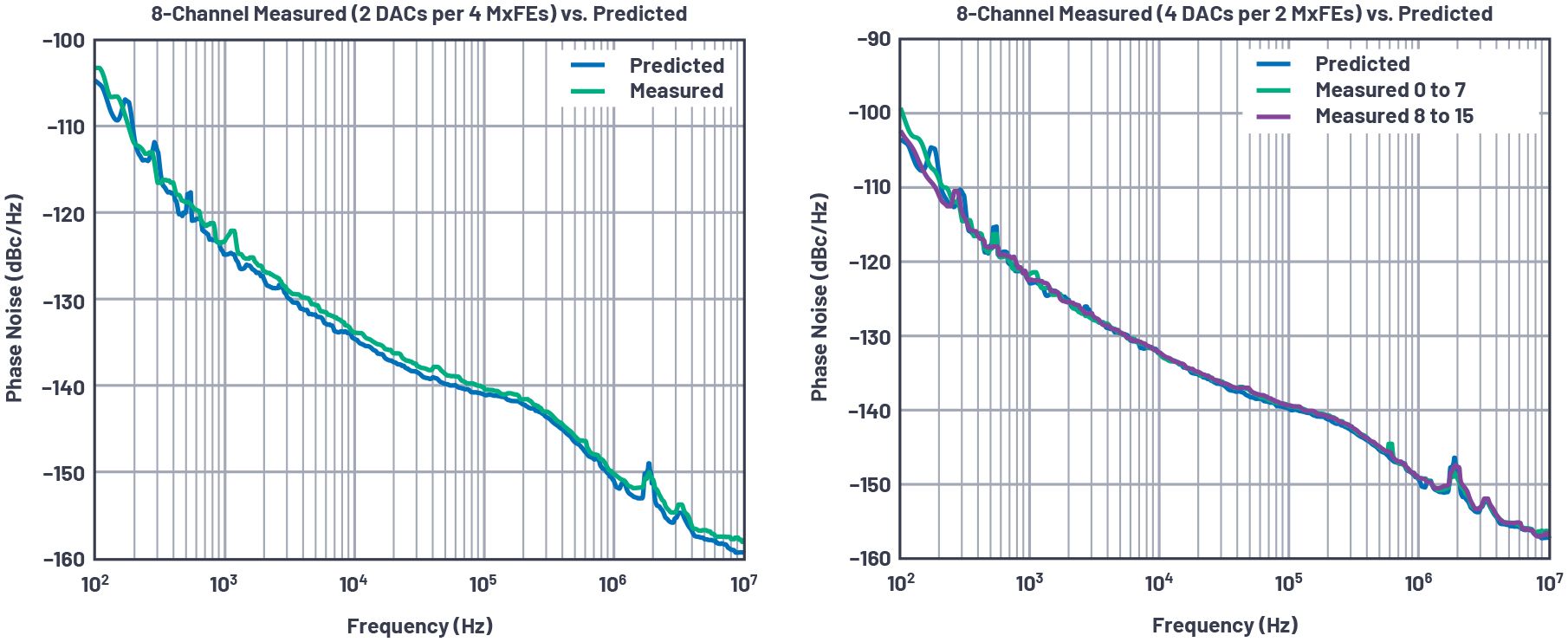

圖7.3.2 GHz 下八個通道的測量與模型預測。兩個圖中的區別在于發射通道如何在 MxFE 之間共享。

圖8.3.2 GHz 下四個通道的測量與模型預測。兩個圖中的區別在于發射通道如何在 MxFE 之間共享。

關于測量與預測的一些觀察值得注意。在許多情況下,預測與測量值幾乎相同。在某些情況下,測量值與預測值略有下降。我們在這里承認這一點,但沒有確切的描述。圖 8 中的左圖提供了一個潛在指標。放大這些圖時,我們注意到預測與兩個測量事例匹配,并且兩個實測事例略高。AD9081 IC中每個MxFE的相關噪聲可能不相同,從而導致一些差異。第五節所述的一些簡化假設可能是一個促成因素。無論哪種情況,預測都非常準確,我們認為該方法針對這種特定設計進行了驗證。

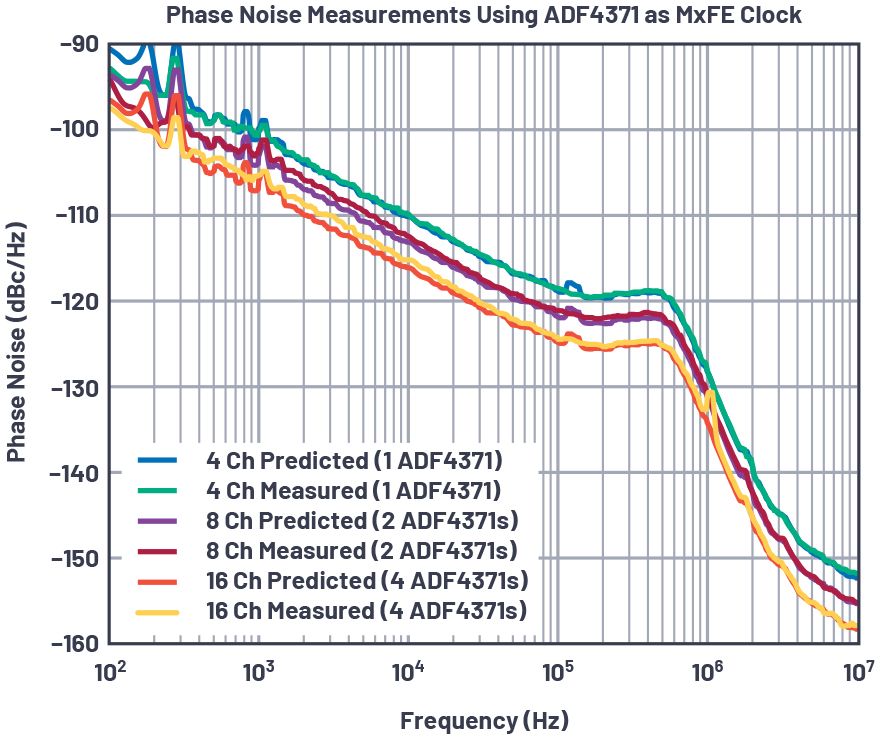

測量案例 2:每個 MxFE 的分布式 PLL

對于此測量,四個MxFE中的每一個都使用單獨的ADF4371,如圖1所示。ADF4371鎖相至低相位噪聲500 MHz基準電壓源,并針對12 GHz輸出進行編程。圖9顯示了用于通知模型的測量值和噪聲因素。

圖9.a) 使用單獨的ADF4371芯片作為時鐘輸入源時為告知相位噪聲模型而進行的測量,以及 b) 計算出要在模型中使用的相位噪聲貢獻因素。這適用于每個 MxFE 的分布式 PLL 的情況。

在這種情況下,PLL是主要的噪聲源,而MxFE噪聲貢獻因素遠低于時鐘噪聲。組合噪聲根據分布式系統中使用的PLL數量而改善,如圖10所示。

圖 10.使用ADF4371作為每個MxFE的時鐘源時,組合各種相位對齊發射通道后,在3.2 GHz下測量與建模預測。

結論

本文展示了一個經驗模型,該模型可以非常準確地預測組合通道的相位噪聲。該方法的前提是首先從噪聲源的角度查看系統,然后重新繪制框圖,以便輕松查看相關項和不相關項。

我們還強調“經驗”一詞,這意味著所提出的方法可以通過觀察或經驗而不是理論或純邏輯來驗證。對于相位噪聲的情況,需要一些測量和觀察來評估趨勢和貢獻因素。一旦了解了這些,就可以系統地計算系統噪聲。

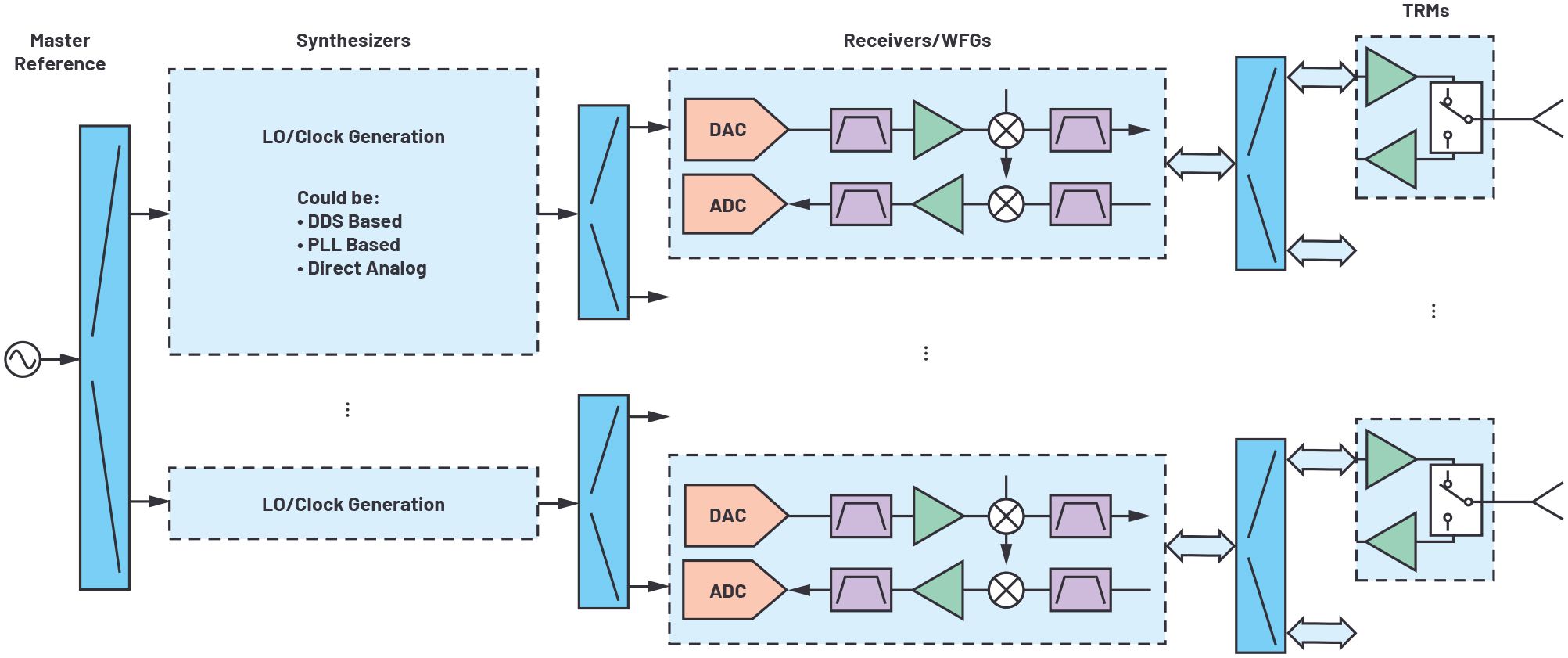

本文中使用的數據和方程式在某種程度上特定于硬件,并基于前面描述的觀察結果。但是,該方法可以擴展到任何多通道系統。更通用的框圖如圖 11 所示。從系統參考振蕩器開始,然后繪制時鐘和LO分布以及通道級硬件,就可以更直接地可視化大型系統中的噪聲貢獻因素。

圖 11.從相位噪聲角度看廣義相控陣圖。每個信號都包含噪聲項,這些項是分布在整個陣列中的噪聲分量的組合。通過從這個角度重繪系統,可以更輕松地在系統級別可視化相關噪聲與不相關噪聲的跟蹤。如果設計人員從系統參考振蕩器開始,繪制時鐘和LO分布以及通道級硬件,那么在大型系統中可視化噪聲貢獻因素會更加簡單。

審核編輯:郭婷

-

接收器

+關注

關注

14文章

2475瀏覽量

72043 -

發射器

+關注

關注

6文章

852瀏覽量

53542 -

RF

+關注

關注

65文章

3056瀏覽量

167167

發布評論請先 登錄

相關推薦

16通道間隔離型模擬輸入解決方案

用于LTC2373CUH-18的18位1Msps 8通道演示板

用于LTC2373CUH-16的16位1Msps 8通道SAR ADC的演示板

CW01DB1,演示板使用CW01K6 4通道,低相位噪聲,低功耗,連續波發射器

演示電路1199A是采用LT3595EUHH的16通道降壓模式LED驅動器

多通道RF到位開發平臺可實現相控陣的快速原型設計

四通道16位電壓/電流輸出DAC節省多通道PLC的空間、成本和功耗

擴展電網應用中的模擬輸入通道(使用16通道、16位、1MSPS雙路同步采樣ADC)

在16通道演示器中驗證的基于經驗的多通道相位噪聲模型

在16通道演示器中驗證的基于經驗的多通道相位噪聲模型

評論