先進封裝行業概覽

封裝是指將生產加工后的晶圓進行切割、焊線塑封,使電路與外部器件實現連接,并為半導體產品提供機械保護,使其免受物理、化學等環境因素損失的工藝。

隨著半導體先進制程不斷往7nm/5nm,甚至以下邁進,晶片設計與制造工藝微縮的難度、成本與開發時間均呈現跳躍式的增長。

面對此難題,晶片業者試圖透過先進封裝來達到晶片間的高密度互聯,以實現以更低成本提供同等級效能表現。

先進封裝采用了先進的設計思路和先進的集成工藝,對芯片進行封裝級重構,并且能有效提升系統高功能密度的封裝技術。

先進封裝工藝包括倒裝焊(FlipChip)、晶圓級封裝(WLP)、2.5D封裝(Interposer) 、3D封裝 (TSV)、Chiplet等。

據 Yole 數據,2021 年全球封裝市場規模約達 777 億美元。其中,先進封裝全球市場規模約 350 億美元。

預計到 2025年先進封裝的全球市場規模將達到 420 億美元,2019-2025 年全球先進封裝市場的 CAGR 約 8%。

相比同期整體封裝市場 (CAGR=5%)和傳統封裝市場,先進封裝市場增速更為顯著。

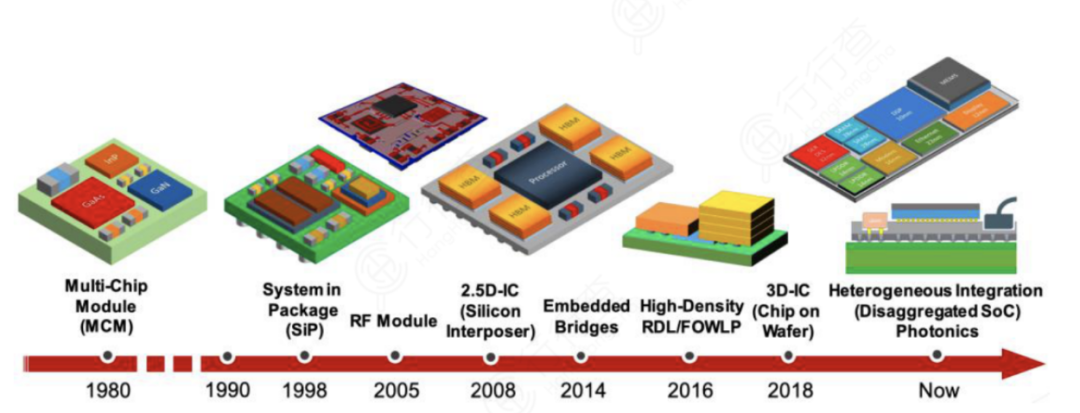

芯片整合已演進至2.5D/3D及Chiplet封裝:

Chiplet 行業概覽

隨著半導體制程節點的持續演進,短溝道效應以及量子隧穿效應帶來的發熱、漏電等問題愈發嚴重,追求經濟效能的摩爾定律日趨放緩。

在此背景下,產業開始思考將不同工藝的模塊化芯片。

Chiplet又稱芯粒或小芯片,是先進封裝技術的代表,將復雜芯片拆解成一組具有單獨功能的小芯片單元 die(裸片),通過 die-to-die 將模塊芯片和底層基礎芯片封裝組合在一起。

Chiplet 實現原理與搭積木相仿,從設計時就按照不同的計算單元或功能單元對其進行分解,然后每個單元選擇最適合的工藝制程進行制造,再將這些模塊化的裸片互聯起來,通過先進封裝技術,將不同功能、不同工藝制造的Chiplet封裝成一個系統芯片,以實現一種新形式的 IP 復用。

Chiplet 的概念源于 Marvell 創始人周秀文博士在 ISSCC 2015 上提出的 Mochi(Modular Chip,模塊化芯片)架構,伴隨著 AMD 第一個將小芯片架構引入其最初的 Epyc 處理器 Naples,Chiplet 技術快速發展。

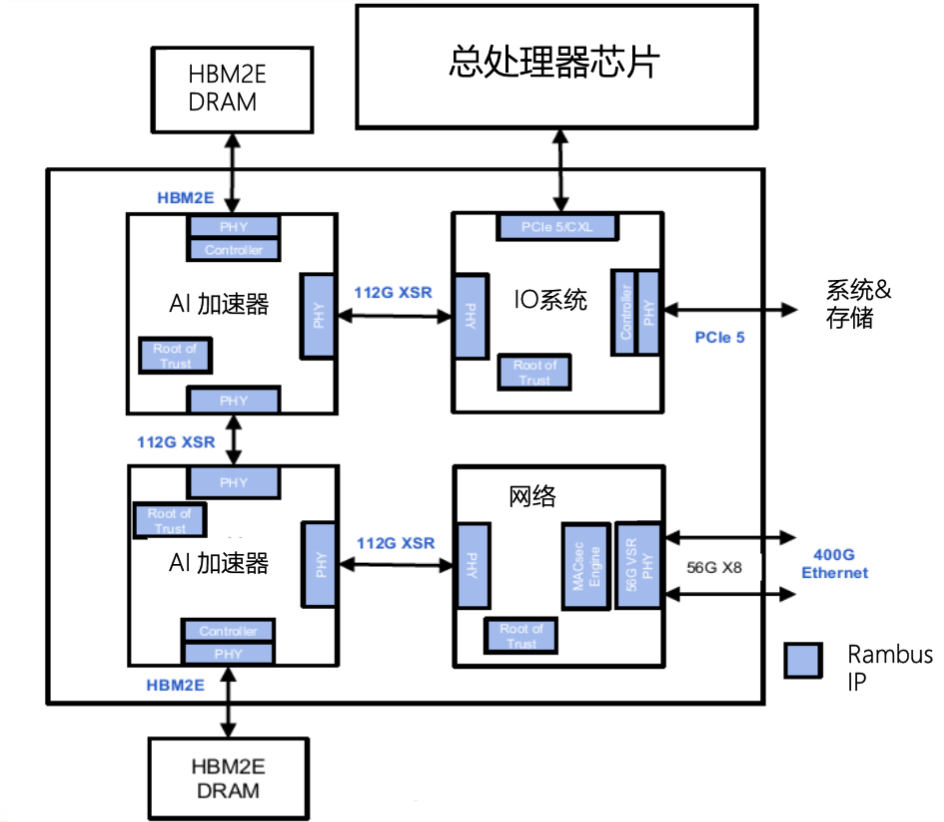

基于Chiplet 的異構架構應用處理器:

通過Chiplet技術,使用10nm工藝制造出來的芯片,完全也可以達到7nm芯片的集成度,但是研發投入和一次性生產投入則比7nm芯片的投入要少的多,新的連接形式在其生產過程中帶動設備需求。

Chiplets結構:

資料來源:Omdia,Rambus,方正證券

Chiplet模式具備開發周期短、設計靈活性強、設計成本低和良率高等優點。可將不同工藝節點、材質、功能、供應商的具有特定功能的商業化裸片集中封裝。

其作用主要包括:降低單片晶圓集成工藝良率風險,達到成本可控,有設計彈性,可實現芯片定制化;Chiplet將大尺寸的多核心的設計,分散到較小的小芯片,更能滿足現今高效能運算處理器的需求;彈性的設計方式不僅提升靈活性,且可實現包括模塊組裝、芯片網絡、異構系統與元件集成四個方面的功能。

資料來源:來源:CEIA電子制造

Chiplet 市場格局

目前Chiplet已經有少量商業應用,并吸引英特爾和AMD等國際芯片廠商投入相關研發,在當前SoC遭遇工藝節點和成本瓶頸的情況下有望發展成為一種新的芯片生態。

隨著 Chiplet 逐步發展,未來來自不同廠商的芯粒之間的互聯需求持續提升。

2022年3月,Chiplet的高速互聯標準——UCIe(UniversalChiplet Interconnect Express,通用芯粒互聯技術)正式推出,旨在芯片封裝層面確立互聯 互通的統一標準,打造一個開放 性的 Chiplet 生態系統。在解決Chiplet 標準化方面具有劃時代意義。

UCIe聯盟為Chiplet制定了多種先進封裝技術,包括英特爾EMIB、臺積電CoWoS、日月光FoCoS-B等。

UCle發起人為 Intel、AMD、ARM、高通、三星、臺 積電、日月光、Google Cloud、Meta 和微軟等十家公司。

UCIe聯盟致力于推行Chiplet互聯規范,當前聯盟成員包括Synopsys、Cadence、ADI、博通等國際龍頭。

對于中國半導體而言,后摩爾時代 Chiplet 是中國與國外技術差距相對較小的封裝技術領域。

國內企業緊跟產業趨勢,積極參與融入UCIe大生態,有望在Chiplet行業技術上乘勢而上,實現突破。

國內企業中,芯原微電子、超摩科技、芯和半導體、芯耀輝、摩爾精英、燦芯半導體、憶芯科 技、芯耀輝、牛芯半導體、芯云凌、長鑫存儲、超摩科技、希姆計算、世芯電子、阿里巴巴、OPPO、愛普科技、芯動科技、藍洋智能等多家國內企業已成為 UCIe 聯盟成員。

資料來源:UCle、招商證券

Chiplet開啟了IP新型復用模式

Chiplet的實現開啟了IP的新型復用模式,即硅片級別的IP復用。

不同功能的IP,如CPU、存儲器、模擬接口等,可靈活選擇不同的工藝分別進行生產,從而可以靈活平衡計算性能與成本,實現功能模塊的最優配置而不必受限于晶圓廠工藝。

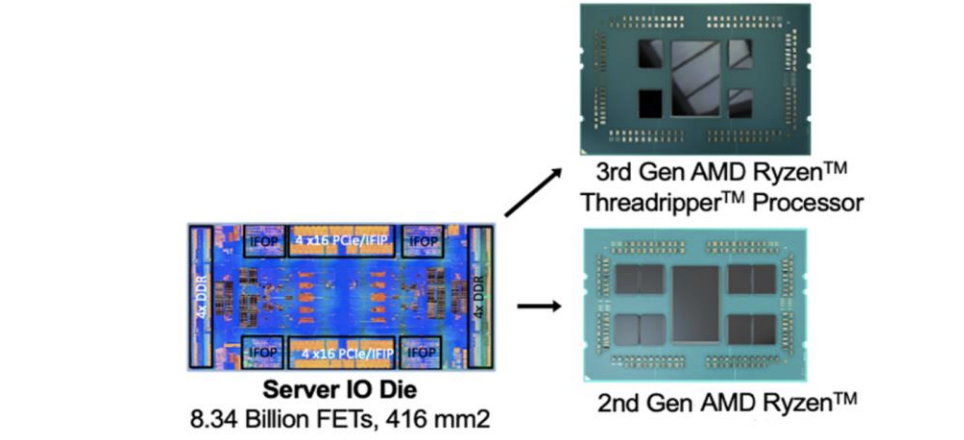

AMD 公司是第一個引入小芯片架構的供應商。AMD 在第三代銳龍(Ryzen)處理器上復 用了第二代霄龍(EPYC)處理器的 IO Chiplet,這種復用不但可以將“老舊制程”生 產的 Chiplet 繼續應用到下一代產品中以節約成本,更能極大地節約設計、驗證和生 產周期并降低失敗風險。 AMD IO Chiplet 的復用:

就Chiplet和半導體IP的聯系而言,Chiplet可以被看作是半導體IP經過設計和制程優化后的硬件化產品,其業務形成也從半導體IP的軟件形式轉向到Chiplet的硬件形式。

半導體IP的市場參與者可大致分為兩類:新思科技和Cadence是與EDA工具捆綁型的半導體IP供應商,生態鏈優勢明顯;其余是在細分領域提供專業的IP核廠商。

當前IP市場仍然被英美國家高度壟斷,全球前3廠商是Arm(英國)、Synopsys(美國)和Cadence(美國)。SST憑借著嵌入式非揮發性存儲器異軍突起,現在已經排到了全球第四。

國內芯原股份在全球前七名半導體IP授權供應商中,IP種類的齊備程度也具有較強競爭力。芯原股份是國內領先的一站式芯片定制服務和半導體 IP 授權服務的企業,利用 Chiplet 技術進行 IP 芯片化,有望給公司帶來全新商業模式。

國內產業鏈相關廠商也在積極布局。

通富微電在先進封裝方面公司已大規模生產 Chiplet 產品,7nm 產品已大規模量產,5nm 產品已完成研發即將量產。長電科技是國內封裝 測試龍頭企業,重點發展系統級(SiP)、晶圓級和 2.5D/3D 等先進封裝 技術,并實現大規模生產。

長川科技是國內領先的集成電路測試設備企業, Chiplet 芯粒的測試與先進封裝將為公司帶來新機遇。華峰測控是國內領 先的集成電路測試設備企業,同樣受益于 Chiplet 芯粒測試與先進封裝帶來的機遇。

興森科技是國內 IC 封裝基板領先企業,在應用 Chiplet 技術的先進封 裝材料領域有望持續拓展。華大九天Chiplet 技術的應用需要 EDA 工具 的全面支持,作為國內 EDA 龍頭,有望在 Chiplet 領域進行拓展。

寒武紀2022年3月30日回復稱思元370是寒武紀首款采用chiplet(芯粒)技術的AI芯片,采用7nm制程工藝,最大算力高達256TOPS(INT8),是寒武紀第二代產品思元270算力的2倍。

摩爾定律減緩帶來了小芯片的設計需求,性能提升、成本降低以及大芯片的缺陷問題是 Chiplet 設計成為趨勢的三大推動因素。

總體來看,Chiplet是后摩爾時代實現性能與成本突破的最優解,國外各大廠商持續布局。

根據研究機構 Omdia 報告,2024年采用Chiplet的處理器芯片的全球市場規模將達 58 億美元,到 2035 年將達到570億美元。

Chiplet作為目前受到廣泛關注的新技術,給全球和中國的半導體市場帶來了產業變革與機遇,降低了芯片設計門檻,帶動IP設計廠商轉換為Chiplet供應商,并且推動了先進封裝、測試環節的需求。

半導體封測行業發展歷史

物聯網先“聯網化”再智能化,模組率先受益

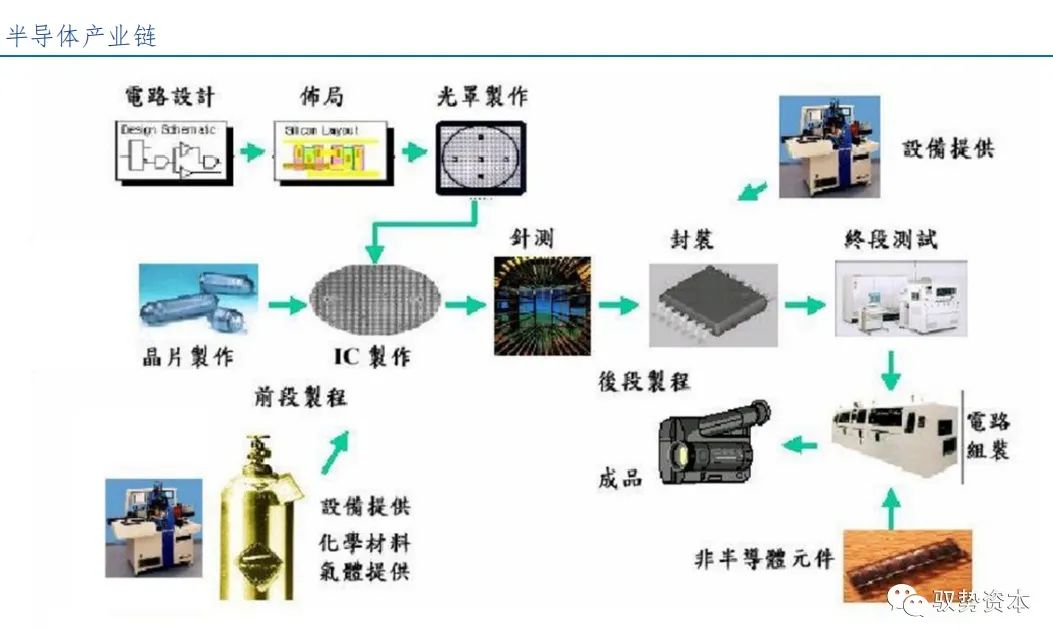

半導體的生產過程可分為晶圓制造工序(Wafer Fabrication)、封裝工序(Packaging)、測試工序(Test)等幾個步驟。其中晶圓制造工序為前道(Front End)工序,而封裝工序、測試工序為后道(Back End)工序。封裝是指將生產加工后的晶圓進行切割、焊線塑封,使電路與外部器件實現連接,并為半導體產品提供機械保護,使其免受物理、化學等環境因素損失的工藝。測試是指利用專業設備,對產品進行功能和性能測試,測試主要分為中測和終測兩種。

處于半導體產業鏈下游

半導體是電子終端產品的關鍵組成部分,產業鏈可分為設計、制造、封測三大環節。半導體設計人員根據需求完成電路設計和布線,晶圓廠在晶圓上完成這些電路的制造,刻好電路圖的晶圓再送到封測廠進行封裝和測試,檢測合格的產品便可應用于終端產品中。

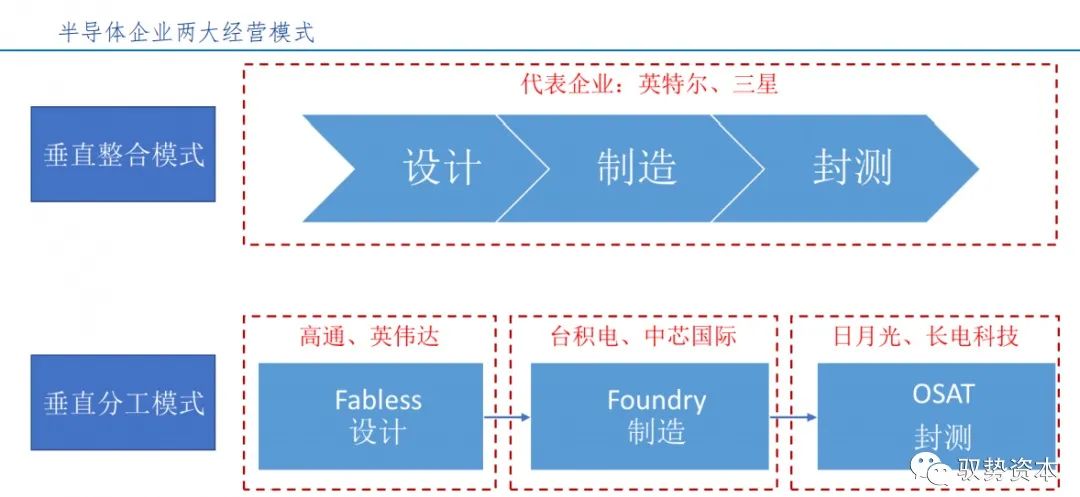

半導體企業的經營模式可分為垂直整合和垂直分工兩大類。采用垂直整合模式(Integrated Device Manufacturer,IDM)的企業可以獨立完成芯片設計、晶圓制造、封裝和測試等生產環節,代表企業包括英特爾、三星等。

垂直分工模式為Fabless設計+Foundry制造+OSAT封測。Fabless芯片設計公司采用無晶圓廠模式,只負責研發設計和銷售,將晶圓制造、封裝、測試外包出去,代表企業包括高通、英偉達等;Foundry晶圓代工廠僅負責晶圓制造,代表企業包括臺積電、中芯國際等;OSAT(Outsourced Semiconductor Assembly and Testing)為外包封測企業,僅負責封裝測試環節,代表企業包括日月光、安靠、長電科技等。

封測行業市場規模

根據Yole的數據,全球封測行業市場規模保持平穩增長,預計從2019年的680億美元增長到2025年的850億美元,年均復合增速約4%。根據中國半導體行業協會的數據,中國封測行業市場規模從2011年的976億元增長到了2019年的2350億元,年均復合增速約11.6%,顯著高于全球增速。

封測技術及發展方向

封測生產流程

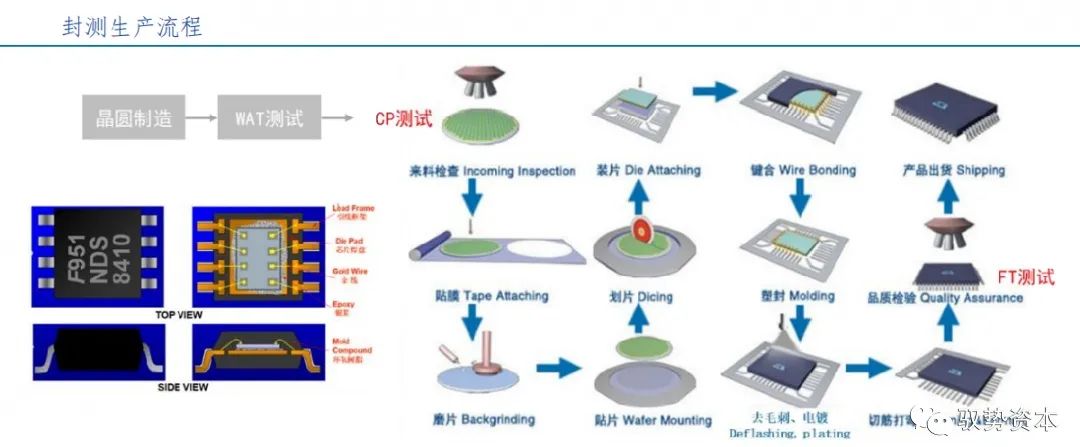

晶圓代工廠制造完成的晶圓在出廠前會經過一道電性測試,稱為晶圓可接受度測試(Wafer Acceptance Test,WAT),WAT測試通過的晶圓被送去封測廠。封測廠首先對晶圓進行中測(Chip Probe,CP)。由于工藝原因會引入各種制造缺陷,導致晶圓上的裸Die中會有一定量的殘次品,CP測試的目的就是在封裝前將這些殘次品找出來,縮減后續封測的成本。在完成晶圓制造后,通過探針與芯片上的焊盤接觸,進行芯片功能的測試,同時標記不合格芯片并在切割后進行篩選。

CP測試完成后進入封裝環節,封裝工藝流程一般可以分為兩個部分,用塑料封裝之前的工藝步驟稱為前段操作,在成型之后的工藝步驟稱為后段操作。基本工藝流程包括晶圓減薄、晶圓切割、芯片貼裝、固化、芯片互連、注塑成型、去飛邊毛刺、上焊錫、切筋成型、打碼等。因封裝技術不同,工藝流程會有所差異,且封裝過程中也會進行檢測。封裝完成后的產品還需要進行終測(Final Test,FT),通過FT測試的產品才能對外出貨。

半導體封裝類型

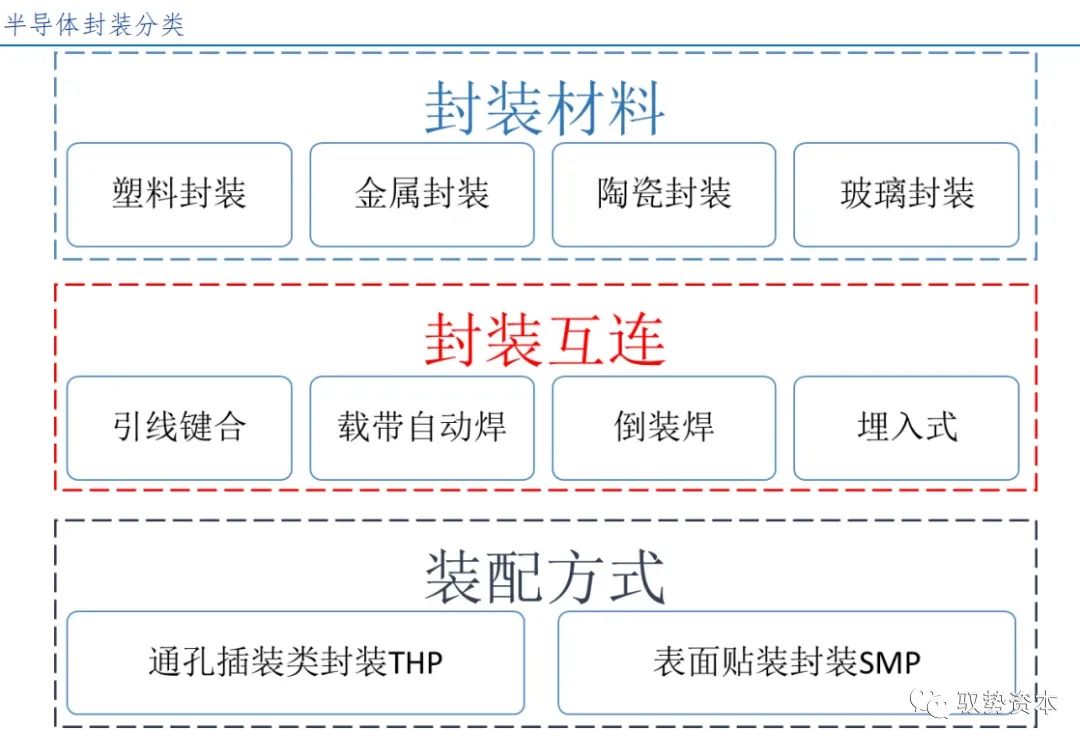

根據封裝材料的不同,半導體封裝可分為塑料封裝、金屬封裝、陶瓷封裝和玻璃封裝。塑料封裝是通過使用特制的模具,在一定的壓力和溫度條件下,用環氧樹脂等模塑料將鍵合后的半成品封裝保護起來,是目前使用最多的封裝形式。金屬封裝以金屬作為集成電路外殼,可在高溫、低溫、高濕、強沖擊等惡劣環境下使用,較多用于軍事和高可靠民用電子領域。

陶瓷封裝以陶瓷為外殼,多用于有高可靠性需求和有空封結構要求的產品,如聲表面波器件、帶空氣橋的GaAs器件、MEMS器件等。玻璃封裝以玻璃為外殼,廣泛用于二極管、存儲器、LED、MEMS傳感器、太陽能電池等產品。其中金屬封裝、陶瓷封裝和玻璃封裝屬于氣密性封裝,能夠防止水汽和其他污染物侵入,是高可靠性封裝;塑料封裝是非氣密性封裝。

根據封裝互連的不同,半導體封裝可分為引線鍵合(適用于引腳數3-257)、載帶自動焊(適用于引腳數12-600)、倒裝焊(適用于引腳數6-16000)和埋入式。引線鍵合是用金屬焊線連接芯片電極和基板或引線框架等。載帶自動焊是將芯片上的凸點與載帶上的焊點焊接在一起,再對焊接后的芯片進行密封保護的一種封裝技術。倒裝焊是在芯片的電極上預制凸點,再將凸點與基板或引線框架對應的電極區相連。埋入式是將芯片嵌入基板內層中。

根據與PCB連接方式的不同,半導體封裝可分為通孔插裝類封裝和表面貼裝封裝。通孔插裝器件是1958年集成電路發明時最早的封裝外形,其外形特點是具有直插式引腳,引腳插入PCB上的通孔后,使用波峰焊進行焊接,器件和焊接點分別位于PCB的兩面。表面貼裝器件是在通孔插裝封裝的基礎上,隨著集成電路高密度、小型化及薄型化的發展需要而發明出來的,一般具有“L”形引腳、“J”形引腳、焊球或焊盤(凸塊),器件貼裝在PCB表面的焊盤上,再使用回流焊進行高溫焊接,器件與焊接點位于PCB的同一面上。

目前,引線鍵合技術因成本相對低廉,仍是主流的封裝互聯技術,但它不適合對高密度、高頻有要求的產品。倒裝焊接技術適合對高密度、高頻及大電流有要求的產品,如電源管理、智能終端的處理器等。TAB封裝技術主要應用于大規模、多引線的集成電路的封裝。

先進封裝是后摩爾時代的必然選擇

封裝技術發展史

封裝技術的發展需要滿足電子產品小型化、輕量化、高性能等需求,因此,封裝技術過去和未來的發展趨勢均是高密度、高腳位、薄型化、小型化。

根據《中國半導體封裝業的發展》,半導體封裝技術的發展歷史可大致分為以下五個階段:

第一階段:20世紀70年代以前(通孔插裝時代),封裝技術是以DIP為代表的針腳插裝,特點是插孔安裝到PCB板上。這種技術密度、頻率難以提高,無法滿足高效自動化生產的要求。

第二階段:20世紀80年代以后(表面貼裝時代),用引線替代第一階段的針腳,并貼裝到PCB板上,以SOP和QFP為代表。這種技術封裝密度有所提高,體積有所減少。

第三階段:20世紀90年代以后(面積陣列封裝時代),該階段出現了BGA、CSP、WLP為代表的先進封裝技術,第二階段的引線被取消。這種技術在縮減體積的同時提高了系統性能。

第四階段:20世紀末以后,多芯片組件、三維封裝、系統級封裝開始出現。

第五階段:21世紀以來,主要是系統級單芯片封裝(SoC)、微機電機械系統封裝(MEMS)。

目前全球半導體封裝的主流正處在第三階段的成熟期和快速發展期,以CSP、BGA、WLP等主要封裝形式進入大規模生產時期,同時向第四、第五階段發展。從發展歷史可以看出,半導體封裝技術的發展趨勢可歸納為有線連接到無線連接,芯片級封裝到晶圓級封裝,二維封裝到三維封裝。

封裝技術封裝技術

根據技術先進性,封裝技術可分為傳統封裝技術和先進封裝技術兩大類。傳統封裝技術包括DIP、SOP、QFP、WB BGA等,先進封裝技術包括FC、WLP、FO、3D封裝、系統級封裝等。隨著晶圓代工制程不斷縮小,摩爾定律逼近極限,先進封裝是后摩爾時代的必然選擇。

(1)SIP/DIP

單列直插封裝(Single Inline Package,SIP)的引腳從封裝體的一個側面引出,排列成一條直線,SIP的引腳數量一般為2-23個。

雙列直插封裝(Dual Inline Package,DIP)的外形為長方形,在兩側有兩排平行的金屬引腳,稱為排針。DIP封裝的產品需要插入到具有DIP結構的芯片插座上,或者直接插在有相同焊孔數和幾何排列的電路板上再進行焊接。引腳數一般不超過100,適合中小規模集成電路封裝。

(2)SOP/QFP

小外形封裝(Small Out-Line Package,SOP)的引腳從封裝兩側引出,呈海鷗翼狀(L字形)。

方型扁平式封裝(Quad Flat Package,QFP)的管腳很細,引腳之間距離很小,可實現更多的I/O數,但仍受限于0.3mm的引腳間距極限。

(3)BGA

球柵陣列封裝(Ball Grid Array Package,BGA)用焊球代替周邊引線,成陣列分布于封裝基板的底部平面上,是在生產具有數百根引腳的集成電路時,針對封裝必須縮小的難題所衍生出的解決方案。

與上一代的QFP相比,BGA在減小體積和重量的情況下增加了I/O數量,但引腳的間距可以做得更大,成品率反而提高了;由于焊球間距明顯短于引線,BGA電性能更好;焊球的共面性也改善了散熱性。

根據芯片的位置不同可分為芯片表面向上和向下兩種;按焊球排列方式可為球柵陣列均勻分布、球柵陣列交錯分布、球柵陣列周邊分布等;按密封方式可分為模制密封和澆注密封等;按基板材料可分為塑料球柵陣列PBGA(Plastic Ball Grid Array)、陶瓷球柵陣列 CBGA(Ceramic Ball Grid Array)、載帶球陣列TBGA(Tape Ball Grid Array)等。

(4)FC

倒裝(Flip Chip,FC)技術由IBM在20世紀60年代研發出來,20世紀90年代后期形成規模化量產,主要應用于高端領域產品。隨著銅柱凸塊技術的出現,結合消費電子產品的快速發展和產品性能的需求,越來越多的產品轉向倒裝芯片封裝。

所謂“倒裝”是相對于傳統的金屬線鍵合連接方式(Wire Bonding,WB)而言的。傳統WB工藝,芯片通過金屬線鍵合與基板連接,電氣面朝上;倒裝芯片工藝是指在芯片的I/O焊盤上直接沉積,或通過RDL布線后沉積凸塊(Bump),然后將芯片翻轉,進行加熱,使熔融的焊料與基板或框架相結合,芯片電氣面朝下。與WB相比,FC封裝技術的I/O數多;互連長度縮短,電性能得到改善;散熱性好,芯片溫度更低;封裝尺寸與重量也有所減少。

倒裝芯片工藝流程中晶圓減薄、芯片倒裝和底部填充是關鍵工藝。在倒裝芯片的工藝中,晶圓來料上已經完成了凸塊的制作,因此晶圓正面并不平整。由于晶圓沒有凸塊的區域是空心結構,所以研磨過程中,晶圓會產生振動,容易造成晶圓龜裂甚至破片,尤其是超薄晶圓的研磨,目前一般采用底部填充工藝技術來解決該問題。

在芯片倒裝工藝中,需要采用高精度坐標對準技術將芯片上的凸塊焊接在高密度線路基板上,在此過程中,各方應力相互拉扯,基板容易產生翹曲現象,這會造成焊接出現偏移、冷焊、橋接短路等質量問題。底部填充是在芯片、凸塊及基板三種材料之間填充底部材料,以避免三種材料因膨脹系數不同而產生剪應力破壞,底部填充的關鍵因素是黏度、溫度、流動長度與時間。

凸塊工藝被稱為中道工序,是先進封裝的核心技術之一,通過高精密曝光、離子處理、電鍍等設備和材料,基于定制的光掩模,在晶圓上實現重布線,允許芯片有更高的端口密度,縮短了信號傳輸路徑,減少了信號延遲,具備了更優良的熱傳導性及可靠性。主流的凸塊工藝均采用晶圓級加工,即在整塊晶圓表面的所有芯片上加工制作凸塊,晶圓級凸塊工藝包括蒸發方式、印刷方式和電鍍方式三種,目前業界廣泛采用的是印刷方式和電鍍方式。晶圓代工廠在凸塊工藝方面具有一定優勢。

(5)WLP

晶圓級封裝(Wafer Level Packaging,WLP)直接在晶圓上進行大部分或全部的封裝測試程序,之后再進行切割制成單顆芯片。采用這種封裝技術,不需要引線框架、基板等介質,芯片的封裝尺寸減小,批量處理也使生產成本大幅下降。

WLP可分為扇入型晶圓級封裝(Fan-In WLP)和扇出型晶圓級封裝(Fan-Out WLP)兩大類。扇入型直接在晶圓上進行封裝,封裝完成后進行切割,布線均在芯片尺寸內完成,封裝大小和芯片尺寸相同;扇出型則基于晶圓重構技術,將切割后的各芯片重新布置到人工載板上,芯片間距離視需求而定,之后再進行晶圓級封裝,最后再切割,布線可在芯片內和芯片外,得到的封裝面積一般大于芯片面積,但可提供的I/O數量增加。

根據Yole的數據,全球晶圓級封裝2019年的市場規模為33億美元,預計2025年增加到55億美元,CAGR為8.9%。其中扇入型晶圓級封裝由2019年的20億美元增加到2025年的25億美元,CAGR為3.2%。2020年蘋果發布的iPhone12采用了扇入型晶圓級封裝,未來將會有更多的手機、平板、可穿戴設備采用此封裝形式。

(6)FO

扇出(Fan Out,FO)是相對扇入而言,“扇入”只能向內走線,而在扇出型封裝中,既可以向內走線,也可以向外走線,從而可以實現更多的I/O,以及更薄的封裝。目前量產最多的是晶圓級扇出型產品。

扇出型封裝工藝主要分為Chip first和Chip last兩大類,其中Chip first又分Die down和Die up兩種。

扇出型封裝生產工藝的關鍵步驟包括芯片放置、包封和布線。芯片放置對速度和精度的要求很高,放置速度直接決定生產效率,從而影響制造成本;放置精度也是決定后續布線精度的關鍵性因素。包封需要對包封材料進行填充和加熱,這一過程不僅可能導致已放置好的芯片發生移位,還有可能因包封材料與芯片的膨脹系數的不同而造成翹曲,這兩者都會影響后續的布線環節。布線成功率是決定最終封裝成品率的關鍵因素,另一方面,布線設備是整個生產設備中最昂貴的,對制造成本的影響很大。

根據封裝芯片數量,扇出型封裝分為晶圓級扇出型(Fan-out Wafer Level Packaging,FOWLP)和板級扇出型技術(Fan-out Panel Level Packaging,FOPLP),FOWLP對單個芯片進行封裝,FOPLP對多個芯片進行封裝。雖然FOPLP的增速更快,FOWLP在未來幾年仍占主導。根據Yole的數據,2019-2025年FOPLP的CAGR達57%,FOWLP的CAGR為14%,但FOWLP在2025年的占比仍會在2/3以上。eWLB(Embedded Wafer Level Ball Grid Array)是目前量產規模最大的晶圓級扇出型封裝。

根據密度的高低,Yole將扇出型封裝分為UHD扇出(Ultra High Density)、HD扇出(High Density)和核心扇出三大類。UHD扇出的需求將隨著新的HPC產品的出現而增加,預計2019-2025年的CAGR最高,為20.2%,到2025年市場規模達15.32億美元,占扇出型一半的市場;HD扇出的CAGR為15.8%,到2025年達12.91億美元;核心扇出增長緩慢,CAGR僅1%。

(7)3D/2.5D封裝

3D封裝又稱為疊層芯片封裝技術,是指在不改變封裝體尺寸的前提下,在同一個封裝體內于垂直方向疊放兩個以上芯片的封裝技術,它起源于快閃存儲器(NOR/NAND)及SDRAM的疊層封裝,可以實現不同類型芯片的異質集成,目前在存儲芯片上已有較多應用。

3D封裝可采用凸塊或硅通孔技術(Through Silicon Via,TSV),TSV是利用垂直硅通孔完成芯片間互連的方法,由于連接距離更短、強度更高,能實現更小更薄而性能更好、密度更高、尺寸和重量明顯減小的封裝,而且還能用于異種芯片之間的互連。

2.5D封裝是在基板和芯片之間放一個硅中間層,這個中間層通過TSV連接上下部分。

(8)SiP

系統級封裝(System in Packag,SiP)是將多種功能芯片,包括處理器、存儲器、FPGA等功能芯片集成在一個封裝內,從而實現一個基本完整的功能。與系統級芯片(System on Chip,SoC)相對應,不同的是系統級封裝是采用不同芯片進行并排或疊加的封裝方式,而SoC則是高度集成的芯片產品。SiP解決方案需要多種封裝技術,如引線鍵合、倒裝芯片、芯片堆疊、晶圓級封裝等,是超越摩爾定律的重要實現路徑。

根據Yole的數據,2019年全球SiP封裝的市場規模為134億美元,預計2025年增加到188億美元,CAGR為6%。

從應用領域來看,移動設備和消費電子是最大市場,2019-2025年的CAGR為5%;通訊/基礎設施和汽車電子緊隨其后,兩者的CAGR均為11%,高于整體增速。

從使用的封裝技術來看,FC/WB SiP占比超過90%,2019年市場規模為122億美元,預計到2025年將達到171億美元,2019年至2025年的復合年增長率為6%。FO SiP仍受限于成本效益比,參與者需要掌握FO技術,所以從2017年開始,臺積電便是最主要的參與者,2019年市占率超過90%。

先進封裝市場規模

摩爾定律的放緩、異質集成和各種大趨勢(包括5G、AI、HPC、物聯網等)推動著先進封裝市場強勢發展。根據Yole的數據,2019年全球先進封裝市場規模約290億美元,預計2025年增長到420億美元,年均復合增速約6.6%,高于整體封裝市場4%的增速和傳統封裝市場1.9%的增速。

從下游應用市場來看,移動設備和消費電子對集成度要求高,是先進封裝最大的細分市場,2019年占比達85%,2019-2025的CAGR為5.5%,略低于整體增速,2025年將占先進封裝市場的80%。電信和基礎設施是先進封裝市場中增長最快的細分市場,CAGR約為13%,市場份額將從2019年的10%增至2025年的14%。汽車與運輸細分市場在2019年至2025年期間將以10.6%的CAGR增長,到2025年達到約19億美元,但其在先進封裝市場中所占的份額仍將持平,約4%。

從技術分類來看,3D堆疊封裝、嵌入式芯片封裝、扇出型封裝在2019年到2025年的增速更高,CAGR分別為21%、18%、16%。扇出型技術進入移動設備、網絡和汽車領域;3D堆疊技術進入AI/ML、HPC、數據中心、CIS、MEMS/傳感器領域;嵌入式芯片封裝進入移動設備、汽車和基站領域。

從先進封裝收入構成來看,倒裝技術占比遙遙領先,2018年占比81%。

從晶圓數來看,2019年約2900萬片晶圓采用先進封裝,到2025年增長為4300萬片,年均復合增速為7%。其中倒裝技術占比最高,3D封裝增速最快。

封測領域競爭格局

原來封測領域的廠商主要有兩類,一類是IDM公司的封測部門,主要完成本公司半導體產品的封測環節,屬于對內業務;第二類是外包封測廠商OSAT,其作為獨立封測公司承接半導體設計公司產品的封測環節。

隨著摩爾定律極限接近,基于硅平臺的先進封裝技術不斷發展,晶圓代工廠利用其在硅平臺的積累正在進入封測領域,尤其是先進封裝。

我們的重點是關注OSAT公司和晶圓代工廠在封測領域的競爭情況。

前十大OSAT企業

1968年,美國公司安靠的成立標志著封裝測試業從IDM模式中獨立出來,直到2002年安靠一直是全球封測龍頭。1987年臺積電成立,成為全球第一家專業晶圓代工企業,并且長期占據全球晶圓代工50%以上的市場份額。臺積電的成功也帶動了本地封測需求,臺灣成為全球封測重地,日月光在2003年取代安靠成為全球封測龍頭。至今全球前十大OSAT企業中有6家來自臺灣。

封測是我國半導體產業鏈中國產化水平較高的環節,全球前十大外包封測廠中,我國占了三席,分別是第三的長電科技、第六的通富微電和第七的天水華天。

晶圓廠入局

臺積電領先地位凸顯

臺積電于2008年底成立集成互連與封裝技術整合部門,經過超十年的構建,目前已經完成晶圓級系統整合(WLSI)技術平臺,該平臺利用臺積電公司工藝制程與產能的核心競爭力,建立支援異質系統整合與封裝能力,以滿足特定客戶在芯片性能、功耗、輪廓、周期時間及成本的需求。至今,在先進封裝領域,臺積電的領先地位已經尤其突顯。從2019年封裝收入排名來看,臺積電在OSAT中排名第4,約30億美元,約占臺積電收入的8.4%。從技術來看,臺積電重心在發展扇出型封裝InFO(Integrated Fan Out,整合扇出型封裝)、2.5D封裝CoWoS(Chip-on-Wafer-on-Substrate,基板上晶圓上芯片封裝)和3D封裝SoIC(System-on-Integrated-Chips,集成芯片系統)。

CoWoS于2011年推出,2013年在賽靈思28nm的FPGA上量產,之后隨著AI的發展被大量采用,包括英偉達的GP 100、谷歌的TPU 2.0等;InFO于2014年投入研發,2016年臺積電利用該技術獲得了蘋果 APU(A10)訂單,InFO成為臺積電獨占蘋果A系列處理器訂單的關鍵;SoIC還處于研發中,預計2021年量產。

中芯國際攜手封測廠入局

2014年中芯國際與長電科技合資成立中芯長電,由中芯國際控股。中芯長電是全球首家采用集成電路前段芯片制造體系和標準,采用獨立專業代工模式服務全球客戶的中段硅片制造企業。以先進的凸塊和再布線加工起步,中芯長電致力于提供中段硅片制造和測試服務,并進一步發展先進的三維系統集成芯片業務。

目前中芯長電位于江陰的基地提供12英寸中段硅片加工,專注于12英寸凸塊和先進硅片級封裝;上海基地提供8英寸中段凸塊和硅片級封裝。另外在江陰以及上海兩地均擁有測試廠,能夠提供測試程序開發、探針卡制作、晶圓測試、失效分析以及失效測試服務。

中芯國際來自先進封裝(凸塊加工及測試業務)的收入占比逐年提升,但2019年也僅實現收入4.76億元,占總營收的比例為2.2%。

2020年12月15日中芯國際聘任蔣尚義博士為公司董事會副董事長、第二類執行董事及戰略委員會成員。蔣尚義博士曾在臺積電掌舵研發,并帶領完成臺積電先進封裝技術的開發。加入中芯國際后,蔣尚義博士公開表示中芯國際將同時發展先進工藝和先進封裝。隨著蔣尚義博士的加入,中芯國際在先進封裝方面的進展值得期待。

封測廠商經營情況

封測廠商通過外延增強競爭力

封測廠商的發展歷史是圍繞著并購展開的,其中日月光和中國三巨頭尤其明顯。

日月光1984年成立,1989年上市時便已全球排名第二,之后十年完成了三次重要并購,于2003年成功超過安靠成為全球第一大封測廠商。之后公司仍然沒有停止并購步伐,至今仍然保持著全球第一的位置。2018年日月光更與排名第四的矽品以股份轉換方式設立日月光投控,日月光投控的規模約為第二名安靠的兩倍,封測領域龍頭地位進一步鞏固。

中國三大封測廠商長電科技、通富微電、華天科技均在2015年前后通過收購海外封測廠而躋身全球前列。其中長電科技以當時全球第六的地位收購新加坡全球第四的星科金朋,成為全球第三大封測廠商。

國內四大封測廠商經營數據

在國內四大封測廠商中,長電科技的體量遠遠領先,通富微電、華天科技體量接近,晶方科技聚焦傳感器市場體量較小。從研發投入來看,晶方科技所有收入均來自于先進封裝,所以研發投入率高達22%,遠遠超過其他三家;通富微電聚焦在處理器、存儲等高端封裝市場,研發投入率也明顯高于長電科技和華天科技。從人均創收角度,長電科技最高,通富微電、晶方科技接近,華天科技較低。

從毛利率和凈利率來看,晶方科技由于專注于傳感器領域的晶圓級芯片尺寸封裝,毛利率和凈利率均遠遠高于其他封測廠商,但隨著2014年收購的資產進入折舊而收入并未跟上,其毛利率和凈利率均在2015年明顯下降。

長電科技、通富微電、華天科技在2016年將收購的企業并表后,由于處于整合階段,整體毛利率、凈利率均出現下滑,其中長電科技尤其明顯,毛利率最低,僅11%左右,并且多次出現虧損。

從2019年開始,國內四大封測廠商均迎來了業績改善。晶方科技在2019年因CIS缺貨漲價表現最好,毛利率和凈利率從2019Q2開始同比改善。2019Q4四大封測廠毛利率均同比提高,2020年四大封測廠商業績繼續改善,毛利率、凈利率均同比提高。

從收益質量來看,2020年前三季度長電科技、華天科技、晶方科技超過80%的凈利潤來自于經常性收益,其中長電科技扣非后凈利潤實現扭虧為盈;通富微電約42%的凈利潤來自非經常性損益,其中主要是政府補助。四家封測廠商的經營性現金流情況均很好,2020年前三季度的凈利潤現金含量均在100%以上。

從客戶集中度來看,長電科技、華天科技客戶相對分散,2019年前五大客戶收入占比分別為33%、17%;通富微電、晶方科技客戶相對集中,2019年前五大客戶收入占比分別為67%、80%。通富微電由于收購AMD的封測廠,AMD成為其第一大客戶,2019年貢獻49%的收入。晶方科技由于集中于傳感器領域,客戶也相對集中。

長電科技、通富微電、華天科技均曾大額收購海外封測廠,從而形成了較高的商譽。截止2019年12月31日,商譽分別為22.14億元、10.99億元、8.11億元,占全年收入的比例分別為9%、13%、10%。長電科技的商譽來自收購星科金朋100%的股權;通富微電商譽來自收購通富超威蘇州和通富超威檳城85%的股權;華天科技商譽來自多個收購,其中最主要的是Unisem(友尼森)和宇芯成都,分別為3.67億元和4.26億元。

國內四大封測廠定增擴產,長期受益本地需求增加

在產能供不應求的情況下,國內四大封測廠商均于近期發布定增擴產計劃,其中通富微電、晶方科技分別于2020年2月和3月首次公告定增預案,已于2020年11月和2021年1月發行股份完畢;長電科技于2020年8月公告定增預案,2020年12月已拿到證監會批復文件;華天科技于2021年1月公告預案。

從四大封測廠的投資項目來看,系統級封裝、多芯片封裝、晶圓級封裝是主要方向。半導體產業鏈相關公司積極參與封測廠商定增,通富微電發行對象中包括卓勝微、華峰測控、芯海科技、韋爾股權等上下游公司,晶方科技發行對象中包括韋爾股權。

從長期來看,國內半導體產業正處于快速發展期,芯片設計公司和晶圓代工廠的增加將帶動本地封測需求。

根據億歐的數據,我國芯片設計公司數量2016年激增626家,達到1362家,增加85%,到2019年增加到1780家。

根據IC Insight統計數據,2018年中國晶圓產能243萬片/月(等效于8寸晶圓),中國大陸晶圓產能占全球晶圓產能12.5%。根據IC Insight對未來產能擴張預測,隨著半導體制造硅晶圓產能持續向中國轉移,2022年中國大陸晶圓廠產能將達410萬片/月,占全球產能17.15%。2018-2022年中國硅晶圓產能的年均復合增長率達14%,遠高于全球產能年均復合增長率5.3%。

半導體

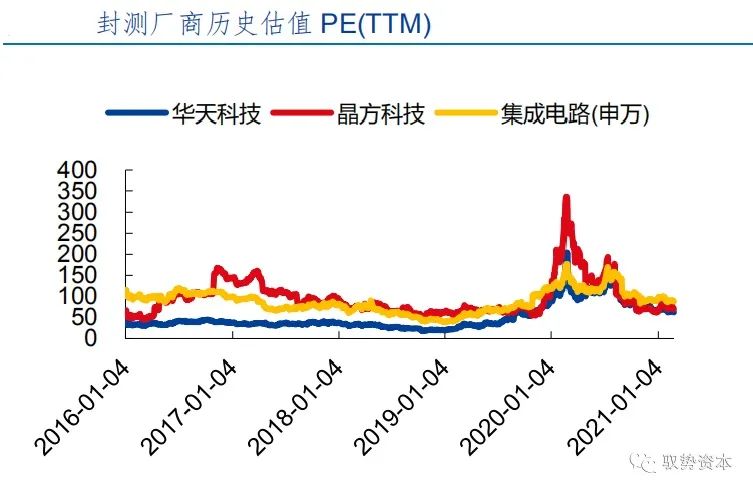

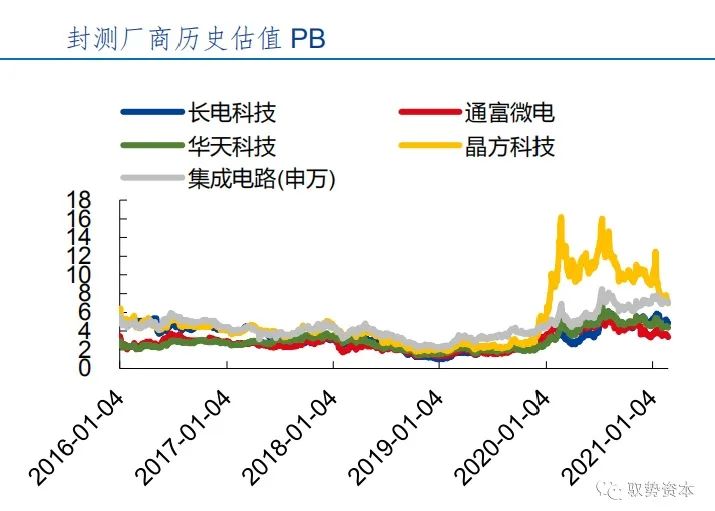

2016-2019年是長電科技并購整合的階段,業績波動較大,2016、2018年全年出現虧損,因此PE相對估值波動也很大,不具有參考性;通富微電也在2019年上半年因中美關系緊張出現虧損,PE相對估值不具參考性。對應PE相對估值,我們主要考察華天科技和晶方科技,從2016年以來,晶方科技因為主要從事先進封裝業務,市場長期給予估值溢價,PE大部分時間高于華天科技。截止2021年2月26日,長電科技、華天科技、晶方科技的PE(TTM)估值接近,且均低于集成電路指數;通富微電的PE(TTM)較高,主要是市場看好公司在處理器和存儲封測的布局。

封測行業屬于重資產行業,PB值具有一定的參考意義。截止2021年2月26日,四家封測企業的PB估值均高于2016年以來的中值和均值,考慮到封測企業從2019年底開始盈利能力改善,資產收益率提高,我們認為PB估值處于相對高位具有合理性。集成電路指數中含有大量輕資產的芯片設計公司,PB值與封測企業不具有可比性。

行業整體而言,我們認為半導體行業目前仍處于上行周期,封測產能供不應求,先進封裝更是后摩爾時代的必然選擇,成為各大廠商發力點,除了原有的IDM封測部、OSAT外包封測企業外,以臺積電為代表的晶圓代工廠成為最大攪局者。

從我國而言,封測環節是半導體產業鏈中實力最強的部分,具備國際競爭力。在行業景氣度上行和加大內部整合的情況下,我國四大封測企業均在2019年下半年迎來了業績拐點。從長期來看,國內半導體產業正處于快速發展期,芯片設計公司和晶圓代工廠的增加將帶動本地封測需求,在產能吃緊的情況下,國內四大封測廠商均于近期發布了定增擴產計劃,規模有望進一步擴大。

審核編輯 :李倩

-

封裝技術

+關注

關注

12文章

550瀏覽量

68008 -

chiplet

+關注

關注

6文章

434瀏覽量

12609

原文標題:Chiplet開啟了IP新型復用模式

文章出處:【微信號:AIOT大數據,微信公眾號:AIOT大數據】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

怎么才能開啟ADS1115的快速模式?

解鎖Chiplet潛力:封裝技術是關鍵

Chiplet技術革命:解鎖半導體行業的未來之門

請問DAC38J82如何開啟NRZ輸出模式?

2035年Chiplet市場規模將超4110億美元

IMEC組建汽車Chiplet聯盟

Primemas選擇Achronix eFPGA技術用于Chiplet平臺

創新型Chiplet異構集成模式,為不同場景提供低成本、高靈活解決方案

如何使用AT固件開啟ESP32 Ethernet DHCP Server模式?

Chiplet是否也走上了集成競賽的道路?

什么是Chiplet技術?

Chiplet技術對英特爾和臺積電有哪些影響呢?

Chiplet開啟了IP新型復用模式

Chiplet開啟了IP新型復用模式

評論