目錄預(yù)覽

1.問題原因

2.RAMECC 控制單元

3.RAMECC 寄存器地址

4.RAMECC 寄存器

5.解決問題

1.問題原因

某客戶測試 STM32H753xi 板子上的 ECC 功能,用于監(jiān)控 AXI-SRAM 區(qū)域,但不是很明白 RAMECC FAR 寄存器在 RM0433 中的描述, “Bits 31:0 FADD[31:0]: ECC error failing address”。

比如在 AXI-SRAM 中,如果客戶示例顯示的是 FAR = 0x2004,但是這個(gè)地址值 0x2004 并不在 AXI-SRAM 范圍之內(nèi),客戶該如何理解 FAR 寄存器?希望能夠有詳盡的描述,這個(gè) FAR 寄存器的偏移地址是 Word 地址還是 Byte 地址或其他?我們先來看看相關(guān)參考手冊中關(guān)于 RAMECC 的介紹去尋找答案。

2.RAMECC 控制單元

RAM ECC 控制單元的數(shù)量取決于不同的 STM32H7 系列。比如,對(duì)于STM32H74x/5x 和 STM32H72x/3x 它們的每一個(gè)域都有一個(gè) RAMECC 的控制器單元,為了描述簡單,表述如下:

Domain 1 (D1) RAMECC unit = RAMECC1Domain 2 (D2) RAMECC unit = RAMECC2Domain 3 (D3) RAMECC unit = RAMECC3

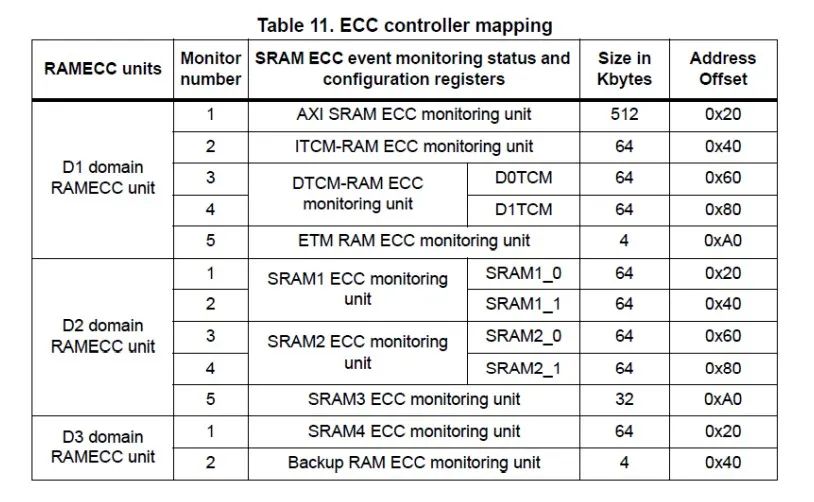

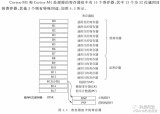

詳細(xì)的說明請參考 RM0433 參考手冊 rev7 中的截圖:

3.RAMECC 寄存器地址

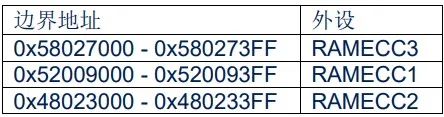

對(duì)于上圖 Table 11 的 RAMECC 控制單元的地址總結(jié)成如下表格,具體的參考RM0433 的第二章節(jié) Memory and bus architecture 中的 table 8.

4.RAMECC 寄存器

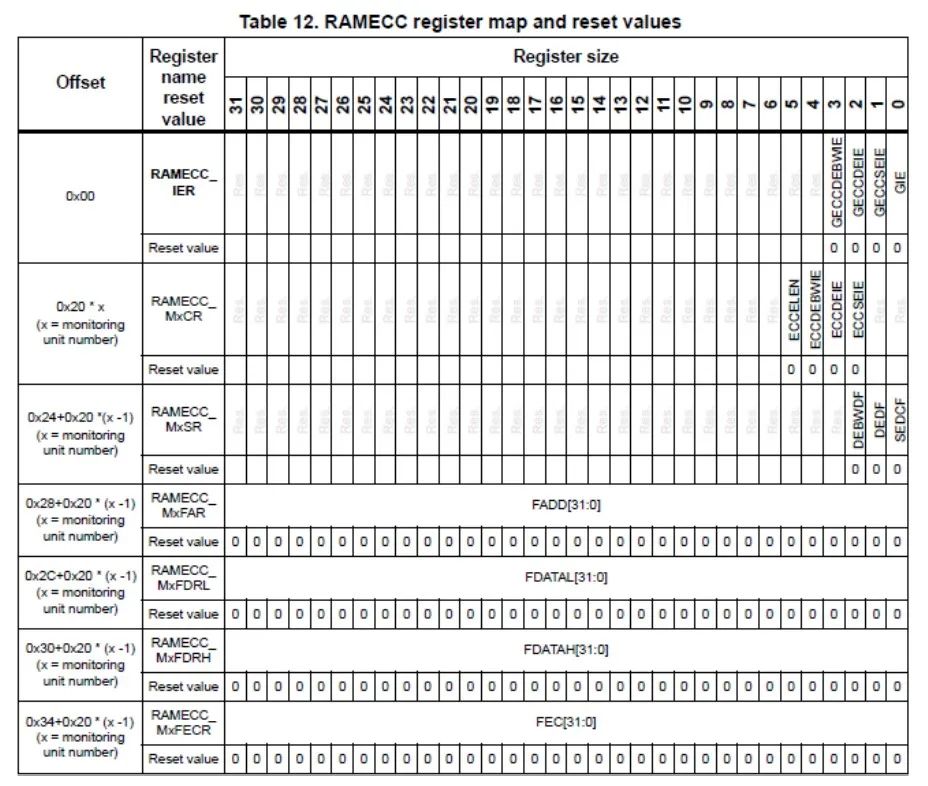

每一個(gè) RAMECC 控制單元(RAMECC1、RAMECC2、RAMECC3)的監(jiān)控單元Monitor number 均分別含有如下的一套寄存器組(其中 RAMECC_IER 為共同擁有)。

接下來我們以 RAMECC1 為例進(jìn)行分析,其邊界地址為:0x52009000 -0x520093FF,那么對(duì)于該 RAMECC1 控制單元中的寄存器組,對(duì)于每一個(gè)寄存器:

以 RAMECC1 的起始地址 0x52009000 為基準(zhǔn):RAMECC_IER:中斷使能,偏移地址 0x00,該寄存器地址即為:0x52009000。

RAMECC_MxCR:配置寄存器,偏移地址 0x20 *x,x 為 ECC 監(jiān)控單元號(hào),該寄存器地址的表達(dá)式為:0x52009000 + 0x20 * x ,x 取值范圍= [1..5](見上面表格 Table 11 ECC controller mapping),所以:

Monitor 1 - AXI SRAM ECC 監(jiān)控單元,該寄存器地址即為 0x52009020,監(jiān)控大小為整個(gè) AXI SRAM 的 512KB 字節(jié)(0x24000000 -0x2407FFFF)。

Monitor 2 - ITCM-RAM ECC 監(jiān)控單元,該寄存器地址0x52009040, 監(jiān)控大小為整個(gè)ITCM RAM的64KB字節(jié)(0x00000000 -0x0000FFFF)。

Monitor 3、Monitor 4、Monitor 5 中該 RAMECC_MxCR 寄存器的地址,以此類推。

RAMECC_MxSR -- 狀態(tài)寄存器,偏移地址: 0x24 + 0x20 * (x - 1),x 為 ECC monitor number 號(hào)碼(見上面表格 Table 11 ECC controller mapping)。那么該寄存的地址為:0x52009000 + 0x24 + 0x20 * (x-1) ,x 取值范圍 = [1..5]:

Monitor 1:0x52009024

Monitor 2:0x52009044

Monitor 3 : 0x52009064

Monitor 4 : 0x52009084

Monitor 5 : 0x520090a4

RAMECC_MxFAR --失敗地址寄存器,表達(dá)式:0x52009000 + 0x28 + 0x20 * (x-1) , x取值 = [1..5]:

Monitor 1:0x52009028

Monitor 2:0x52009048

Monitor 3:0x52009068

Monitor 4:0x52009088

Monitor 5:0x520090a8

RAMECC_MxFDRL -- 失敗數(shù)據(jù)低位,表達(dá)式 0x52009000 + 0x2c + 0x20 * (x-1) ,x 取值= [1..5]

Monitor 1:0x5200902c

Monitor 2:0x5200904c

Monitor 3:0x5200906c

Monitor 4:0x5200908c

Monitor 5:0x520090ac

RAMECC_MxFDRH -- 失敗數(shù)據(jù)高位,表達(dá)式 0x52009000 + 0x30 + 0x20 * (x-1),x 取值= [1..5]

Monitor 1:0x52009030

Monitor 2:0x52009050

Monitor 3:0x52009070

Monitor 4:0x52009090

Monitor 5:0x520090b0

RAMECC_MxFECR --失敗 ECC 錯(cuò)誤代碼,表達(dá)式 0x52009000 + 0x34 + 0x20 * (x1) ,x 取值 = [1..5]

Monitor 1:0x52009034

Monitor 2:0x52009054

Monitor 3:0x52009074

Monitor 4:0x52009094

Monitor 5:0x520090b4

5.解決問題

通過查詢資料與試驗(yàn),F(xiàn)ADD[31:0]中表述的地址是 word 而不是 bit。為了計(jì)算真實(shí)的地址,客戶需要用如下公式計(jì)算:真實(shí)地址= 所處內(nèi)存的首地址 + FADD x 字節(jié)數(shù)。

現(xiàn)在舉個(gè)例子,如上述提到的 FADD= 0x2004 :

- 對(duì)于 64-bit word 的內(nèi)存 :如 AXI RAM : 0x2400 0000 + 0x2004 * 8 = 0x2401 0020;

- 對(duì)于 32-bit word 的內(nèi)存 :如 SRAM1 : 0x3000 0000 + 0x2004 * 4=0x3000 8010 ;

END

-

單片機(jī)

+關(guān)注

關(guān)注

6040文章

44604瀏覽量

637058 -

STM32

+關(guān)注

關(guān)注

2270文章

10918瀏覽量

356830

原文標(biāo)題:工程師筆記|如何理解 RAMECC FAR 寄存器的值

文章出處:【微信號(hào):STM32_STM8_MCU,微信公眾號(hào):STM32單片機(jī)】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評(píng)論請先 登錄

相關(guān)推薦

Modbus協(xié)議的讀取保持寄存器值

硬件工程師VS軟件工程師|硬件工程師看到這都淚目了!#硬件設(shè)計(jì) #硬件工程師 #電子工程師 #軟件工程師

FPGA算法工程師、邏輯工程師、原型驗(yàn)證工程師有什么區(qū)別?

ARM處理器的寄存器組織及功能

數(shù)字寄存器的原理和使用

寄存器是什么意思?寄存器是如何構(gòu)成的?

寄存器尋址和直接尋址的區(qū)別

寄存器尋址的實(shí)現(xiàn)方式

寄存器分為基本寄存器和什么兩種

干貨滿滿:ARM的內(nèi)核寄存器講解

工程師筆記|如何理解 RAMECC FAR 寄存器的值

工程師筆記|如何理解 RAMECC FAR 寄存器的值

評(píng)論