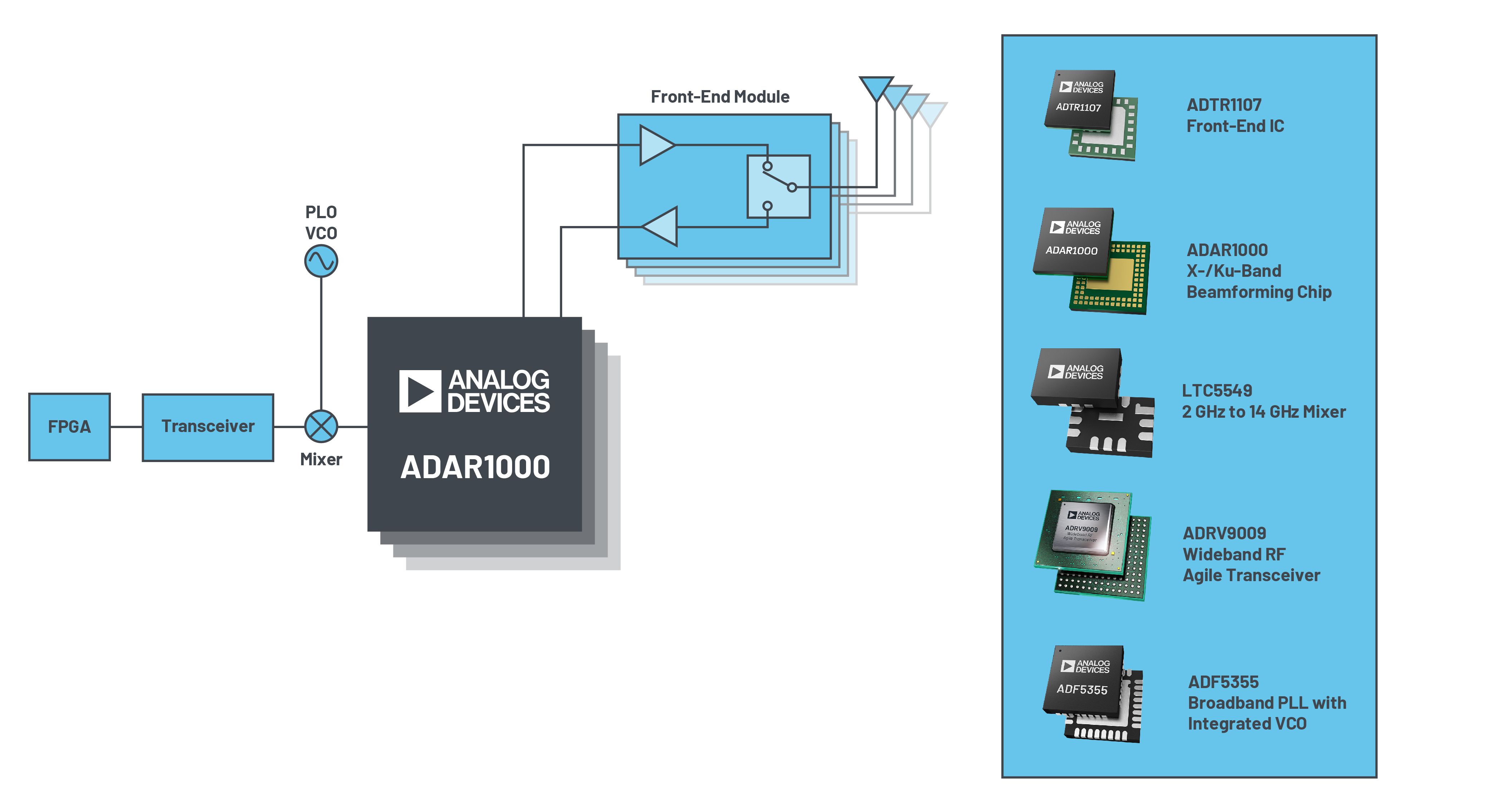

半導體技術的進步使相控陣天線在整個行業中的普及成為可能。這種從機械轉向天線到有源電子掃描天線(AESA)的轉變始于多年前的軍事應用,但最近在衛星通信移動和5G通信方面迅速發展。薄型AESA具有快速轉向能力、產生多種輻射圖的能力和更高的可靠性等優點;然而,這些天線在廣泛使用之前需要IC技術的重大進步。平面相控陣要求設備具有高集成度、低功耗和高效率,以便用戶可以將這些組件安裝在天線陣列后面,同時將產生的熱量保持在可接受的水平。本文將簡要介紹相控陣芯片組的進步如何使平面相控陣天線成為可能,然后舉例說明。

介紹

在過去的幾年中,拋物面碟形天線已被廣泛用于發送和接收方向性很重要的信號。其中許多系統運行良好,經過多年的優化,成本相對較低。這些機械轉向碟形天線確實有一些缺點。它們物理尺寸大,轉向速度慢,長期可靠性較差,并且它們僅提供一種所需的輻射圖或數據流。

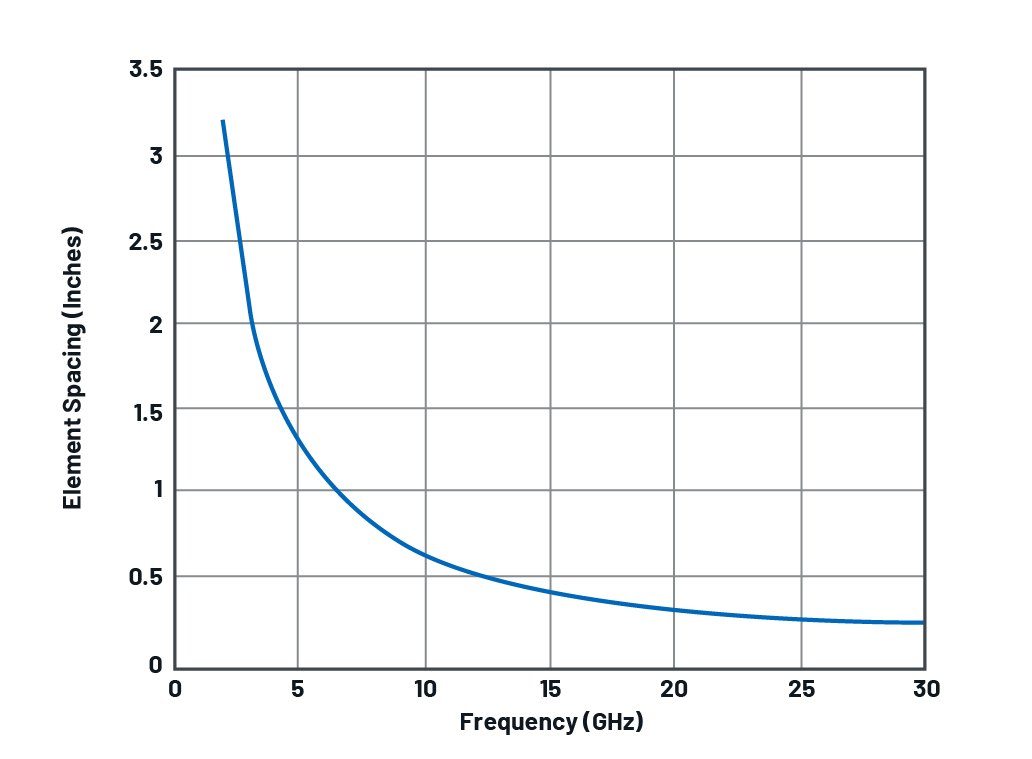

相控陣天線采用電控,具有許多優點,例如外形更小、體積更小、長期可靠性更高、轉向速度更快和多波束。相控陣天線設計的一個關鍵方面是天線元件的間距。大多數陣列所需的大約半波長元件間距在更高頻率下創造了特別具有挑戰性的設計。這推動了更高頻率的IC越來越集成,封裝解決方案變得更加先進。

人們對將相控陣天線技術用于各種應用有著濃厚的興趣。然而,工程師一直受到可用IC的限制,無法使其可行。由于IC芯片組的最新發展,情況已不再如此。半導體技術正朝著先進的硅IC發展,我們可以將數字控制、存儲器和RF晶體管組合到同一個IC上。此外,氮化鎵(GaN)顯著提高了功率放大器的功率密度,從而提供了更小的尺寸。

相控陣技術

業界正在大力推動低調陣列,這些陣列消耗的體積和重量更少。傳統的木板架構基本上使用小型PCB木板,其上的電子設備垂直饋入天線PCB的背面。在過去的20年中,這種方法得到了改進,以不斷減小木板的尺寸,從而減少天線的深度。下一代設計從這種木板架構轉向平板方法。平板設計顯著減小了天線的深度,使其更容易安裝到便攜式或機載應用中。要實現更小的尺寸,需要在每個IC中集成足夠的尺寸,以將它們安裝在天線的背面。

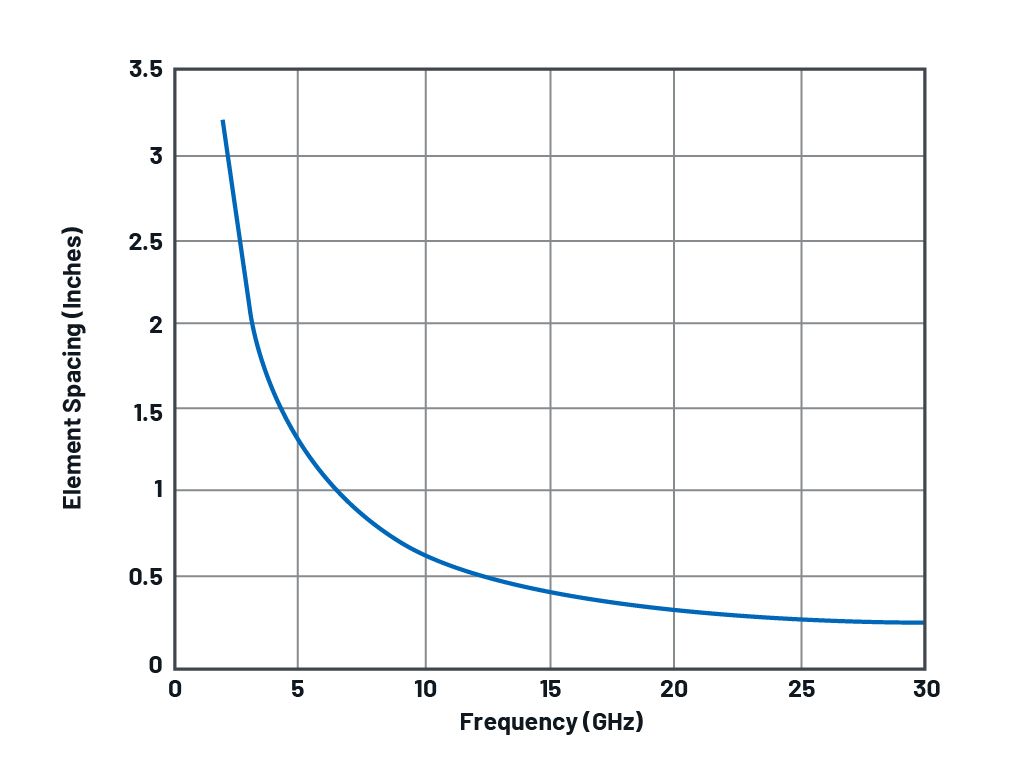

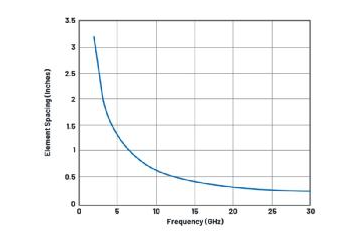

在平面陣列設計中,天線背面的IC可用空間受到天線元件間距的限制。例如,在高達 60° 掃描角度下,防止光柵瓣的最大天線元件間距為 0.54 λ。圖1顯示了最大元件間距(以英寸為單位)與頻率的關系。隨著頻率的提高,元件之間的間距變得非常小,天線后面的組件幾乎沒有空間。

圖1.天線元件間距可防止光柵波瓣在 60° 離軸時出現。

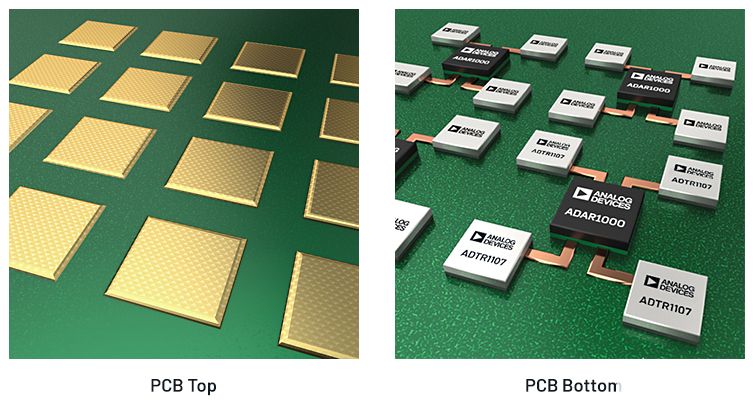

在圖2中,左圖顯示了PCB頂部的金色貼片天線元件,右圖顯示了PCB底部天線的模擬前端。在這些設計中,附加層上的變頻級和配電網絡也很典型。很容易看出,集成度更高的IC顯著減少了以所需間距布置天線設計的挑戰。隨著天線變得越來越小,更多的電子設備封裝在更小的尺寸中,它需要新的半導體和封裝技術來幫助使解決方案可行。

圖2.顯示 PCB 頂部的天線補丁以及天線 PCB 背面的 IC 的平板陣列。

半導體技術與封裝

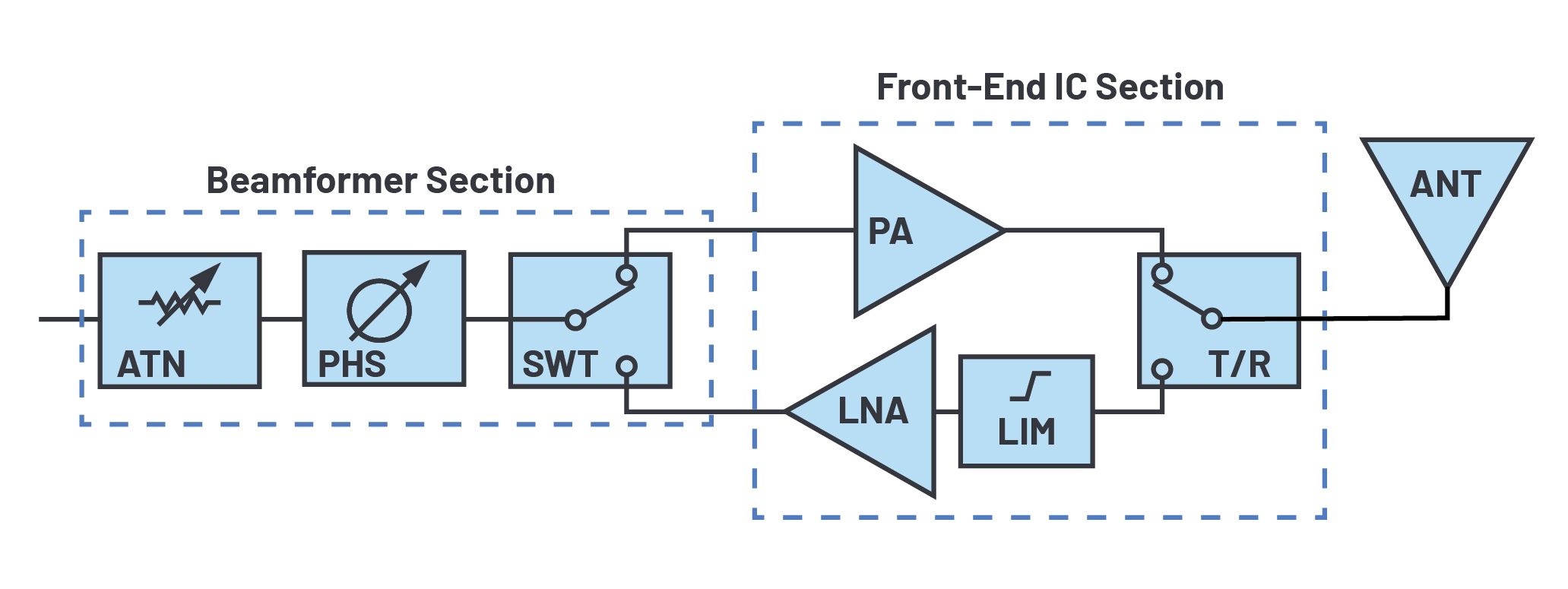

用作相控陣天線構建模塊的微波和毫米波(mmW)IC元件如圖3所示。在波束成形部分,衰減器調整每個天線元件的功率電平,從而減少天線方向圖的旁瓣。移相器調整每個天線元件的相位以控制天線主波束,并使用開關在發射器和接收器路徑之間切換。在前端IC部分,功率放大器用于發射信號,低噪聲放大器用于接收信號,最后,另一個開關用于在發射器和接收器之間切換。在過去的實現中,這些IC中的每一個都作為單獨的封裝器件提供。更先進的解決方案可以采用集成的單片單通道砷化鎵(GaAs)IC來實現此功能。未顯示,但在波束成型器之前的大多數陣列中都包含無源RF合路器網絡,接收器/激勵器和信號處理器。

圖3.相控陣天線的典型射頻前端。

最近相控陣天線技術的普及得益于半導體技術的進步。SiGe BiCMOS、絕緣體上硅(SOI)和體CMOS中的高級節點結合了數字和RF電路。這些IC可以執行陣列中的數字任務,以及控制RF信號路徑,以實現所需的相位和幅度調整。如今,可以實現多通道波束成形IC,在4通道配置中執行增益和相位調整,以及針對mmW設計的多達32個通道。在一些低功耗示例中,硅基IC可以作為上述所有功能的單片解決方案。在高功率應用中,基于氮化鎵的功率放大器顯著提高了相控陣天線單元的功率密度。這些放大器傳統上使用基于行波管(TWT)的技術或相對低功耗的基于GaAs的IC。

在機載應用中,我們看到平板架構的趨勢是具有GaN技術的功率附加效率(PAE)優勢。氮化鎵還使大型地面雷達從由TWT驅動的碟形天線轉變為由固態氮化鎵IC驅動的基于相控陣的天線技術。我們現在能夠擁有單片GaN IC,能夠以超過50%的PAE提供超過100 W的功率。將這種效率水平與雷達應用的低占空比相結合,可以實現表面貼裝解決方案,我們可以散發通過封裝底座產生的熱量。這些表面貼裝PA大大降低了天線陣列的尺寸、重量和成本。除了GaN的純功率能力之外,與現有的GaAs IC解決方案相比,其尺寸減小。例如,與基于GaAs的放大器相比,X波段的6 W至8 W氮化鎵功率放大器可將占位面積減少50%或更多。當試圖將這些電子設備安裝到相控陣天線的單元單元中時,這種尺寸的減少意義重大。

封裝技術的進步也使平面天線架構的成本低得多。高可靠性設計可能使用鍍金、密封外殼,內部有芯片和電線互連。這些外殼在極端環境中可能更堅固,但體積大且成本高昂。多芯片模塊 (MCM) 將多個 MMIC 器件以及無源器件組合成成本相對較低的表面貼裝封裝。MCM仍然允許混合半導體技術,以便可以最大限度地提高每個器件的性能,同時節省大量空間。例如,在前端IC的情況下,它可能包含PA、LNA和T/R開關。封裝底部的熱通孔或實心銅塊用于散熱。為了節省成本,商業、軍事和空間應用現在在許多應用中使用成本低得多的表面貼裝封裝替代方案。

相控陣波束成形器 IC

集成模擬波束成形IC,通常稱為核心芯片,旨在支持一系列應用,包括雷達、衛星通信和5G電信。這些芯片的主要功能是精確設置每個通道的相對增益和相位,以便信號在天線主波束的所需方向上相干地相干添加。它們正在為模擬相控陣應用或混合陣列架構而開發,將一些數字波束成形與模擬波束成形相結合。

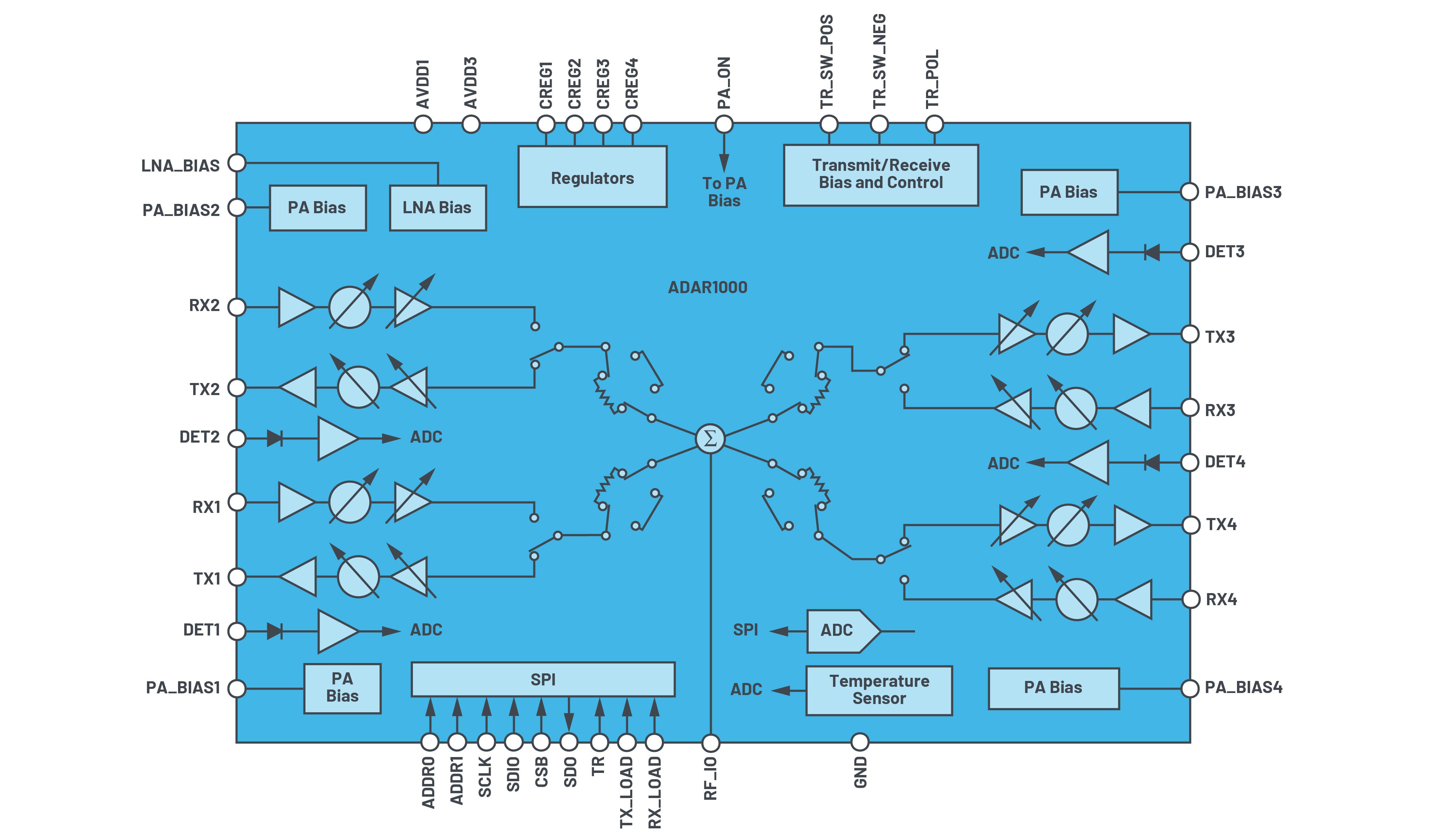

ADAR1000 X/Ku波段波束成形IC是一款4通道器件,頻率為8 GHz至16 GHz,工作在時分雙工(TDD)模式,發射器和接收器集成在一個IC中。在接收模式下,輸入信號通過四個接收通道,并組合在一個公共RF_IO引腳中。在發射模式下,RF_IO輸入信號被分割并通過四個發射通道。功能圖如圖 4 所示。

圖4.ADAR1000功能框圖

一個簡單的4線串行端口接口(SPI)控制片內寄存器。兩個地址引腳允許SPI控制同一串行線路上多達四個器件。專用的發送和接收引腳提供同一陣列中所有內核芯片的同步。單個引腳控制發射和接收模式之間的快速切換。4 通道 IC 采用 7 mm × 7 mm QFN 表面貼裝封裝,可輕松集成到平板陣列中。高集成度加上小封裝解決了高通道數相控陣架構中的一些尺寸、重量和功耗挑戰。該器件在發射模式下每通道的功耗僅為240 mW,在接收模式下每通道功耗僅為160 mW。

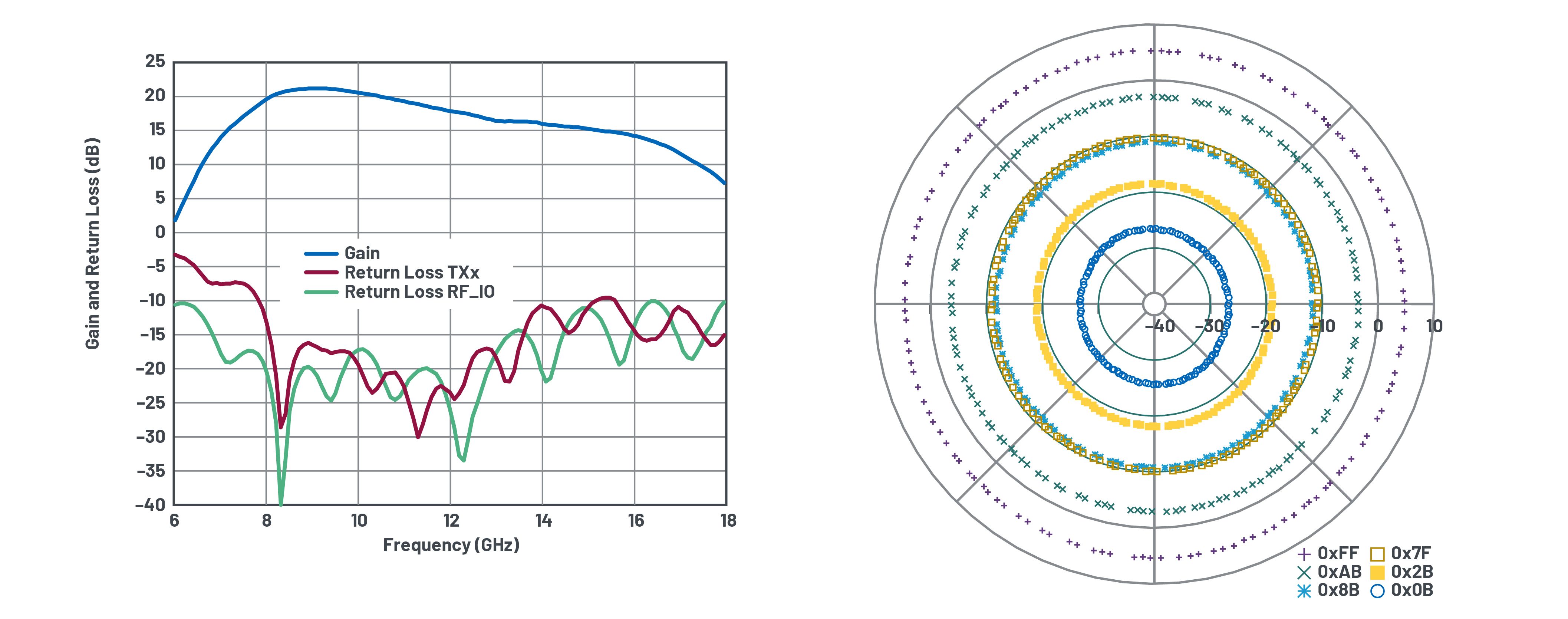

發射和接收通道直接從外部連接,設計用于與前端IC配接。圖5顯示了該器件的增益和相位圖。可實現完整的 360° 相位覆蓋,相位步長小于 2.8°,增益調整超過 30 dB。ADAR1000內置片內存儲器,可存儲多達121個波束狀態,其中一個狀態包含整個IC的所有相位和增益設置。發射器提供約19 dB增益和15 dBm飽和功率,其中接收增益約為14 dB。另一個關鍵指標是增益設置的相位變化,在20 dB范圍內約為3°。同樣,在整個360°相位覆蓋范圍內,增益隨相位的變化約為0.25 dB,這減輕了校準挑戰。

圖5.ADAR1000發射增益/回波損耗和相位/增益控制,其中頻率= 11.5 GHz。

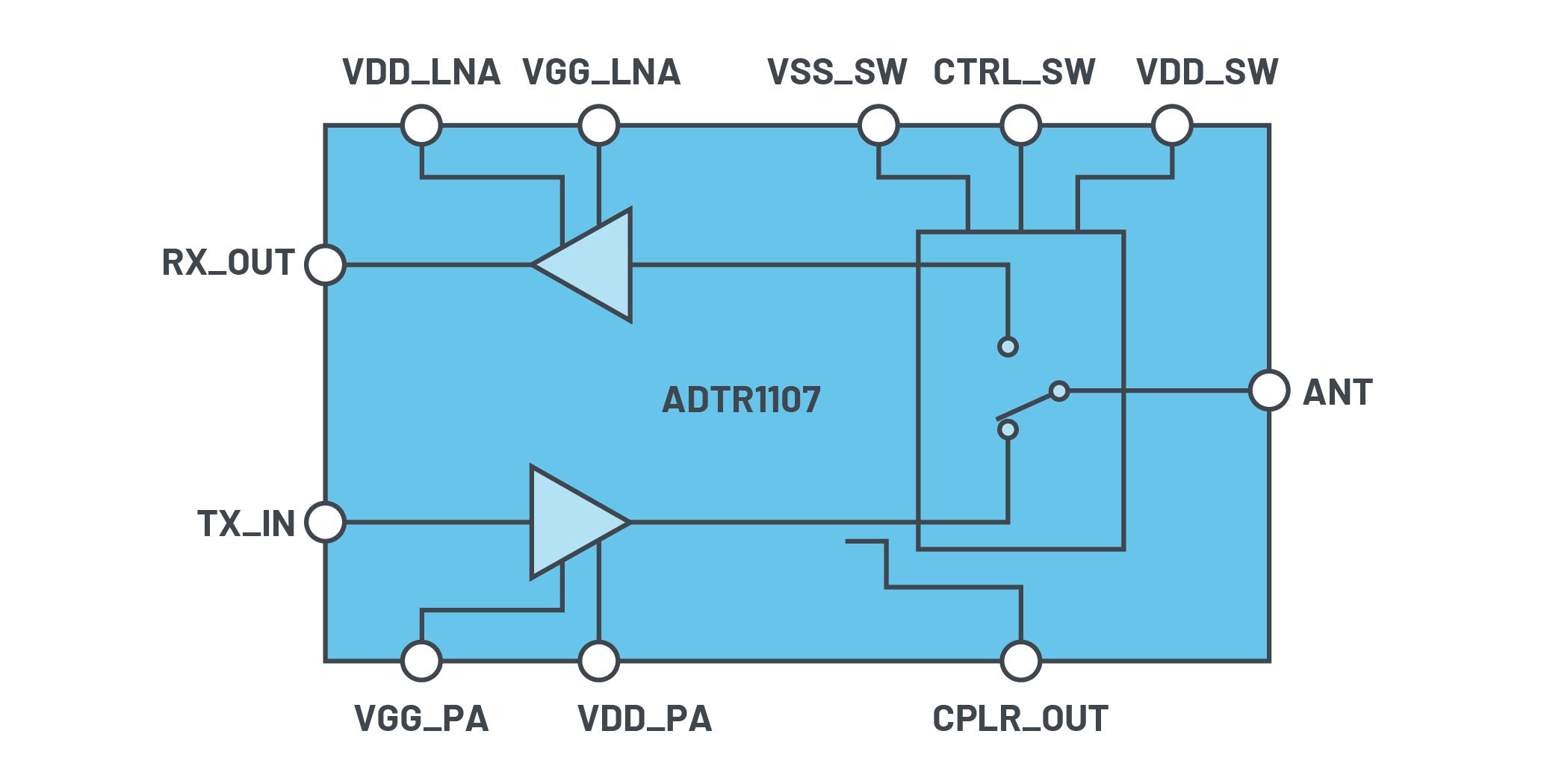

ADAR1000波束成形芯片的補充是前端IC ADTR1107。ADTR1107是一款緊湊的6 GHz至18 GHz前端IC,集成功率放大器、低噪聲放大器(LNA)和反射式單刀雙擲(SPDT)開關。功能框圖如圖6所示。

圖6.ADTR1107功能框圖

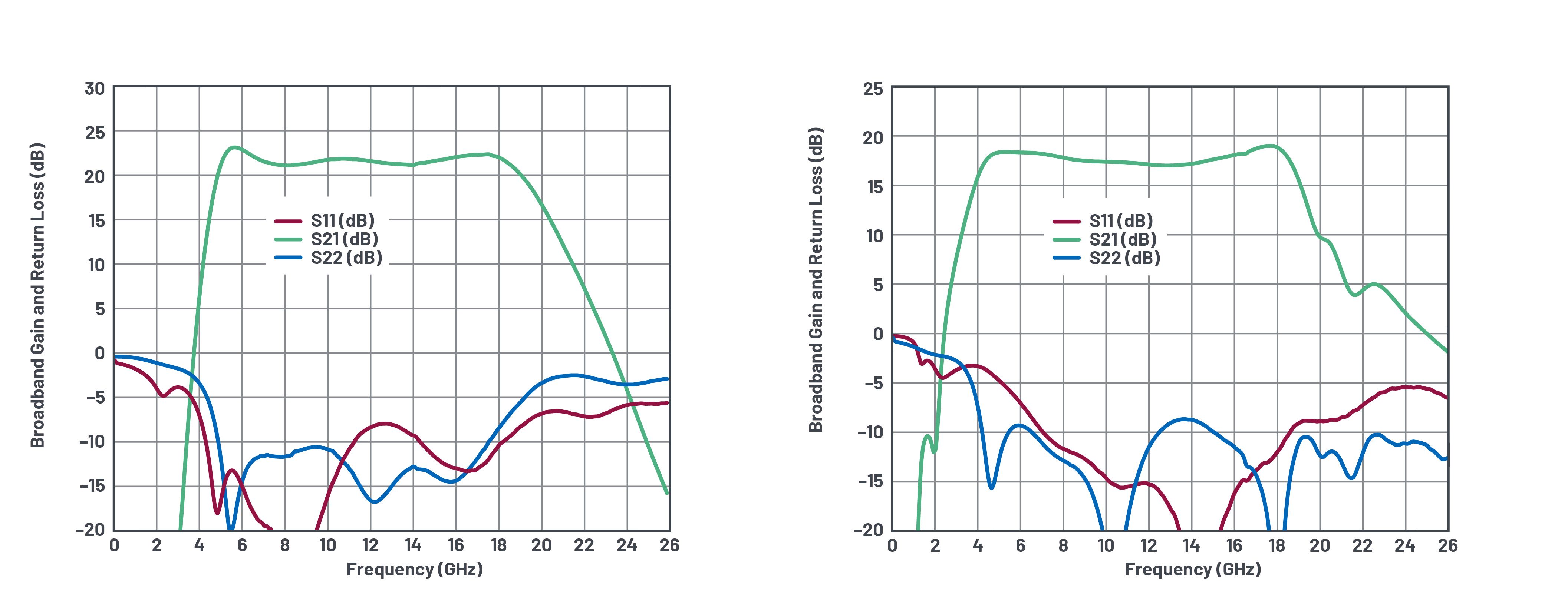

該前端IC提供25 dBm的飽和輸出功率(P坐)和發射狀態下的22 dB小信號增益,以及接收狀態下的18 dB小信號增益和2.5 dB噪聲系數(包括T/R開關)。該器件具有用于功率檢測的定向耦合器。輸入/輸出 (I/O) 在內部匹配至 50 Ω。ADTR1107采用5 mm×5 mm、24引腳焊盤柵格陣列(LGA)封裝。ADTR1107的發射和接收增益及回波損耗如圖7所示。

圖7.ADTR1107發送增益/回波損耗和接收增益/回波損耗。

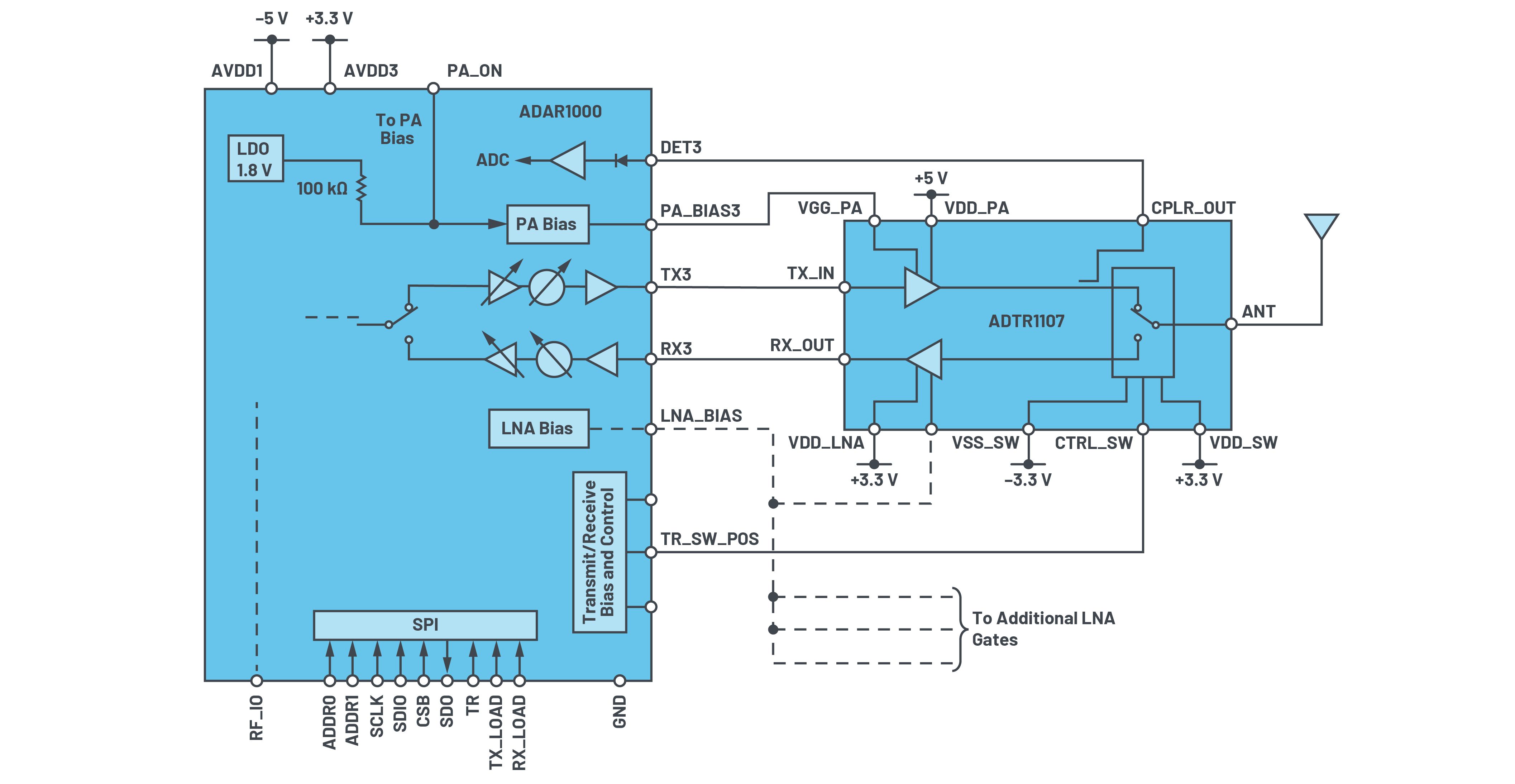

ADTR1107設計用于與ADAR1000輕松集成。接口原理圖如圖8所示。四個ADTR1107 IC由單個ADAR1000內核芯片驅動。為簡單起見,僅顯示了四個ADTR1107 IC中的一個的連接。

圖8.將 ADTR1107 葉端 IC 與 ADAR1000 X 波段和 Ku 波段波束成形器接口。

ADAR1000提供所有必需的柵極偏置電壓和控制信號,從而實現與前端IC的無縫接口。雖然ADTR1107 LNA柵極電壓是自偏置的,但也可以通過ADAR1000控制電壓。ADTR1107功率放大器的柵極電壓也由ADAR1000提供。功率放大器柵極偏置需要四個獨立的負柵極電壓,因為一個ADAR1000驅動四個ADTR1107。每個電壓由一個8位數模轉換器(DAC)設置。該電壓可通過ADAR1000 TR輸入或串行外設接口寫入來置位。置位ADAR1000 TR引腳可在接收和發送模式之間切換ADAR1000的極性。TR_SW_POS引腳可驅動多達四個開關的柵極,并可用于控制ADTR1107 SPDT開關。

ADTR1107 CPLR_OUT耦合器輸出可以連接回四個ADAR1000 RF檢波器輸入(圖4中的DET1至DET4)之一,以測量發射輸出功率。這些基于二極管的RF檢波器的輸入范圍為?20 dBm至+10 dBm。ADTR1107定向耦合器的耦合因數范圍為6 GHz時的28 dB至18 GHz時的18 dB。

ADTR1107的脈沖可以通過ADAR1000驅動的柵極電壓實現,同時漏極保持恒定。這優于通過漏極的脈沖,因為這需要高功率MOSFET開關和柵極驅動器器件,而不是低電流的柵極開關。還應該注意的是,ADAR1000輸出的功率足以使ADTR1107在發射模式下飽和,而ADTR1107設計用于在天線短路的情況下承受總反射功率。

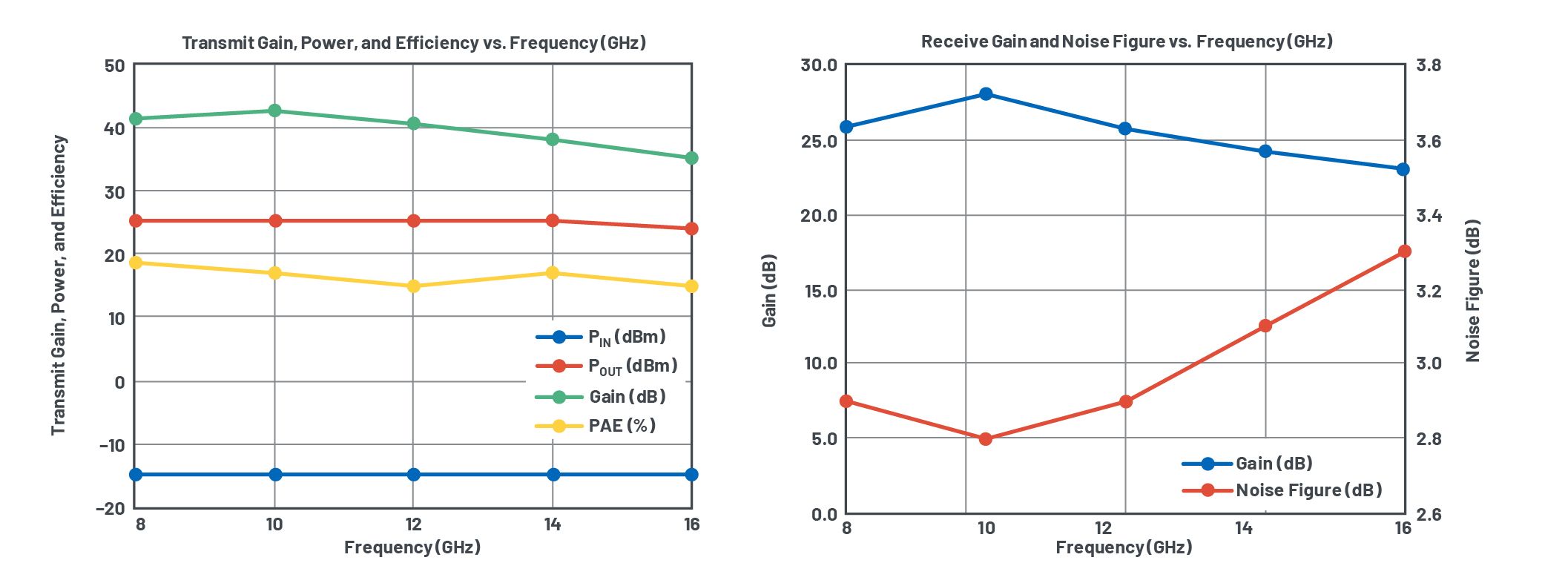

ADTR1107和ADAR1000在8 GHz至16 GHz頻率范圍內發射和接收模式下的綜合性能如圖9所示。在發射模式下,它們提供約40 dB的增益和26 dBm的飽和功率,而在接收模式下,它們提供約2.9 dB的噪聲系數和25 dB的增益。

圖9.ADTR1107與ADAR1000耦合的發送和接收性能(單通道)。

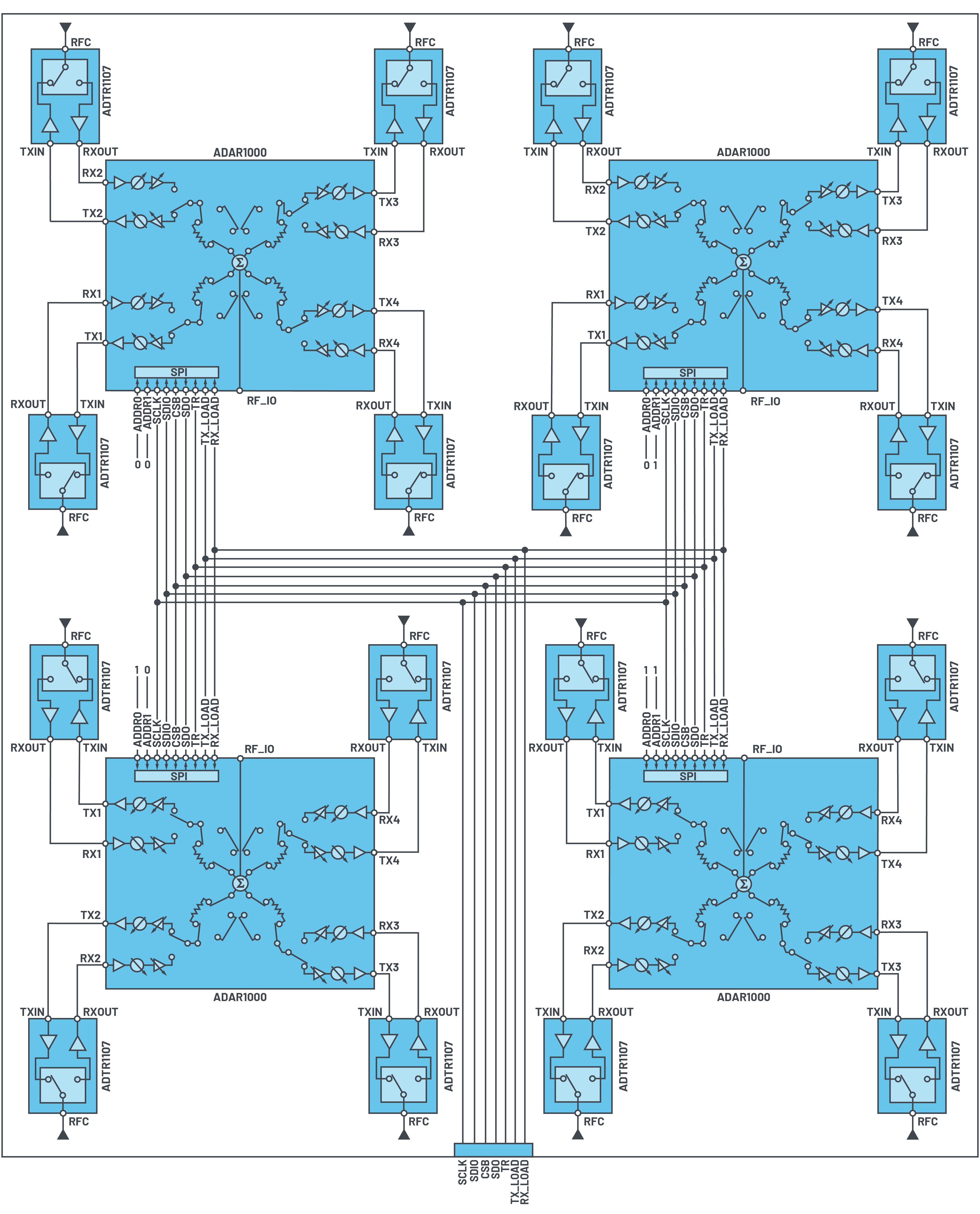

圖10顯示了驅動16個ADTR1107芯片的4個ADAR1000芯片。一個簡單的4線SPI控制所有片內寄存器。兩個地址引腳允許SPI在同一串行線路上控制多達四個ADAR1000芯片。專用發射和接收負載引腳還提供同一陣列中所有內核芯片的同步,單個引腳控制發射和接收模式之間的快速切換。

圖 10.4個ADAR1000芯片驅動16個ADTR1107芯片。

圖 11.詳細了解ADI相控陣功能

高度集成的射頻收發器芯片有助于提高天線級的集成度。ADRV9009就是這種芯片的一個例子。它提供雙發射器和接收器、集成合成器和數字信號處理功能。該器件包括一個先進的直接變頻接收器,內置高動態范圍、寬帶寬、糾錯和數字濾波功能。輔助功能包括模數轉換器(ADC)和DAC。還集成了用于功率放大器和RF前端控制的通用輸入/輸出。高性能鎖相環為發射器和接收器信號路徑提供小數N分頻RF頻率合成。它提供非常低的功耗和全面的省電模式,可在不使用時進一步節省功耗。ADRV9009采用12 mm×12 mm、196引腳芯片級球柵陣列封裝。

ADI公司為相控陣天線設計提供從天線到比特的完整信號鏈,并針對該應用優化了IC,從而加快了客戶的上市時間。IC技術的進步導致了天線設計技術的變化,推動了多個行業的變革。

審核編輯:郭婷

-

adc

+關注

關注

98文章

6513瀏覽量

545035 -

微波

+關注

關注

16文章

1044瀏覽量

83743 -

GaN

+關注

關注

19文章

1947瀏覽量

73685

發布評論請先 登錄

相關推薦

光控相控陣天線的發展歷程及工作原理

IC集成推動實現平板相控陣天線設計

【模擬對話】相控陣波束成形IC簡化天線設計

相控陣天線系統散射分析

相控陣天線實驗系統設計

相控陣天線原理_相控陣天線設計

多波束相控陣天線的應用優勢

什么是相控陣天線有源駐波測試?

IC集成支持平板相控陣天線設計

IC集成支持平板相控陣天線設計

評論