Xilinx-vivado的網表形式有edf和dcp兩個方式,兩個方式各有不同。對于仿真來說,兩者均需轉換為verilog的形式進行仿真,只是使用的命令不同。

轉換為仿真文件的命令

對于dcp文件可以在tcl中使用open_checkpoint命令或者從gui界面中選擇file->open checkpoint打開dcp文件,之后使用wirte_verilg命令就可以生成對應的Verilog文件。

對于edf文件,gui界面中沒有對應的選項,只有使用tcl命令。read_edif用于讀取edf文件,之后輸入link_desing -top xxx(xxx表示頂層名稱,不要加后綴),最后再使用write_verilog命令就可以對應生成Verilog文件。

仿真工具的支持情況

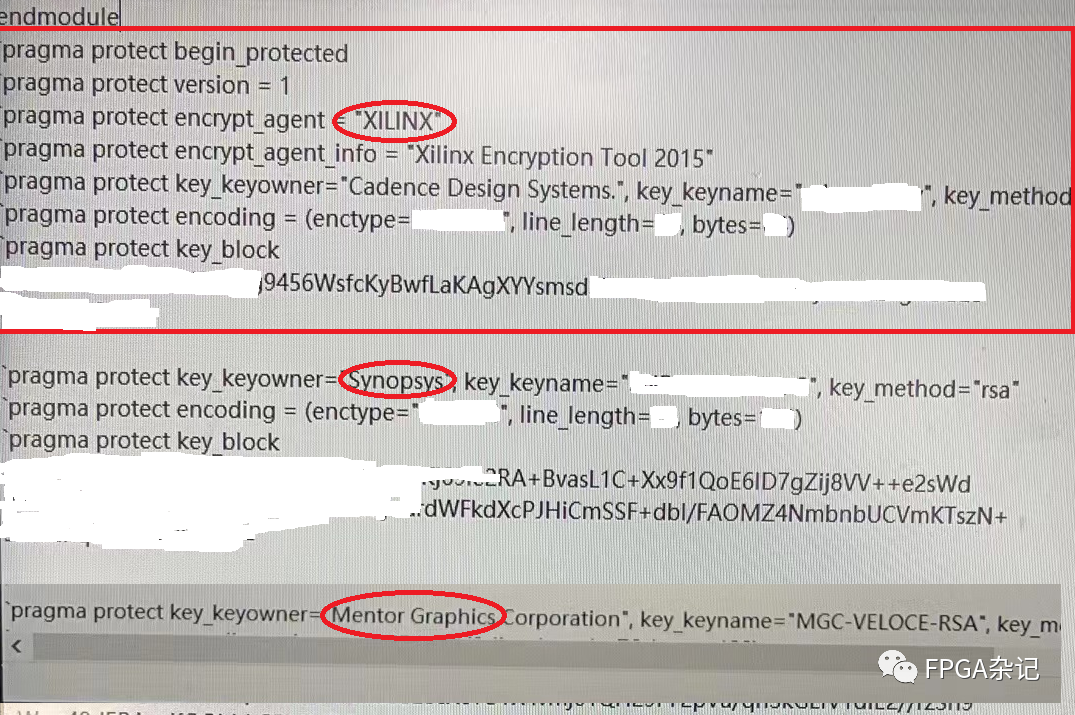

通過該以上兩種方式生成的Verilog文件均可以在vivado中進行仿真。但是,dcp生成的verilog文件可以在modelsim中進行仿真,而edf生成的Verilog文件不能在modelsim、VCS等其他廠商的工具中進行仿真。edf生成的Verilog文件不能在modelsim、VCS等廠商仿真的原因在于該Verilog中只包含了xilinx對應的秘鑰,而不包含其他廠商的秘鑰,具體可以詳見每一個生成文件末尾亂碼的起始位置。只要有對應廠商的名字,就可以在對應的工具中進行仿真。

dcp生成的Verilog文件能夠仿真的原因在于dcp格式只是一種文件打包的形式,轉換為Verilog形式之后就相當于恢復了原來的文件源碼,而源碼文件一般情況下都可以在各個廠商的仿真工具中進行仿真,除非源碼本身就包含固定的加密文件。

對于xilinx-ise的ngc格式的網表文件,使用netgen命令就可以生成對應的verilog形式的仿真文件。

PS:edif 和 dcp的區別:封裝成 edif 文件時,不能將 Xilinx ip 核封裝在文件中,而 dcp 可以;例化時,edif 是網表文件,例化時需要增加同名的 hdl 文件,dcp 文件其實是一個壓縮文件,例化時只需使用 dcp 文件即可

審核編輯:湯梓紅

-

Xilinx

+關注

關注

71文章

2167瀏覽量

121429 -

仿真

+關注

關注

50文章

4082瀏覽量

133613 -

Verilog

+關注

關注

28文章

1351瀏覽量

110101 -

網表

+關注

關注

0文章

15瀏覽量

7649 -

Vivado

+關注

關注

19文章

812瀏覽量

66539

原文標題:仿真Xilinx網表

文章出處:【微信號:FPGA雜記,微信公眾號:FPGA雜記】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

仿真Xilinx網表

仿真Xilinx網表

評論