近年來,擴頻通信技術在移動通信、個人通信、室內無線通信以及衛星通信中得到越來越廣泛的應用。對于DS-CDMA(Direct Sequence-Code Division MulTIple Access,直接序列-碼分多址)移動通信系統,因其具有較好的抗干擾性能而成為軍事通信、民用通信以及宇宙通信的一種重要的通信體制。擴頻通信的一項關鍵技術是擴頻信號的設計,以及對它的捕捉和跟蹤。在DS-CDMA移動通信中,也正是利用擴頻碼來實現用戶多址,從而使多用戶能同時共享同一頻帶進行通信。

在擴頻通信中,通常在偽隨機序列(Pseudo-random Noise,PN)的基礎上產生擴頻碼。然而,擴頻碼(PN序列)的生成一直是通信工程師最關心的問題之一。隨著FPGA(Field Programmable Gate Array,現場可編程邏輯門陣列)技術的發展,很多人采用FPGA來實現PN序列發生器。通常情況下應用FPGA來實現PN碼生成器所采用的方法是利用觸發器及邏輯門來組成線性反饋移位寄存器,從而產生所需的PN序列。然而這種方法會占用大量的觸發器資源,不利于縮小芯片面積及制造成本。SRL16 E是Xilinx公司Virtex II等系列FPGA的Slice中的基本單元,應用它來實現PN碼生成器可以大大降低FPGA中專用觸發器的使用量,從而減少FPGA片上面積的占用。

基本原理

PN碼生成器的核心是LFSR(LinearFeedback Shift Regisiter,線性反饋移位寄存器),LFSR序列共有(2N-1)種狀態(其中N為LFSR中寄存器的個數),寄存器中的數據在每個觸發時鐘周期右移一位。反饋由預先確定的寄存器引出,共同經過異或邏輯后,加到LFSR的左端。通常寄存器的個數越多生成的PN序列的長度就越長,其中生成的最長的序列成為M序列。

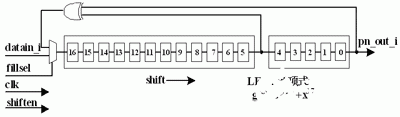

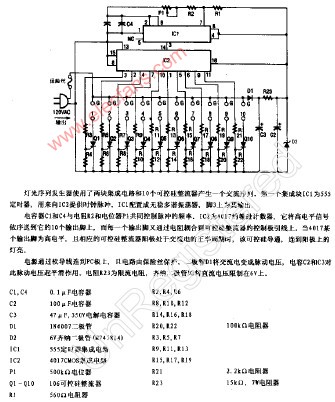

要實現LFSR序列的填充,需要在LFSR的反饋路徑中加入一個多路復用器,利用這個多路復用器將實現期望的狀態加載進去。需要注意的是在用一個特定的序列來填充時必須事先知道合適新填充的第一位從LFSR中輸出。新的填充序列必須在相同的時鐘周期內加載到LFSR中,并且新序列的第一位必須在并行加載完成后的第一個時鐘周期被移出。如圖1所示PN碼生成器的原理圖,共有17種寄存狀態。下面來看并行加載是如何實現的。如果一個并行加載發生在T=0時鐘周期,那么在T=17時鐘周期時,通過fillsel指示反饋加入。這時,移位寄存器包含反饋加入前的長度為17位原序列,這17位的原序列在反饋加入時并未受影響。在接下來的17個時鐘周期(即從T=17到T=0),原序列被移出,新的序列被移出,在T=0周期,新的序列移入完畢,反饋路徑被斷開,并在下一個時鐘周期開始驅動新序列的第一位。這樣,就如同新序列在一個單個的時鐘周期T=0被并行加載一樣。

圖1 PN碼生成器的原理圖

PN碼生成器的實現

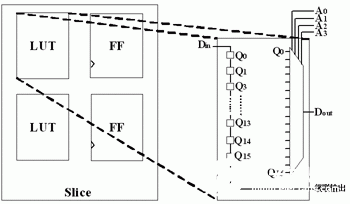

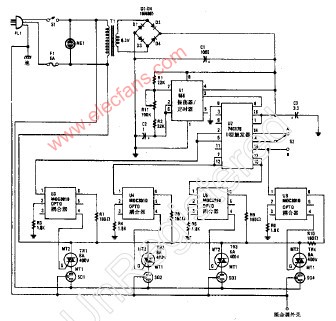

SRL16E是一種基于查找表的移位寄存器,可以非常方便地配置成多個觸發器級聯輸出的形式,因此應用SRL16E來實現PN序列,是非常高效的,并且能夠很大程度地減少FPGA資源的占用。原先SRL16E由于在配制時需要注冊而被認為比ASIC(ApplicaTIon Specific Integrated Circuit,特定用途集成電路)開銷更大。現在,它已成為FPGA中LUT(Look Up Table,查找表)配制模式的基本單元,可以非常方便地應用。并且這些基本單元在設計中應用得越多,那么設計所占用的專用觸發器資源就越少。如圖2所示為Xilinx公司Virtex II系列FPGA中的基本Slice結構示意圖。

圖2 Virtex II中的Slice結構示意圖

應用SRL16E來實現LFSR時,一個Slice就可以生成一個16階的LFSR,而用觸發器來實現時,所用Slice的數量激增為16個。由此可見,應用SRL16E可以大大降低FPGA資源的占用。

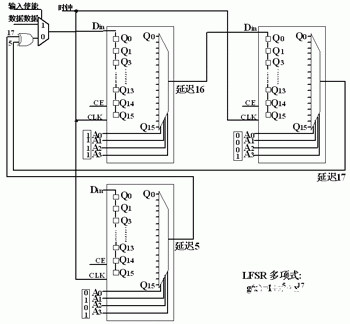

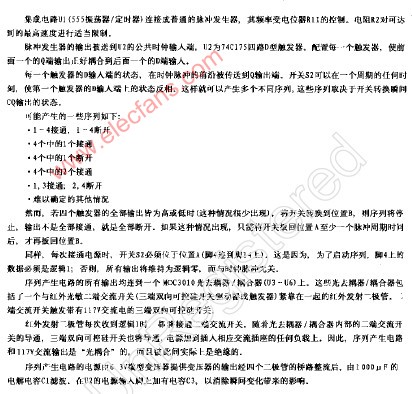

假設LFSR多項式為g(x)=1+x5+x17,即圖1所示的PN碼生成器,則應用SRL16E來實現PN碼生成器的電路圖如圖3所示。

圖3 SRL 16E構成PN碼生成器的電路圖

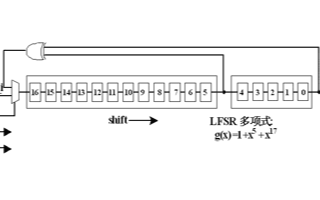

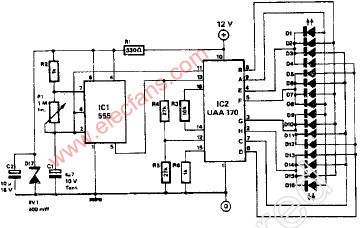

圖4為以SRL16E為基本單元,使用ISE軟件設計的PN碼生成器所得到的模塊圖。其中輸出pn_out_i對應的LFSR多項式為:

圖4 PN碼生成器模塊圖

輸出pn_out_q對應的LSFR多項式為:

對于圖4所示PN碼生成器,我們應用ISE軟件內嵌的XST(Xilinx Synthesis Technology)綜合工具對其進行綜合,得到的仿真波形如圖5所示。

圖5 PN碼生成器的XST仿真波形圖

根據ISE生成的綜合報告可得到圖4所示PN碼生成器僅僅占用4個Xilinx公司Virtex II系列FPGA的基本Slice單元,可見應用SRL16E來設計PN碼生成器可以非常有效地節省FPGA資源。

結論

應用SRL16E來實現PN碼生成器的方法可以大大節省FPGA資源的占用量,并且由于SRL16E是被優化設計的模塊,相較于傳統的方法可提高所設計PN碼生成器的效率。同時,SRL16E還可以用來實現濾波器、除法器以及波形發生器等,在大的系統中,例如整個CDMA系統,通過使用SRL16E可有效降低整個FPGA資源的占用量,從而使功耗及成本等得到進一步的降低。

-

FPGA

+關注

關注

1630文章

21769瀏覽量

604648 -

衛星通信

+關注

關注

12文章

722瀏覽量

38782 -

無線通信

+關注

關注

58文章

4587瀏覽量

143686 -

CDMA

+關注

關注

1文章

584瀏覽量

118085 -

發生器

+關注

關注

4文章

1368瀏覽量

61760

原文標題:基于FPGA實現PN序列發生器的設計

文章出處:【微信號:gh_9d70b445f494,微信公眾號:FPGA設計論壇】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

基于FPGA實現PN序列發生器的設計

基于FPGA技術的Logistic映射PN序列

【原創】基于FPGA的M序列發生器設計

FPGA的偽隨機序列發生器設計

基于TDERCS偽隨機序列發生器的FPGA設計與實現

如何使用FPGA實現混沌跳頻序列發生器

序列發生器是什么_序列發生器設計步驟

基于FPGA實現PN序列發生器的設計

基于FPGA實現PN序列發生器的設計

評論