在當今市場的許多細分市場中,交錯模數轉換器(ADC)在許多應用中具有多種優勢。在通信基礎設施中,除了對數字預失真(DPD)等線性化技術有更寬的帶寬要求外,人們還在不斷推動更高的采樣速率ADC,以允許多頻段、多載波無線電。在軍事和航空航天領域,更高的采樣速率ADC允許多用途系統可用于通信、電子監控和雷達等。在工業儀器儀表中,對更高采樣速率ADC的需求總是在增加,以便能夠充分、準確地測量更高速的信號。

首先,要準確了解交錯式ADC的含義。要理解交錯,最好看看實際發生了什么以及它是如何實現的。有了基本的了解,就可以討論交錯的好處。當然,正如許多人所知,沒有免費的午餐,因此需要評估和評估交錯的挑戰。

關于交錯

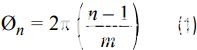

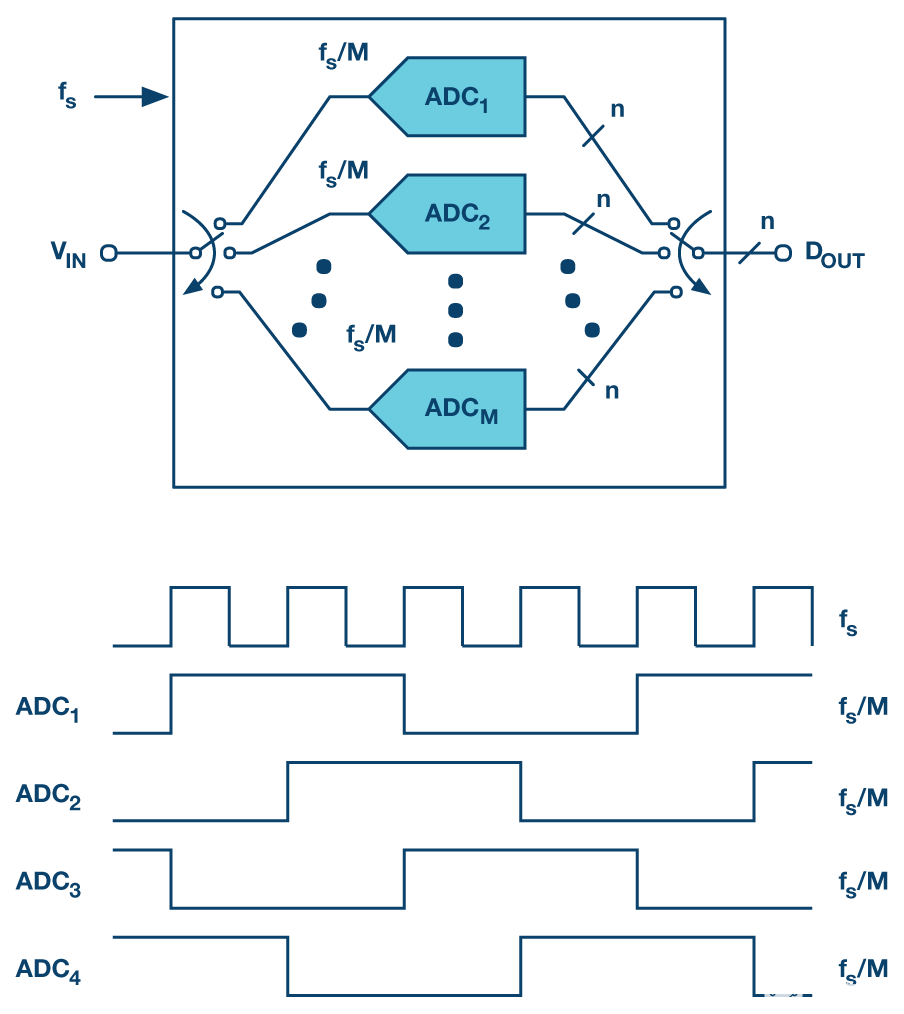

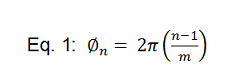

當ADC交錯時,使用兩個或多個具有定義時鐘關系的ADC同時對輸入信號進行采樣,并產生組合輸出信號,從而在單個ADC的某個倍數處產生采樣帶寬。利用m個ADC可將有效采樣速率提高m倍。為了簡單易懂,我們將重點介紹兩個ADC的情況。在這種情況下,如果兩個ADC,每個ADC的采樣速率為fS,交錯,合成采樣率僅為 2× FS.這兩個ADC必須具有時鐘相位關系,交錯才能正常工作。時鐘相位關系由公式1決定,其中n是特定的ADC,m是ADC的總數。

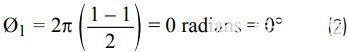

例如,兩個采樣速率為100 MSPS的ADC交錯在一起,以實現200 MSPS的采樣速率。在這種情況下,公式1可用于推導兩個ADC的時鐘相位關系,由公式2和公式3給出。

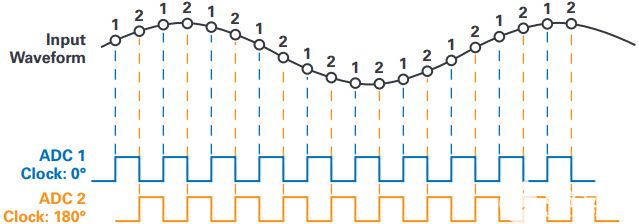

現在時鐘相位關系已知,可以檢查樣本的結構。圖1直觀地顯示了兩個100 MSPS交錯ADC的時鐘相位關系和樣本結構。請注意 180° 時鐘相位關系以及樣本的交錯方式。輸入波形由兩個ADC交替采樣。在這種情況下,交錯通過使用200 MHz時鐘輸入來實現,該輸入除以2倍和每個ADC所需的時鐘相位。

圖1.兩個交錯式100 MSPS ADC — 基本原理圖。

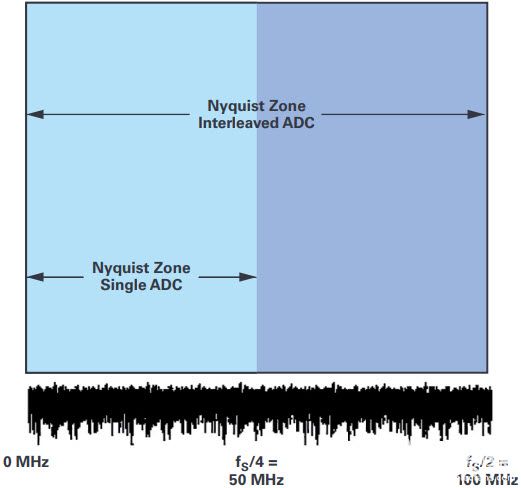

圖 2 顯示了此概念的另一個表示形式。通過交錯這兩個100 MSPS ADC,采樣速率增加到200 MSPS。這將每個奈奎斯特區從50 MHz擴展到100 MHz,使可用帶寬翻倍。增加的操作帶寬為許多細分市場中的應用帶來了許多優勢。無線電系統可以增加支持的頻段數量,雷達系統可以提高空間分辨率,測量設備可以實現更大的模擬輸入帶寬。

圖2.兩個交錯式100 MSPS ADC——時鐘和采樣。

交錯的好處

交錯的好處跨越市場的多個部分。交錯最理想的好處是交錯ADC的更寬奈奎斯特區可以增加帶寬。同樣,以兩個100 MSPS ADC交錯產生200 MSPS的采樣速率為例,圖3顯示了兩個ADC交錯允許的更寬帶寬。這為許多不同的應用創造了優勢。隨著蜂窩標準增加信道帶寬和工作頻段數量,對ADC可用帶寬的要求也越來越高。此外,在軍事應用中,對更好的空間識別以及后端通信中增加信道帶寬的要求要求ADC具有更高的帶寬。由于這些領域對帶寬的需求增加,因此需要精確測量這些信號。因此,測量設備增加了對更高帶寬的需求,以便正確采集和測量這些具有更高帶寬的信號。許多設計中的系統要求本質上都領先于商用ADC技術。交錯允許縮小其中一些間隙。

圖3.兩個交錯式ADC——奈奎斯特區。

更高的采樣速率為這些應用提供了更多的帶寬,但也允許更容易的頻率規劃,并降低通常用于ADC輸入端的抗混疊濾波器的復雜性和成本。有了所有這些好處,人們不得不想知道要付出的代價是什么。與大多數事情一樣,沒有免費的午餐。交錯式ADC提供了更高的帶寬和其他不錯的優勢,但在處理交錯式ADC時會出現一些挑戰。

交錯的挑戰

交錯ADC時,有一些挑戰和需要注意的事項。輸出頻譜中會出現雜散,這是由交錯ADC相關的缺陷引起的。這些缺陷基本上是交錯的兩個ADC之間的不匹配。有四種基本的失配會導致輸出頻譜中的雜散。這些是失調失配、增益失配、時序失配和帶寬失配。

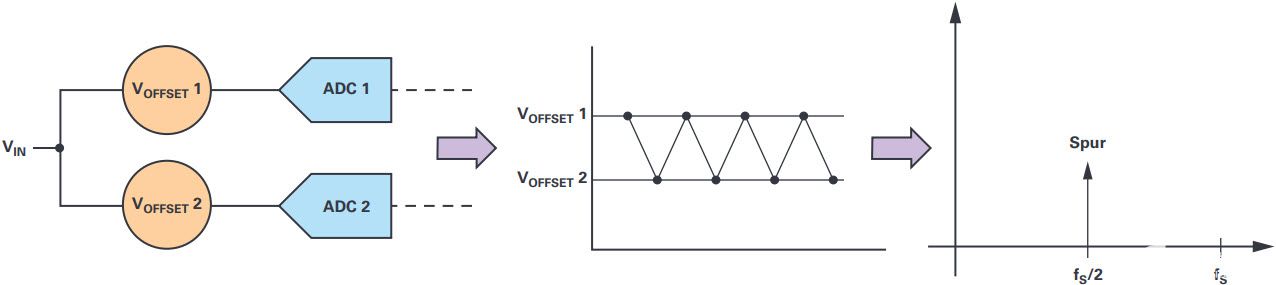

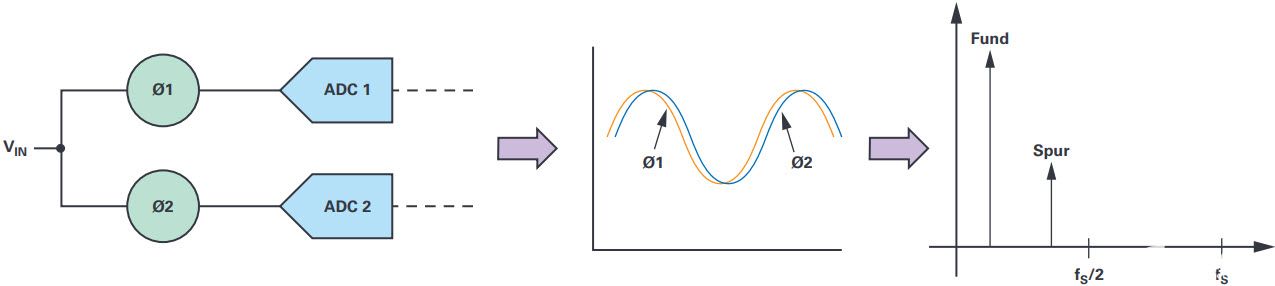

其中最容易理解的可能是兩個ADC之間的失調失配。每個ADC都有一個關聯的直流失調值。當兩個ADC交錯采集,并在兩個ADC之間交替來回采集樣本時,每個連續采樣的直流失調都會發生變化。圖4舉例說明了每個ADC如何擁有自己的直流失調,以及交錯輸出如何在這兩個直流失調值之間有效地來回切換。輸出以f的速率在這些偏移值之間切換S/2,這將導致位于 f 處的輸出頻譜出現雜散S/2.由于失配本身沒有頻率分量,并且僅在直流時,因此輸出頻譜中出現的雜散頻率僅取決于采樣頻率,并且始終以f fS/2.雜散的大小取決于ADC之間的失調失配幅度。不匹配越大,雜散就越大。為了最小化失調失配引起的雜散,無需將每個ADC中的直流失調完全歸零。這樣做會濾除信號中的任何直流成分,不適用于使用零中頻(ZIF)架構的系統,其中信號內容真實而復雜,包括直流數據。相反,更合適的技術是將其中一個ADC的失調與另一個ADC相匹配。選擇一個ADC的失調作為基準電壓源,另一個ADC的失調設置為盡可能接近該值。偏移值匹配得越好,產生的雜散在 f 處越低S/2.

圖4.偏移不匹配。

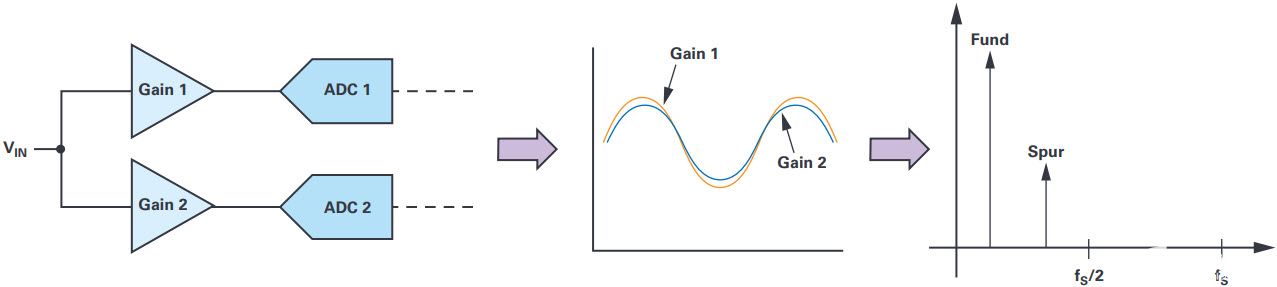

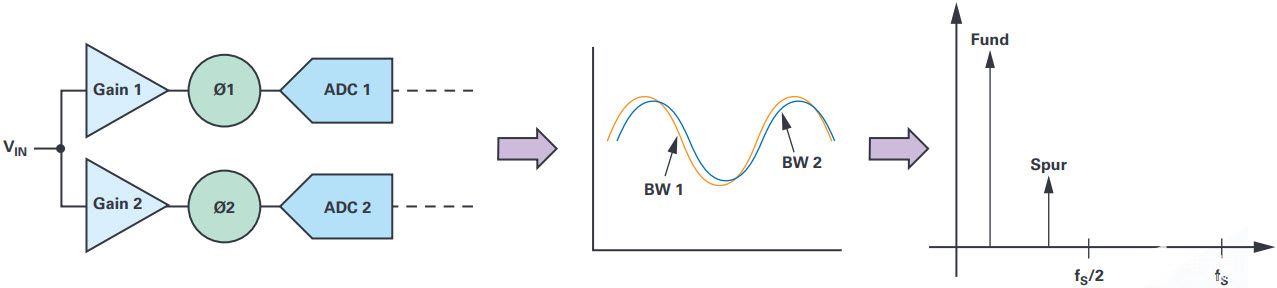

交錯時要注意的第二個失配是ADC之間的增益失配。圖5給出了兩個交錯轉換器之間的增益失配表示。在這種情況下,不匹配存在頻率分量。為了觀察這種失配,必須向ADC施加一個信號。在失調失配的情況下,無需信號即可查看兩個ADC的固有直流失調。在增益失配的情況下,除非存在信號并且可以測量增益失配,否則無法看到增益失配。增益失配將導致輸出頻譜中出現與輸入頻率和采樣速率相關的雜散,并將出現在fS/2 ± f在.為了最小化增益失配引起的雜散,采用了與失調失配類似的策略。其中一個ADC的增益被選為基準電壓源,另一個ADC的增益設置為盡可能接近該增益值。每個ADC的增益值相互匹配得越好,產生的雜散在輸出頻譜中就越少。

圖5.增益不匹配。

接下來,我們必須檢查兩個ADC之間的時序不匹配。時序失配有兩個分量:ADC模擬部分的群延遲和時鐘偏斜。ADC內的模擬電路具有相關的群延遲,兩個ADC之間的值可能不同。此外,時鐘偏斜在每個ADC中都有一個孔徑不確定性分量,并且有一個與輸入到每個轉換器的時鐘相位精度相關的分量。圖6直觀地顯示了ADC中時序失配的機制和影響。與增益失配雜散類似,時序失配雜散也是輸入頻率和采樣速率的函數,出現在fS/2 ± f在.

圖6.時序不匹配。

為了最小化產生的雜散,需要通過每個轉換器模擬部分的群延遲與良好的電路設計技術進行適當匹配。此外,時鐘路徑設計需要緊密匹配,以盡量減少孔徑不確定性差異。最后,需要精確控制時鐘相位關系,使兩個輸入時鐘盡可能接近180°。與其他不匹配一樣,目標是嘗試最小化導致時序不匹配的機制。

最后一個不匹配可能是最難理解和處理的:它是帶寬不匹配。如圖7所示,帶寬失配具有增益和相位/頻率分量。這使得帶寬不匹配更加困難,因為它包含來自其他兩個不匹配參數的組件。然而,在帶寬不匹配的情況下,我們在不同的頻率下看到不同的增益值。此外,帶寬具有定時分量,導致不同頻率的信號通過每個轉換器具有不同的延遲。最小化帶寬失配的最佳方法是采用非常好的電路設計和布局實踐,以最大程度地減少ADC之間的帶寬不匹配。每個ADC匹配得越好,產生的雜散就越小。正如增益和時序失配導致輸出頻譜在f處產生雜散一樣S/2 ± f在,帶寬失配也會導致相同頻率下的雜散。

圖7.帶寬不匹配。

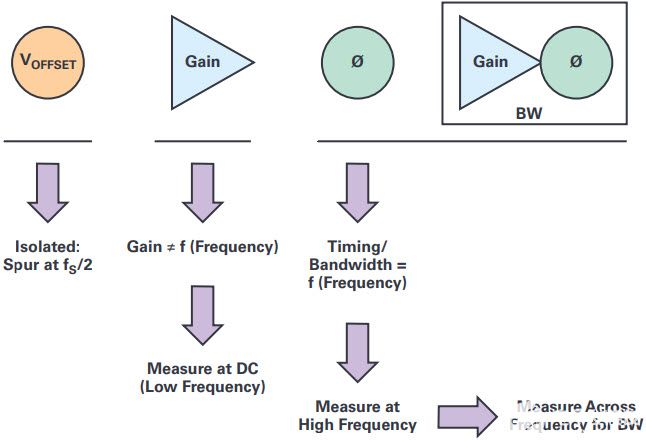

既然我們已經討論了四種不同的失配,它們在交錯ADC時會導致問題,很明顯已經出現了一個共性。四個失配中的三個在f處的輸出頻譜中產生雜散S/2 ± f在.失調失配雜散很容易識別,因為它單獨位于fS/2,可以相當容易地得到補償。增益、時序和帶寬失配都會在f處產生雜散。S/2 ± f在在輸出頻譜中,所以問題是如何識別每個頻譜的貢獻。圖8提供了從交錯ADC的不同失配中識別雜散源的過程的快速可視化指南。

圖8.交錯不匹配的相互關聯性質。

如果僅從增益失配來看,則屬于低頻或直流失配類型。通過在接近直流的低頻下進行增益測量,然后在較高頻率下執行增益測量,可以將帶寬失配的增益分量與增益失配分開。增益失配不像帶寬失配的增益分量那樣是頻率的函數。時序不匹配也采用類似的方法。在接近直流的低頻下進行測量,然后在較高頻率下進行后續測量,以將帶寬失配的時序分量與時序失配分開。

結論

最新的通信系統設計、尖端的雷達技術和超高帶寬測量設備似乎不斷超越現有的ADC技術。他們的要求促使ADC的用戶和制造商開發滿足這些需求的方法。交錯式ADC允許以比提高典型ADC轉換速率的傳統路徑更快的速度實現更大的帶寬。通過采用兩個或多個ADC并將它們交錯在一起,可以增加可用帶寬,并且可以更快地滿足系統設計要求。然而,交錯ADC并非免費,ADC之間的失配也不容忽視。即使不匹配確實存在,了解它們以及如何適當地處理它們也可以使設計人員更智能地使用這些交錯式ADC,并滿足其最新系統設計不斷增長的需求。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8703瀏覽量

147183 -

adc

+關注

關注

98文章

6498瀏覽量

544660 -

無線電

+關注

關注

60文章

2143瀏覽量

116476

發布評論請先 登錄

相關推薦

交錯式ADC的基礎知識

有ADC和傳感器的基礎知識嗎?

交錯式功率因數校正

ADC轉換器的基礎知識詳細資料說明

交錯ADC:揭開謎團

交錯式ADC的基礎知識

交錯式ADC的基礎知識

評論