作者:David Brown and Peter Delos

電子戰(zhàn) (EW) 接收器(特別是信號情報 (SIGINT) 應用)對更高帶寬和更小尺寸、重量和功耗 (SWaP) 的需求一直存在,這促使電子戰(zhàn)系統(tǒng)設計人員不斷尋找高速模數轉換器 (ADC) 技術的新發(fā)展和改進。雖然65 nm ADC接近其固有的工藝相關性能和帶寬限制,但新的28 nm RF ADC超越了這些界限,為下一代寬帶接收器系統(tǒng)奠定了新的基礎。28 nm工藝節(jié)點的晶體管寬度更小,寄生效應更低,可實現更快的采樣速率、更寬的模擬輸入帶寬、集成的數字功能和新的接收器架構,同時降低功耗和整體尺寸。

28 nm 模數轉換器的優(yōu)勢

隨著寬帶電子戰(zhàn)系統(tǒng)在現代戰(zhàn)場上變得越來越普遍,系統(tǒng)設計人員面臨著許多挑戰(zhàn),即如何實現下一代電子戰(zhàn)接收器所需的更高性能和更低的SWaP。高速ADC是所有寬帶電子戰(zhàn)接收器的主要設計考慮因素之一,在很大程度上決定了系統(tǒng)架構以及整體檢測和觀察能力。高速ADC的許多性能特征,包括采樣速率、帶寬和分辨率,是決定接收器其余部分設計的因素——從模擬RF域到DSP要求。隨著電子戰(zhàn)系統(tǒng)設計人員不斷開發(fā)下一代電子戰(zhàn)接收器,對更高ADC帶寬和更高分辨率的需求仍然是永恒的行業(yè)趨勢。更高的采樣速率和帶寬允許一次數字化更多頻譜,從而緩解RF領域的設計挑戰(zhàn)并減少掃描時間,同時更大的位深度可提高性能并減少誤報和檢測。這種對更高采樣速率和更好分辨率的永不滿足的需求促使高速ADC制造商轉向越來越小的晶體管光刻節(jié)點(目前為28 nm和16 nm),以便在不增加器件功耗的情況下實現這些要求。

28 nm ADC的基本優(yōu)勢是實現下一代寬帶電子戰(zhàn)接收器不可或缺的一部分,并為構建未來系統(tǒng)奠定了新的基礎。28 nm晶體管降低了寄生柵極電容,由于驅動開關所需的能量較低,因此可實現更快的開關。正因為如此,以及28 nm工藝的物理晶體管尺寸更小,ADC不僅可以實現更快的采樣速率,而且每平方毫米可以容納更多數量的晶體管,從而有可能實現更大的數字處理能力。考慮到固有的低功耗,采用28 nm工藝的ADC是下一代電子戰(zhàn)系統(tǒng)中的關鍵推動因素,其性能和能力要求以前在≥65 nm工藝上被認為是不切實際的。對于大多數電子戰(zhàn)系統(tǒng)設計人員來說,28 nm ADC可實現更高的采樣速率(幾GSPS及以上),這是最具吸引力的ADC特性之一,特別是對于SIGINT、電子保護(EP)和電子支持(ES)應用。與ADC帶寬同樣重要的是分辨率,它允許更高的SNR/SFDR以及隨后檢測、觀察和處理目標信號的能力。低于 1 的欠采樣圣由于更高的模擬輸入帶寬,奈奎斯特也是可能的。

轉向28 nm工藝還允許混合信號半導體制造商將越來越多的數字信號處理和功能集成到其高速ADC中,而無需增加(甚至減少)系統(tǒng)SWaP。集成 NCO(數控振蕩器)和 DDC(數字下變頻器)等數字特性突破了轉換器性能極限,緩解了與更高轉換器數據速率和高數字接口功耗相關的系統(tǒng)設計挑戰(zhàn)。利用更小的28 nm工藝和提高ADC的片內DSP功能,還可以減輕處理器的大部分處理負載和功耗,使電子戰(zhàn)系統(tǒng)設計人員能夠降低系統(tǒng)SWaP。

雖然更快的28 nm ADC可以捕獲和觀察更大的RF頻譜,但與ADC奈奎斯特帶寬相比,目標信號的帶寬可能仍然相對較小。此外,GSPS ADC的大量數據吞吐量可能導致尋找合適的處理器并將其與ADC物理接口的挑戰(zhàn)。目前市場上的許多28 nm轉換器在10 Gbps以上的通道速率下使用JESD204B接口標準,這可能會帶來與路由Gbps SERDES(串行器/解串器)JESD通道相關的電路板布局和信號完整性挑戰(zhàn)。幸運的是,通過集成NCO/DDC和片上DSP,ADC可以將目標信號轉換為較低的頻率或基帶,應用數字濾波,并抽取數字數據輸出速率,以便對捕獲頻譜的部分執(zhí)行更密集的處理。可調諧NCO允許DDC掃描數字化頻譜,以便仍然可以分析整個頻譜,但具有處理增益和較低數字數據輸出速率的額外好處。并行添加多個 NCO 和 DDC 允許用戶在 DDC 之間預配置并快速切換和快速跳躍,從而進一步縮短掃描時間,因為從等式中刪除了 NCO 調諧。集成的DDC還可以顯著節(jié)省數字JESD204B接口的功耗。以如此高的速率運行的JESD SERDES可能會增加一瓦特或更多的系統(tǒng)功耗,因此將數據速率降低到較低的速度在這方面非常有益。隨著高速ADC不斷向更高的采樣速率、位深度和帶寬邁進,集成DDC和ADC對寬帶電子戰(zhàn)接收器系統(tǒng)設計人員更具吸引力,因為低SWaP處理器可能難以處理來自ADC的大量數字數據。有關DDC的更多信息和一些實際示例,請參閱Jonathan Harris的“數字下變頻器怎么了”第1部分和第2部分。

實現新的接收器架構

外差接收器架構已廣為人知,并已經過多年的驗證。從歷史上看,許多微波接收器都采用雙下變頻架構實現。對于前幾代ADC而言,工作頻段頻率與ADC輸入頻率的較大比率使得使用單個下變頻接收器架構無法進行鏡像濾波。采樣速率和模擬輸入帶寬均增加的新型ADC現在使高性能寬帶單下變頻架構變得實用且易于實現。

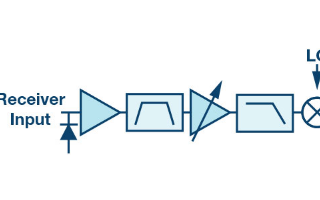

單個下變頻接收器架構示例如圖1所示。選擇前端LNA是為了提高噪聲系數性能。如果需要,在LNA前面添加一個限幅器,以提高前端的生存功率能力。工作帶濾波器用于衰減帶外干擾。接下來,可以根據需要添加額外的增益和/或增益控制。在混頻器之前,低通濾波器可以減少RF諧波,這些諧波會增加混頻雜散輸出。混頻器是一個關鍵的構建模塊,選擇混頻器是為了優(yōu)化目標頻帶的性能。混頻器之后的另一個低通濾波器在放大前對上邊帶進行濾波。根據需要增加額外的中頻增益。抗混疊濾波器通常是ADC之前的最后一個元件,可抑制采樣過程中可能折疊在帶內的任何頻率。ADC是下一個,雖然它是鏈中的最后一個,但通常是第一個選擇的組件,而接收器的其余部分則圍繞ADC構建。

圖1.單下變頻接收器架構示例。

接下來,我們將回顧選擇頻率計劃選項時的一些注意事項。頻率規(guī)劃是選擇頻率轉換方法的過程,當使用可用組件實施時,通過合理的濾波器設計產生最低的雜散性能。當RF工程師第一次做出這個決定時,次優(yōu)頻率計劃有許多選擇和影響,可能會使這成為一項艱巨的任務。幸運的是,CAD工具和可用組件的現代進步使頻率規(guī)劃成為一項更易于管理的任務。

一般來說,較高的IF頻率在2德·或 3RD從雜散角度來看,ADC奈奎斯特區(qū)是首選。我們將首先展示將 10 GHz 工作頻段轉換為 1 的頻率計劃來概述其優(yōu)勢圣3 GHz ADC的奈奎斯特,然后顯示工作在2 GHz ADC中時的優(yōu)勢德·奈奎斯特區(qū)。

圖 2 顯示了 1 GHz 工作頻段在 10 GHz 下到 1 的頻率轉換圣3 GSPS ADC 的奈奎斯特區(qū)。說明了兩個主要問題。首先,RF鏡像頻率與工作頻段的距離非常近,需要一個非常困難的濾波器來進行鏡像抑制。其次,從IF放大級創(chuàng)建的任何IF都是帶內,無法被抗混疊濾波器濾波。

圖2.頻率規(guī)劃有問題:中頻諧波在中頻頻帶內,這使得鏡像濾波變得困難。

圖3顯示了在2德·奈奎斯特區(qū)。較高的IF頻率導致鏡像頻率遠離工作頻段,RF鏡像濾波器明顯更容易實現。此外,中頻放大器中產生的任何諧波都可以通過抗混疊濾波器濾除,并且將產生的唯一中頻諧波是ADC本身內部的諧波。

圖3.改進的頻率規(guī)劃:IF諧波在IF頻段之外,這意味著可以實現鏡像濾波。

使用是德科技 Genesys 工具進行雜散分析可以快速得出相同的結論。圖4來自WhatIF頻率規(guī)劃工具。圖4顯示了WhatIF頻率規(guī)劃工具,該工具設置為10 GHz工作頻段、1 GHz瞬時帶寬、高端LO選擇以及搜索高達五階雜散。無支線區(qū)以綠色表示,在本例中,落在 2德·3 GSPS ADC 的奈奎斯特區(qū)。

圖4.使用是德科技 Genesys WhatIF 頻率規(guī)劃工具進行雜散分析。

組件啟用程序

作為任何頻率規(guī)劃分析的后續(xù)工作,應在接收器的預期工作條件下評估混頻器和ADC,以驗證雜散和噪聲性能。

最近發(fā)布的高性能3 GHz至20 GHz混頻器包括LTC5552和LTC5553。圖 5 顯示了這些器件的主要特性。這些是同類最佳的高線性度寬帶混頻器,可直接裝入寬帶接收器架構。主要區(qū)別在于 LTC5552 具有一個差分 IF 輸出,而 LTC5553 在所有端口上均為單端。差分IF輸出允許整個IF鏈保持差分,從而消除了通常添加到ADC輸入的巴倫。差分中頻放大器可通過實現完全差分中頻部分而輕松獲得,唯一的設計調整是在中頻信號鏈中引入差分濾波器。

圖5.寬帶、高性能、高線性度混頻器。

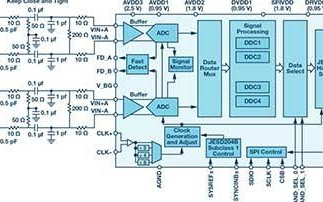

最近發(fā)布的28 nm ADC是AD9208,這是一款14位、3 GSPS雙通道ADC,具有本文前面提到的許多特性集和特性。高輸入帶寬和采樣分辨率以及四個集成DDC和NCO等數字特性使AD9208非常適合許多電子戰(zhàn)接收器系統(tǒng)和應用。此外,9 GHz的高模擬輸入帶寬允許AD9208直接采樣至2德·和 3RD奈奎斯特頻率。甚至 4千奈奎斯特采樣可通過干凈的低抖動參考時鐘實現,以最大限度地減少較高輸入頻率下的SNR下降。

RF接收器設計人員面臨的一個持續(xù)挑戰(zhàn)是,每個關鍵的ADC指標都會隨著輸入頻率而降低。對于噪聲和無雜散動態(tài)范圍都是如此。除了硅的限制之外,還需要仔細的封裝設計,以適應從硅到封裝層壓板以及從封裝到PWB的RF發(fā)射,以保持GHz轉換器的輸入帶寬。

設計良好的RF I/O結構會隨著輸入頻率的降低而逐漸下降。在設計中不考慮這些因素,通常會有一個輸入頻率,性能會急劇下降。圖 7 從概念上對此進行了說明。在為應用篩選轉換器時,在提交設計之前需要花費大量精力來驗證性能。對于工作在GHz頻率下的RF采樣ADC,這一點變得越來越重要,在為應用選擇ADC之前,應充分了解性能響應與頻率的關系。

結論

本文回顧了幾種寬帶應用和接收器設計考慮因素。電子戰(zhàn)應用尤其具有挑戰(zhàn)性,因為接收器具有寬工作頻段和盡可能多的瞬時帶寬。這些挑戰(zhàn)表明,對于單下變頻接收器架構,在較高的ADC奈奎斯特區(qū)工作將產生更好的雜散性能。該目標對ADC的輸入帶寬和混頻級的性能參數提出了挑戰(zhàn)。幸運的是,使能組件,包括具有擴展輸入頻率范圍的高速28 nm ADC和寬帶高線性度混頻器,現在可用于為下一代接收器奠定基礎。圖 6 顯示了一個完整的保護解決方案。

圖6.AD9208: 28 nm 3 GSPS、高性能、寬輸入帶寬ADC。

圖7.模擬性能:SNR、SFDR和信號功率都會隨輸入頻率而降低。針對中頻采樣的設計需要驗證所選ADC不會隨著所需輸入頻率而顯著降低。此外,在PWB設計中實現時,需要謹慎的RF布局技術。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8741瀏覽量

147675 -

接收器

+關注

關注

14文章

2477瀏覽量

72078 -

adc

+關注

關注

99文章

6530瀏覽量

545378

發(fā)布評論請先 登錄

相關推薦

LTM9003CV-AA#PBF模數轉換器

AD9689BBPZ-2000模數轉換器現貨

AD9689BBPZ-2600模數轉換器現貨

AD9689BBPZ-2600模數轉換器銷售

AD9689BBPZ-2000模數轉換器銷售

AD9689BBPZ-2000模數轉換器

AD9208BBPZRL-3000模數轉換器

5962-9581501HXA高端AD模數轉換器

AD7878SQ高端AD模數轉換器IC 訂貨***

AD574ASE/883B高端AD模數轉換器IC

模數轉換器ADC簡介

電流積分模數轉換器(ADC),什么是電流積分模數轉換器(AD

下一代電子戰(zhàn)接收器系統(tǒng)可由28納米模數轉換器支持

利用ADI RF轉換器打造一個帶DPD接收機的直接RF發(fā)射機

28nm模數轉換器支持下一代電子戰(zhàn)接收器系統(tǒng)

28nm模數轉換器支持下一代電子戰(zhàn)接收器系統(tǒng)

評論