作者:Kris Lokere and Gabino Alonso

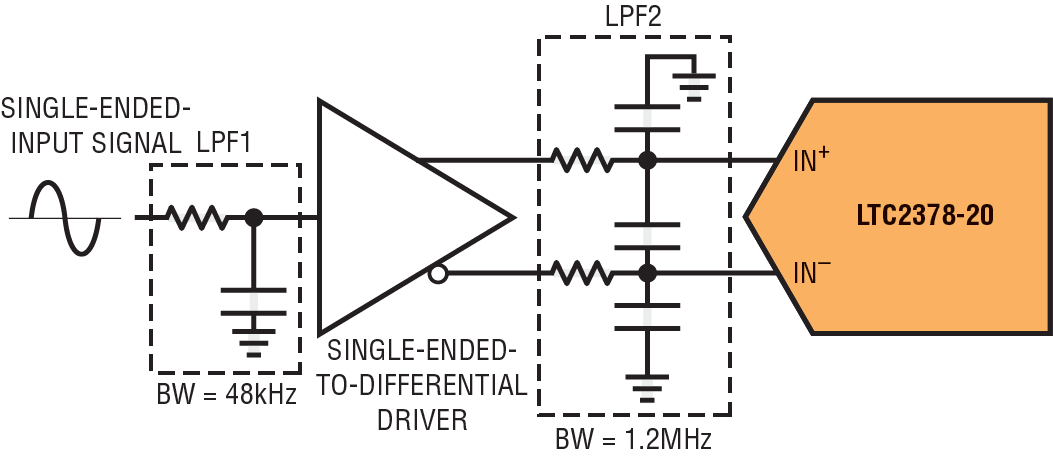

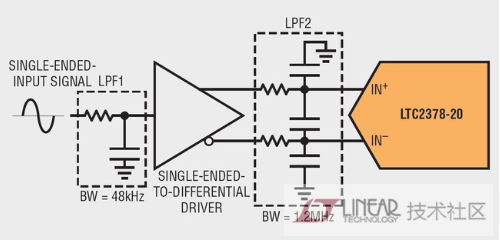

隨著ADC分辨率和采樣速率的不斷提高,模擬輸入的驅動器電路(而不是ADC本身)日益成為決定整體電路精度的限制因素。除了用于噪聲輸入信號的簡單1極點RC低通濾波器(LPF1)(圖1)之外,緩沖器和ADC輸入之間通常使用耦合RC濾波器網絡(LPF2),以最大程度地減少ADC采樣瞬變反射到緩沖器的干擾。模擬輸入端的長RC時間常數會減慢這些干擾的建立速度。因此,LPF2 通常需要比 LPF1 更寬的帶寬。該濾波器還有助于最大限度地減少緩沖器的噪聲貢獻。

圖1.仿真放大器和ADC之間的接口有助于確定噪聲和建立時間之間的權衡。

仿真放大器和ADC之間的接口,在建立時間和噪聲性能之間提出了一些有趣的權衡。對此類仿真進行實驗有助于直觀地了解濾波器設計如何影響這些性能方面。

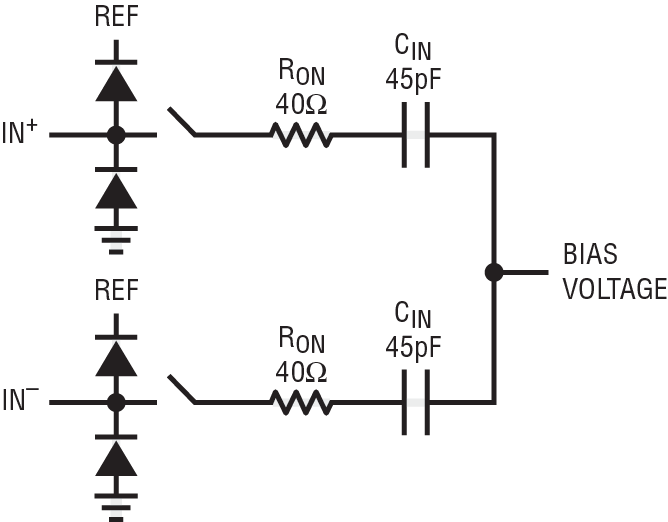

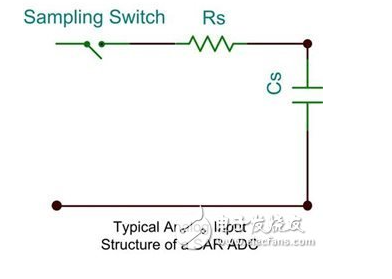

全差分SAR ADC的模擬輸入可以建模為驅動電路上的開關電容負載,如圖2所示。所示值來自 LTC2378-20 20 位、1Msps、低功率 SAR ADC,但可輕松修改以表示其他 ADC。在采集階段,每個輸入從采樣CDAC獲得約45pF (CIN),從采樣開關的導通電阻看到40Ω (RON)。輸入在此相位為 CIN 電容器充電時會吸收電流尖峰。在隨后的轉換階段,模擬輸入僅吸收很小的漏電流,電容完全放電。這種 ADC 模擬輸入建模突出了將放大器耦合到 SAR ADC(如 LTC2378-20)的最大挑戰之一;處理每個采集階段開始時ADC輸入端消耗的電流尖峰。

圖2.SAR ADC模擬輸入的等效電路。

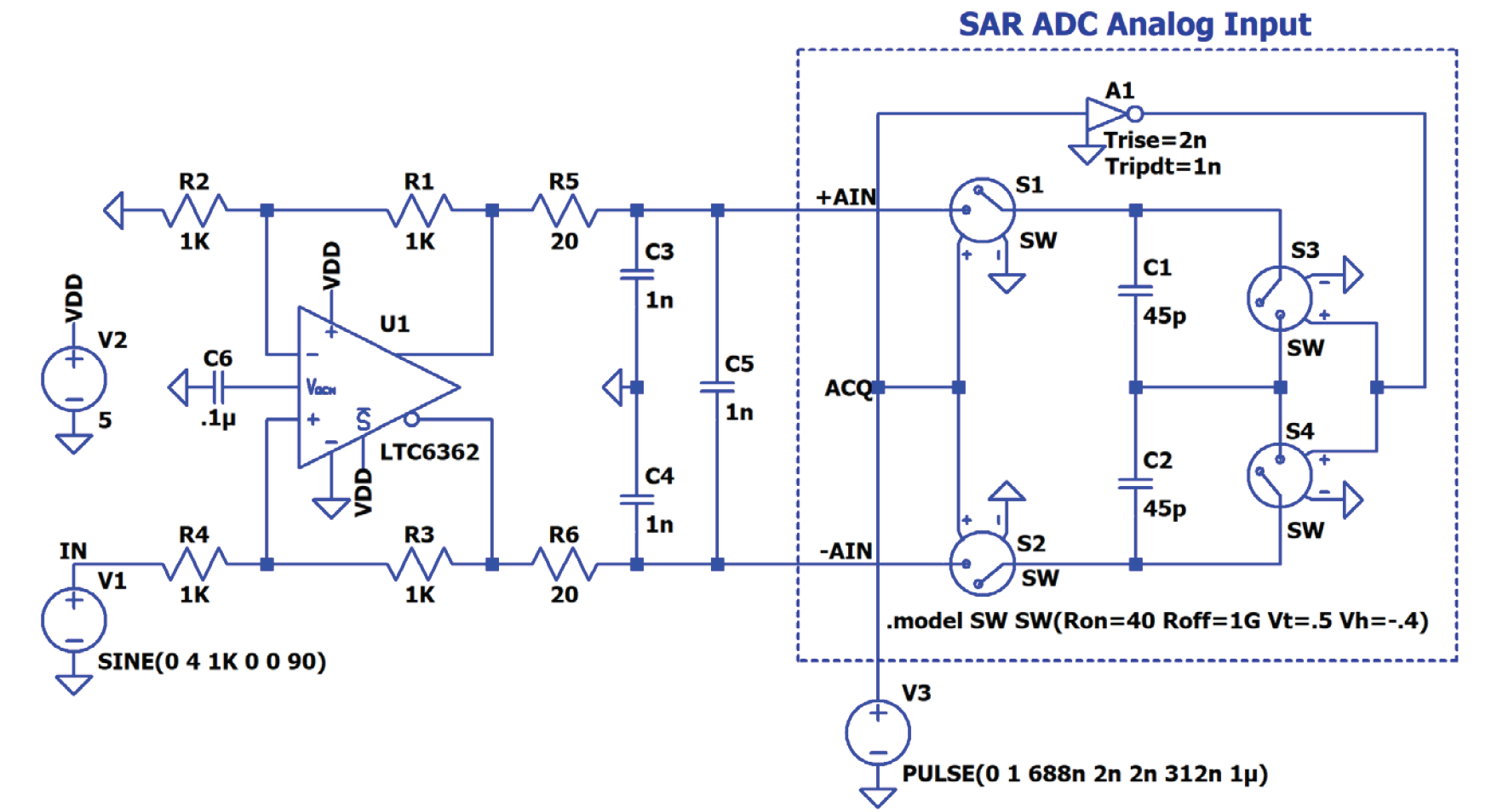

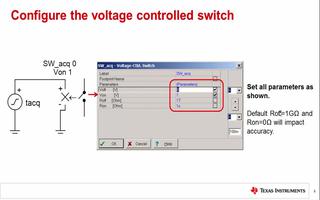

該等效電路的仿真原理圖如圖3所示。低功率差分運放 LTC6362 配置為將一個單端輸入信號轉換為一個全差分輸出以驅動 LTC2378-20。為了簡化仿真,不包括輸入ESD保護二極管。兩個45pF輸入電容(C1和C2)通過穩壓開關(S1和S2)充電,這些開關由導通電阻為40Ω的SW模型語句定義。這些開關由一個持續時間為 312ns 和周期為 1μs 的脈沖電壓源驅動,以模擬 LTC2378-20 SAR ADC 在 1Msps 時的采集時間。為了使采樣電容為下一個采集階段做好準備,使用理想化行為逆變器(A1)來打開對電容放電的第二組開關(S3和S4)。

圖3.SAR ADC模擬輸入等效電路仿真原理圖。

放大器和ADC之間的RC濾波器網絡有多種用途。首先,濾波器網絡減少進入ADC的寬帶噪聲量。其次,電容用作電荷儲存器,吸收來自ADC內部采樣電容的電荷反沖。在每個轉換周期之后,放電的采樣電容(45pF)重新連接到放大器電路。通過在ADC輸入端放置一個大得多的儲能電容,可以減少這些采樣電容引起的電壓偏移。然而,在寬帶噪聲和建立時間性能之間需要權衡取舍。當采樣電容連接到放大器電路(采集時間)時,RC網絡應完全建立到ADC的分辨率范圍內。在濾波器網絡中使用過多的儲能電容會使建立時間超出可接受的限值。

審核編輯:郭婷

-

放大器

+關注

關注

143文章

13589瀏覽量

213484 -

濾波器

+關注

關注

161文章

7817瀏覽量

178128 -

adc

+關注

關注

98文章

6498瀏覽量

544641

發布評論請先 登錄

相關推薦

SAR與ADC不同輸入類型

不同的SAR ADC模擬輸入架構研究

SAR ADC模擬輸入架構

使用sar adc時的模擬路由錯誤該怎么辦?

如何使用LTspice模擬 SAR ADC 模擬輸入?

探索不同的SAR ADC 模擬輸入架構

18 位、2.5Msps、無延遲 SAR ADC可實現 99.8dB SNR 及靈活的模擬輸入范圍

SAR ADC的采樣過程和模擬輸入結構

LTspice:仿真SAR ADC模擬輸入

LTspice:仿真SAR ADC模擬輸入

評論