鍺硅(SiGe)外延(p-MOS源漏)

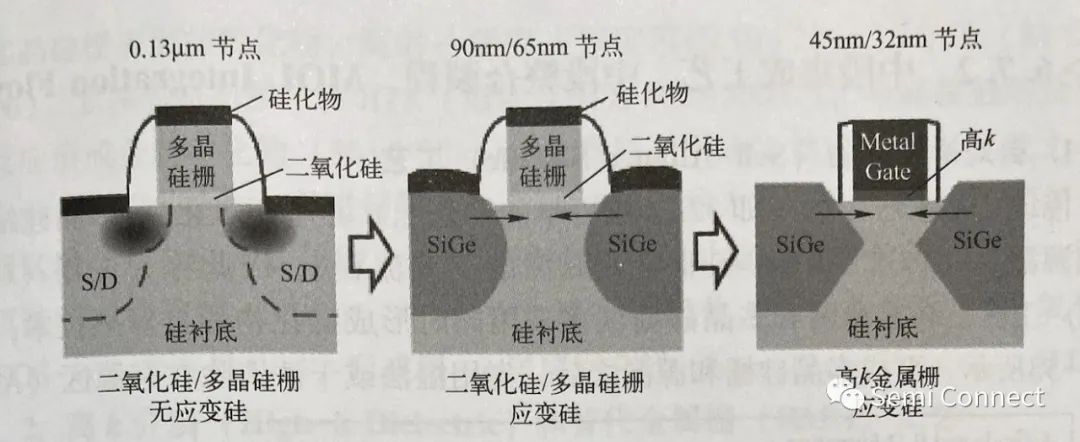

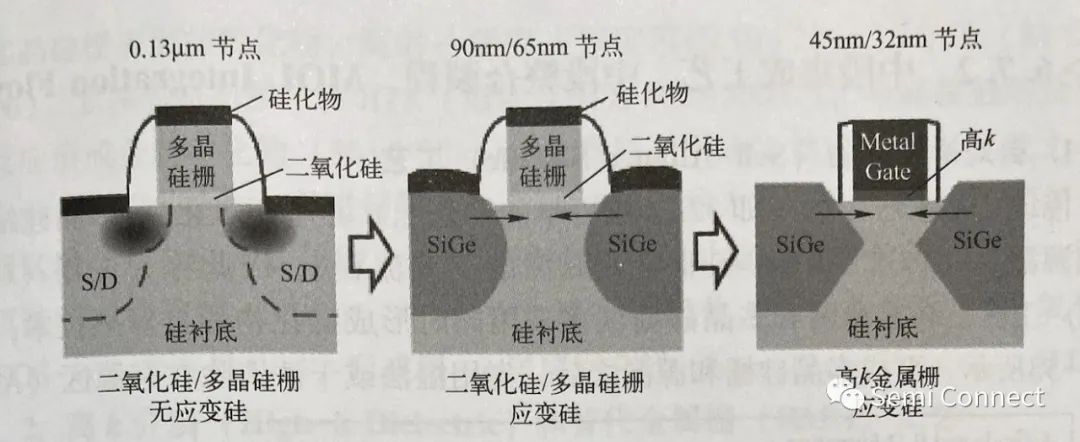

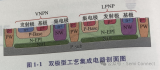

自 32 nm節(jié)點(diǎn)以來(lái),CMOS 器件結(jié)構(gòu)已從多晶硅柵(如硅氧化/多晶硅結(jié)構(gòu))和非應(yīng)變?cè)绰┙Y(jié)構(gòu)演變到利用高k柵介質(zhì)/金屬柵 (high-k/ Metal-Gate, HKMG)和應(yīng)變硅源漏,如圖所示。

其制造工藝流程如下:首先形成補(bǔ)償側(cè)墻(Offset Spacer),經(jīng)n+/p+輕摻雜源漏后,選擇性地進(jìn)行圖形化,在p型源漏區(qū)先進(jìn)行干法刻蝕,使其凹陷適當(dāng)?shù)纳疃?30~100nm);然后采用濕法各向異性刻蝕形成“鉆石”形腔(Diamond Cavity,又稱“∑”形狀);接著外延鍺硅(SiGe)形成p-MOS 的源漏,p型摻雜可由原位硼摻雜或硼離子注入和快速熱退火(RTA) 來(lái)形成。p型源漏的鉆石形鍺硅面向溝道的鄰近尖點(diǎn)(DiamondTip),可有效地增強(qiáng)沿溝道方向的壓應(yīng)力,因此也增強(qiáng)了溝道空穴遷移率。

審核編輯 :李倩

聲明:本文內(nèi)容及配圖由入駐作者撰寫(xiě)或者入駐合作網(wǎng)站授權(quán)轉(zhuǎn)載。文章觀點(diǎn)僅代表作者本人,不代表電子發(fā)燒友網(wǎng)立場(chǎng)。文章及其配圖僅供工程師學(xué)習(xí)之用,如有內(nèi)容侵權(quán)或者其他違規(guī)問(wèn)題,請(qǐng)聯(lián)系本站處理。

舉報(bào)投訴

原文標(biāo)題:前段集成工藝(FEOL)- 6

文章出處:【微信號(hào):Semi Connect,微信公眾號(hào):Semi Connect】歡迎添加關(guān)注!文章轉(zhuǎn)載請(qǐng)注明出處。

相關(guān)推薦

芯片制造可分為前段(FEOL)晶體管制造和后段(BEOL)金屬互連制造。后段工藝是制備導(dǎo)線將前段制造出的各個(gè)元器件串連起來(lái)連接各晶體管,并分配時(shí)鐘和其他信號(hào),也為各種電子系統(tǒng)組件提供電

![的頭像]() 發(fā)表于

發(fā)表于 12-04 14:10

?1134次閱讀

共讀好書(shū)歡迎掃碼添加小編微信掃碼加入知識(shí)星球,領(lǐng)取公眾號(hào)資料

原文標(biāo)題:集成電路封裝基板工藝詳解(68

![的頭像]() 發(fā)表于

發(fā)表于 11-01 11:08

?287次閱讀

共讀好書(shū)歡迎掃碼添加小編微信掃碼加入知識(shí)星球,領(lǐng)取公眾號(hào)資料

原文標(biāo)題:集成電路封裝基板工藝詳解(68

![的頭像]() 發(fā)表于

發(fā)表于 11-01 11:08

?211次閱讀

隨著信息技術(shù)的飛速發(fā)展,芯片作為現(xiàn)代電子設(shè)備的核心部件,其重要性日益凸顯。而芯片封裝工藝集成工程師作為芯片制造過(guò)程中的關(guān)鍵角色,需要掌握一系列復(fù)雜的課程知識(shí),以確保芯片的性能、穩(wěn)定性和可靠性。本文將從多個(gè)方面詳細(xì)闡述芯片封裝工藝

![的頭像]() 發(fā)表于

發(fā)表于 10-24 10:09

?337次閱讀

近日,晶合集成在新工藝研發(fā)領(lǐng)域取得了重要突破。在2024年第三季度,晶合集成成功通過(guò)了28納米邏輯芯片的功能性驗(yàn)證,并順利點(diǎn)亮了TV,標(biāo)志著其28納米制程技術(shù)又邁出了堅(jiān)實(shí)的一步。

![的頭像]() 發(fā)表于

發(fā)表于 10-10 17:10

?541次閱讀

集成電路(IC)作為現(xiàn)代電子技術(shù)的核心,其制造工藝的復(fù)雜性和先進(jìn)性直接決定了電子產(chǎn)品的性能和質(zhì)量。對(duì)于有志于進(jìn)入集成電路行業(yè)的學(xué)習(xí)者來(lái)說(shuō),掌握一系列基礎(chǔ)知識(shí)是至關(guān)重要的。本文將從半導(dǎo)體物理與器件

![的頭像]() 發(fā)表于

發(fā)表于 09-20 13:46

?754次閱讀

在硅基集成電路(IC)制造業(yè)的精密舞臺(tái)上,WIP(Wafer In Process)扮演著舉足輕重的角色。它指代那些正處于復(fù)雜制造工藝流程之中,已經(jīng)歷了部分處理階段但尚未完成全部生產(chǎn)環(huán)節(jié)的晶圓。這些晶圓如同生產(chǎn)線上的旅行者,穿梭于不同的

![的頭像]() 發(fā)表于

發(fā)表于 08-26 16:15

?1024次閱讀

本章主要介紹了集成電路是如何從雙極型工藝技術(shù)一步一步發(fā)展到CMOS 工藝技術(shù)以及為了適應(yīng)不斷變化的應(yīng)用需求發(fā)展出特色工藝技術(shù)的。

![的頭像]() 發(fā)表于

發(fā)表于 07-17 10:09

?1186次閱讀

近日,SK海力士與臺(tái)積電宣布達(dá)成合作,計(jì)劃量產(chǎn)下一代HBM(高帶寬內(nèi)存)。在這項(xiàng)合作中,臺(tái)積電將主導(dǎo)基礎(chǔ)芯片的前端工藝(FEOL)和后續(xù)布線工藝(BEOL),確保基礎(chǔ)芯片的質(zhì)量與性能。而SK海力士則負(fù)責(zé)晶圓測(cè)試和HBM的堆疊工作

![的頭像]() 發(fā)表于

發(fā)表于 05-20 09:18

?553次閱讀

集成電路(IC)是現(xiàn)代電子設(shè)備中不可或缺的組件,它將成千上萬(wàn)的晶體管、電阻、電容等元件集成在一塊微小的硅片上,實(shí)現(xiàn)了復(fù)雜電路功能的高度集成化。集成電路的制造涉及到多種精密

![的頭像]() 發(fā)表于

發(fā)表于 04-10 13:40

?7405次閱讀

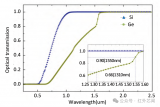

鍺(Ge)探測(cè)器是硅基光電子芯片中實(shí)現(xiàn)光電信號(hào)轉(zhuǎn)化的核心器件。在硅基光電子芯片工藝中實(shí)現(xiàn)異質(zhì)單片集成高性能Ge探測(cè)器工藝,是光模塊等硅基光電子產(chǎn)品實(shí)現(xiàn)小體積、低成本和易制造的優(yōu)先選擇。

![的頭像]() 發(fā)表于

發(fā)表于 04-07 09:16

?1037次閱讀

此節(jié)以半導(dǎo)體的代表,CMOS-半導(dǎo)體為例,對(duì)前段制程FEOL進(jìn)行詳細(xì)說(shuō)明。此說(shuō)明將依照FEOL主要制程的剖面構(gòu)造模型,說(shuō)明非常詳細(xì),但一開(kāi)始先掌握大概即可。

![的頭像]() 發(fā)表于

發(fā)表于 04-03 11:40

?1229次閱讀

前段制程包括:形成絕緣層、導(dǎo)體層、半導(dǎo)體層等的“成膜”;以及在薄膜表面涂布光阻(感光性樹(shù)脂),并利用相片黃光微影技術(shù)長(zhǎng)出圖案的“黃光微影”。

![的頭像]() 發(fā)表于

發(fā)表于 04-02 11:16

?5152次閱讀

電子發(fā)燒友網(wǎng)站提供《東芝BiCD工藝集成電路硅單片TB67H450AFNG數(shù)據(jù)手冊(cè).pdf》資料免費(fèi)下載

發(fā)表于 03-20 11:23

?1次下載

近日,上海發(fā)布了《2023年上海科技進(jìn)步報(bào)告》,來(lái)自上海工研院的MEMS標(biāo)準(zhǔn)工藝模塊及90納米硅光集成工藝2項(xiàng)國(guó)際先進(jìn)水平技術(shù)成果入選。

![的頭像]() 發(fā)表于

發(fā)表于 02-22 09:42

?929次閱讀

前段集成工藝(FEOL)

前段集成工藝(FEOL)

評(píng)論