感謝《半導體行業觀察》對新思科技的關注

低功耗一直是便攜式電子設備的關鍵要求,但近年來,在人工智能、5G、大數據中心、汽車等應用快速發展的推動下,對低功耗的需求已經擴散到更多的終端產品中。而且隨著芯片中晶體管的集成度越來越高,散熱成為行業的一大挑戰,因此低功耗設計顯得尤為重要。這也給廣大開發者提出了不小的挑戰。

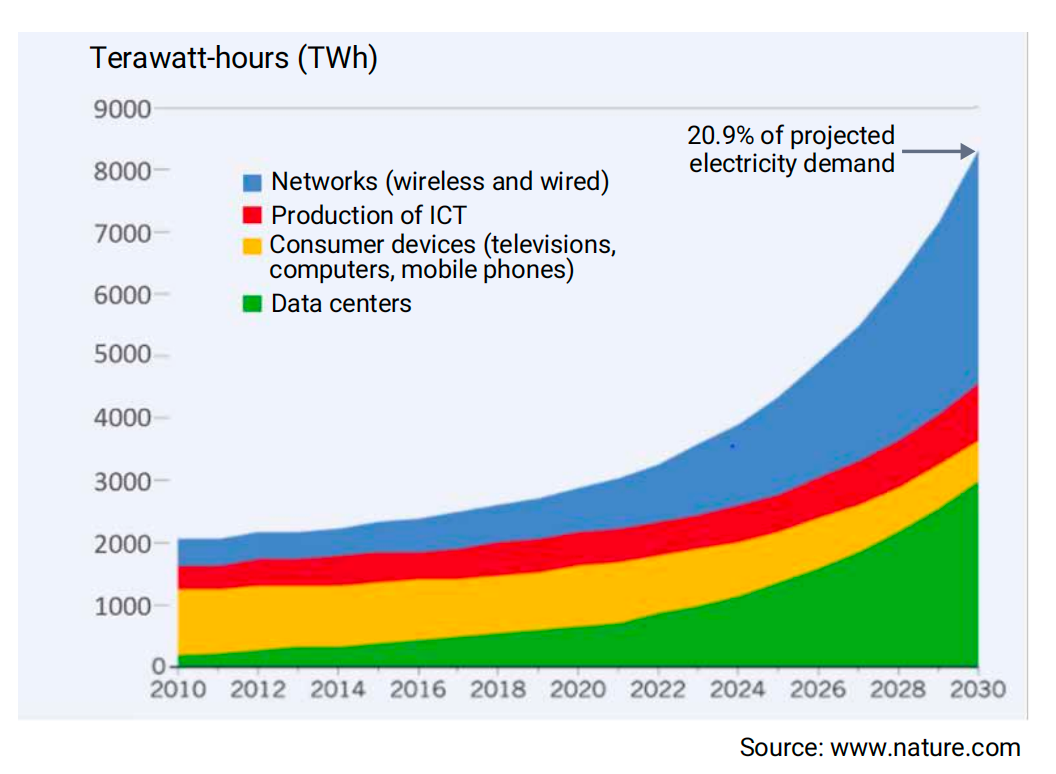

低功耗是芯片的重要考量指標 隨著電子設備的大規模增加,電子產品所消耗的電力也在增長。圖1顯示了全球信息和通信技術(ICT)所消耗的電力增長情況,按照nature的統計,預計到2030年,僅ICT所消耗的電力占比將達到20%以上。 因此,芯片開發者和制造商都爭取在保證芯片性能的情況下,盡可能做到低碳、節能和環保。 ▲圖1:信息通信技術應用的電力需求增長

▲圖1:信息通信技術應用的電力需求增長

低功耗正成為芯片很重要的一個衡量指標。對于智能手機、平板電腦、筆記本電腦和可穿戴設備等小型電子產品來說,一方面由于其使用電池,控制功耗可以獲得更長的使用時間,一方它們的SoC大多采用先進工藝、設計比較復雜,本身就面臨散熱難題,降低功耗也能進一步緩解這方面的挑戰。此外,像臺式機、服務器這樣的大型系統而言,雖然可以通過使用先進封裝技術、大型散熱器、風扇甚至是液冷技術等解決散熱問題,但這些會帶來成本的大幅增加,同時出于對全球氣候變化的擔憂,也要求開發者們對產品設計和電源能效進行更合理的權衡。

低功耗貫穿芯片設計全流程

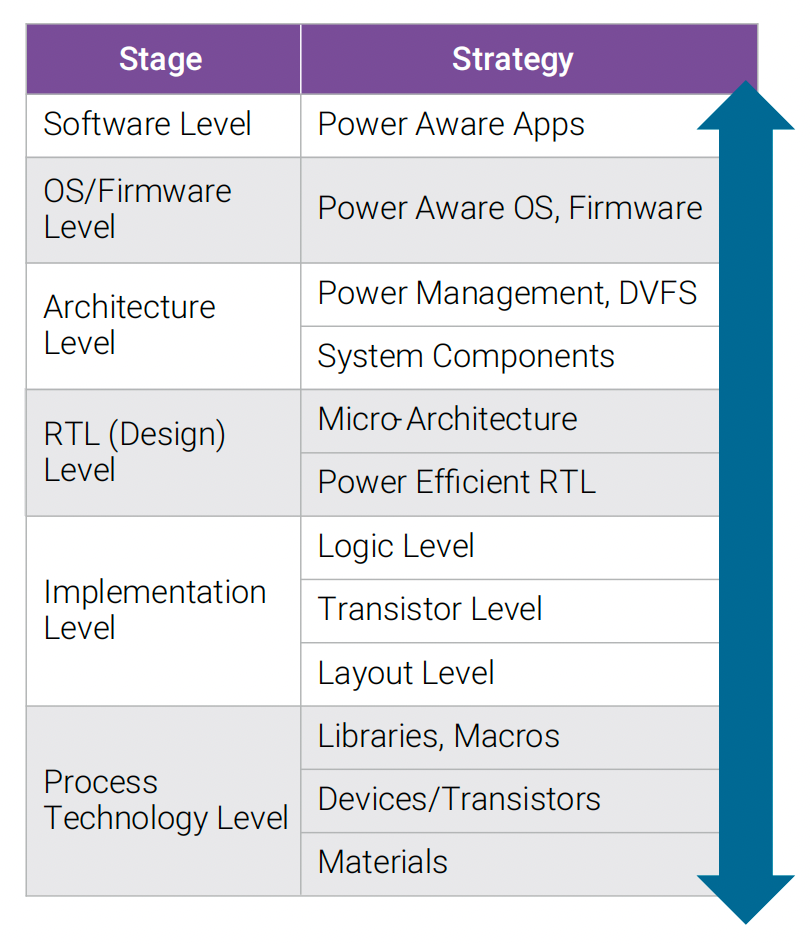

為了達到最佳效果,在SoC設計的每個階段都必須考慮能源效率問題。如圖2所示,多年來,行業從業者開發了各種各樣的技術來管理和降低功耗。

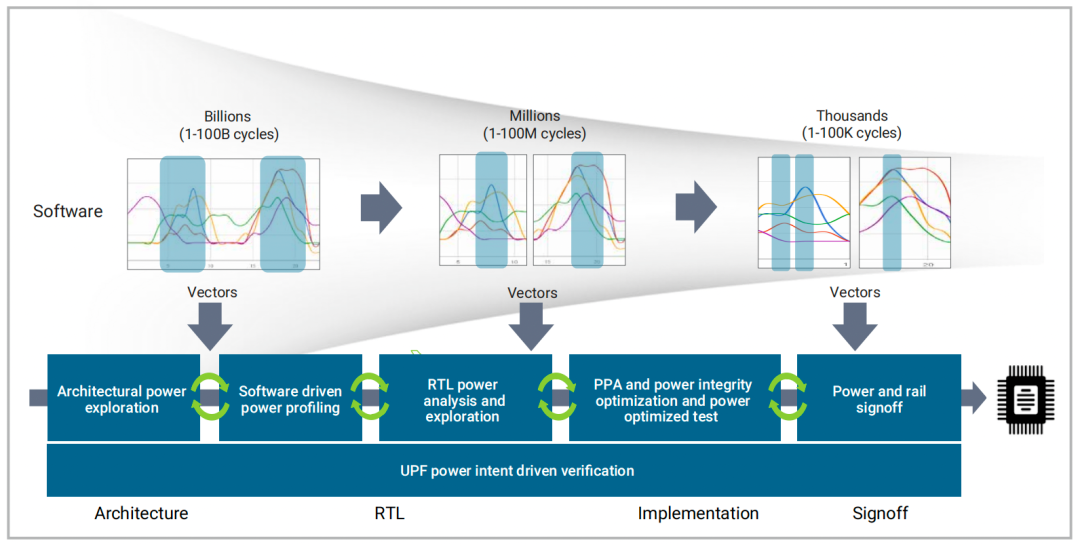

從最底部的物理層開始看起,首先是材料,常用的硅擁有較高的導熱性,除此之外,砷化鎵(GaAs)也被廣泛應用于某些高性能產品領域。 在基礎材料之上,晶體管和其他器件的結構也對能源效率有很大的影響。在芯片開發的早期階段,開發者們就通過選擇與設計目標最匹配的晶體管來權衡功率性能區域(PPA),鰭場效應晶體管(FinFET)器件就是一個很典型的例子。1990年代,半導體產業面臨25納米的制程瓶頸,當時市場有不少聲音認為摩爾定律即將終結, FinFET 晶體管技術的出現讓半導體產業突破瓶頸,逐步發展到現在的7納米、5納米制程技術。 但要知道的一點是,大部分SoC設計不是在晶體管級別上進行的,而是在寄存器傳輸級別(RTL)上進行的,或者是使用通用功能的單元庫合成的更高級別的代碼。這其中包含許多“低功耗”單元庫,開發者可以利用邏輯合成工具快速測試多種單元庫的組合,以滿足PPA目標。功耗會影響芯片的電源完整性和熱特性,因此必須在物理設計階段就解決這些問題,并在signoff期間進行確認。 在微架構的定義過程中也必須考慮到功耗的問題。常用做法是關閉當前SoC中未被激活的部分,將其置于待機狀態,或使用動態電壓和頻率縮放(DVFS)來實時控制操作。SoC架構師必須定義電源控制結構并提供hooks,以便它們可以由運行在終端系統上的軟件進行操作。 軟件是解決方案的最后一部分。雖然硬件層面可以完全實現電源管理要求,但對于大多數SoC來說,大部分的工作都有電源感知固件、操作系統(OS)和應用程序(apps)來控制。例如,操作系統知道所有正在運行或計劃運行的應用程序和任務,因此可以在不需要最高性能的地方做出減少或停止芯片運行的決定。在生產環節用于測試裸片和芯片的應用程序也需要注意功耗以免引起過熱。 圖3中是低功耗SoC設計的整個流程。

看起來要打造一個低功耗設計所需要非常多工作,但是統一功率格式(UPF)標準的引入,讓整個設計流程變得更加容易。UPF規定了SoC電源控制網絡的許多方面,包括:

-

電源網絡和電源開關

-

功率/電壓域

-

這些域之間的電平移位器和隔離單元

-

功率狀態和這些狀態之間的轉換

-

當芯片中的電源部分關閉時,內存保留

UPF標準用于描述低功耗要求,基于TCL語言編寫。目前,最新版的UPF為UPF3.0 1801-2018。設計工具可以讀取該文件,并通過邏輯綜合、放置和路由來指導設計實現。在虛擬模型中,架構工具可以使用UPF反映電源管理的需求,從而幫忙開發者在宏觀層面進行權衡。許多驗證工具也會將功耗納入考慮之中。

新思科技的

端到端低功耗解決方案

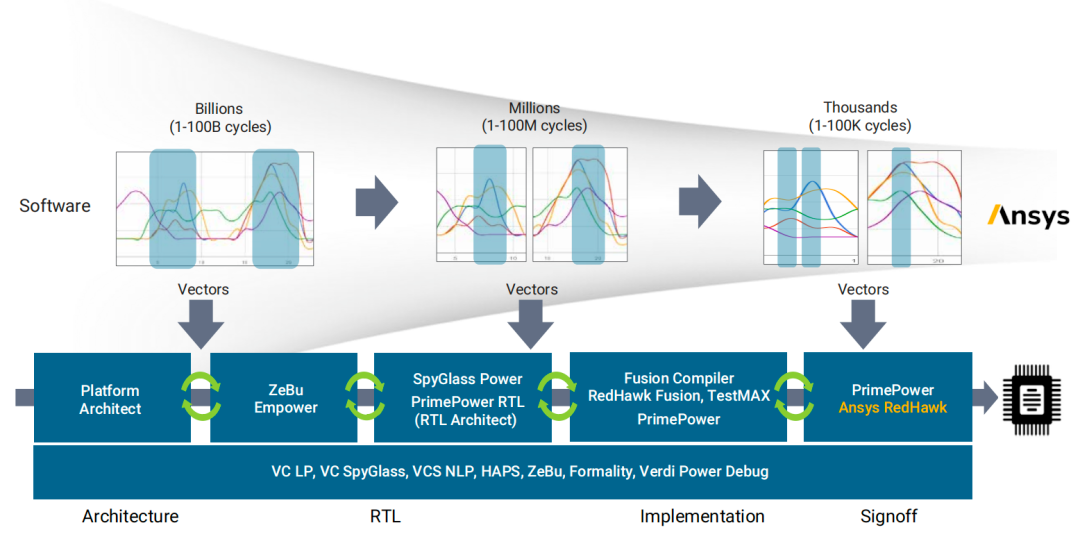

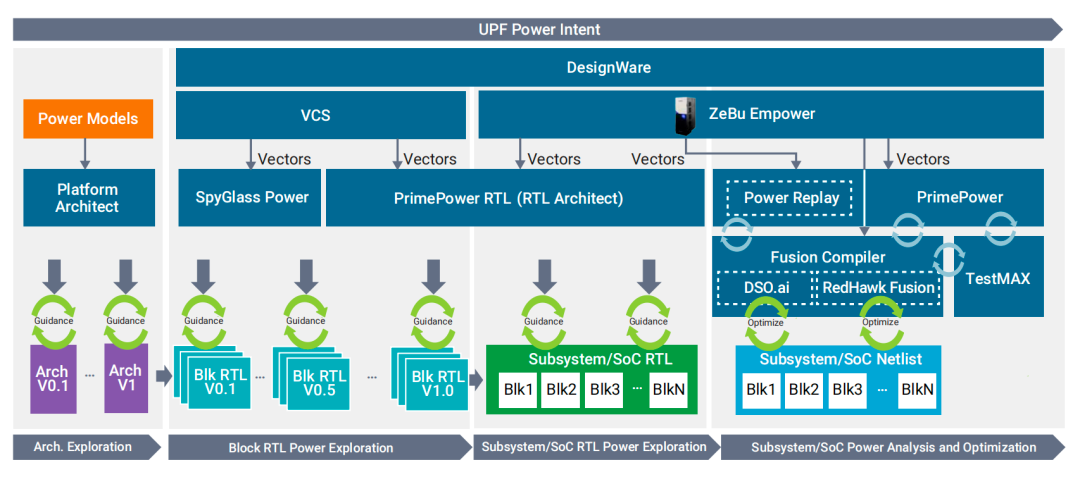

在低功耗設計方面,新思科技提供以軟件驅動的電源驗證、探索、分析和優化的低功耗解決方案,其產品覆蓋了低功耗設計的所有流程,包括Platform Architect、ZeBuEmpower、SpyGlass Power、PrimePower RTL、Fusion Compile、Fusion of PrimePower and RedHawk signoff engines、TestMAX、PrimePower和Ansys RedHawk等,這些產品構成了非常完整、有效的解決方案。

▲圖4:新思科技的低功耗解決方案

▲圖4:新思科技的低功耗解決方案

新思科技的開發流程基于實際的軟件工作負載來權衡電源性能,并且在設計早期就準確地進行功耗分析,還可以幫助開發者更快實現PPA目標。圖5深入剖析了新思科技的設計流程細節,顯示了其中各個組件/產品如何應用于不同的設計階段。

▲圖5:軟件驅動功耗的探索、分析和優化

▲圖5:軟件驅動功耗的探索、分析和優化

在架構階段,Platform Architect可以使用抽象模型來探索合適的系統性能和功耗。在RTL模塊開發的早期階段,SpyGlass Power與VCS模擬器生成的矢量一起用于功耗分析。隨著RTL模塊接近完善,PrimePower RTL提供了基于嵌入式RTL Architect物理和時間感知預測技術以及signoff PrimePower engine的更準確的分析。當SoC或子系統進入仿真階段,ZeBu Empower將用于分析軟件工作負載,以識別高活躍的窗口(例如峰值功率和高平均功率區域),然后在PrimePower RTL中進行更詳細的分析。

隨著設計進入實現階段,活動窗口的進一步細化將驅動Fusion Compiler中的實現。在人工智能引擎DSO的輔助下,RTL到GDSII流程可以快速提供最佳的PPA結果。ZeBu Empower的活動窗口也推動了PrimePower signoff流程,它的Power Replay功能可以在門級網表上重新利用由VCS RTL仿真產生的向量。PrimePower Golden power signoff包括用于( Glitch)故障分析和調試的關鍵技術,用于計時精度的延遲轉移,以及用于高級過程節點的建模。最后,TestMax可以在制造測試過程中用于功耗分析。

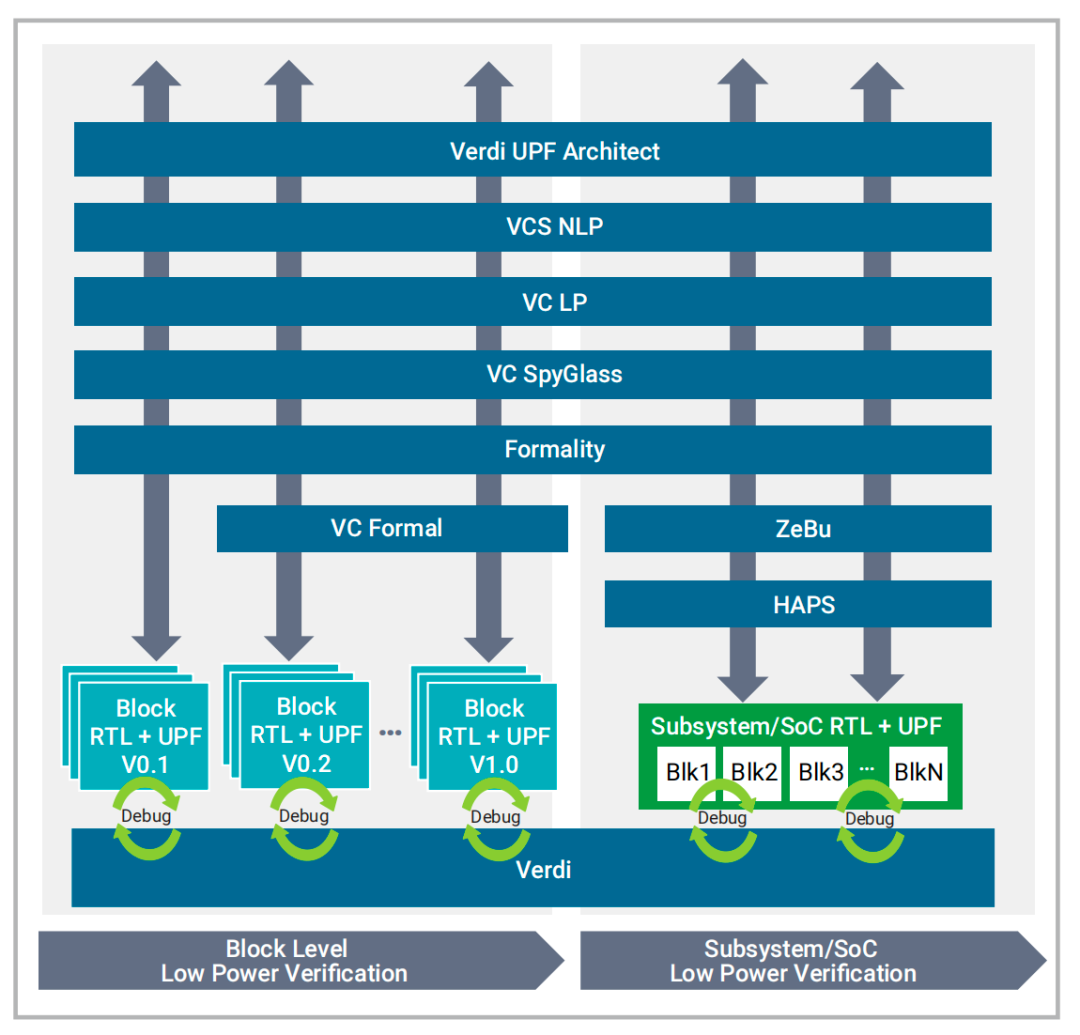

除了自定義RTL部分外,每個SoC都會使用商業IP。而在這方面,新思科技提供廣泛的低功耗IP產品組合,用于處理器、接口、傳感器、模擬/混合信號(AMS)、存儲器和邏輯庫。這些都帶有預定義的UPF描述,以補充開發者提供的文件。圖6詳細展示了新思科技的低功耗驗證工具。

這些驗證可以在從RTL到最終布局網表的任何設計階段開始進行,也可以在RTL-to-GDSII流程的各個階段直接從Fusion Compiler中調用這些檢查,以確保在芯片實現的過程中達到低功耗要求。VC SpyGlassRTL靜態signoff平臺還可以讀取UPF,以便檢查時鐘域交叉(CDC)和重置域交叉(RDC)實例是有低功耗要求的。由Formality執行的邏輯等價性檢查(LEC)和由VC Formal執行的分析驗證也是如此。ZeBu仿真系統和HAPS原型解決方案都考慮了UPF。所有這些工具和技術都將Verdi作為統一的調試平臺共享,并提供許多支持功率的調試特性。最終在功能驗證的所有階段,對低功耗要求規范都有統一的要求。

結論

許多SoC應用需要最小的功耗來延長電池壽命、滿足市場需求。但是,PPA的總體目標不能僅僅集中在功耗上,更應該有一個端到端的設計流程來提高電源效率。新思科技的全流程低功耗解決方案將為整個芯片行業在進行低功耗全過程設計中提供極大的幫助。

原文標題:如何從0到1設計一顆低功耗芯片?

文章出處:【微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

-

新思科技

+關注

關注

5文章

798瀏覽量

50349

原文標題:如何從0到1設計一顆低功耗芯片?

文章出處:【微信號:Synopsys_CN,微信公眾號:新思科技】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

用一顆5G的204B接口DA芯片,DA芯片的輸入時鐘大小和輸入數據的速率是怎么樣的關系?

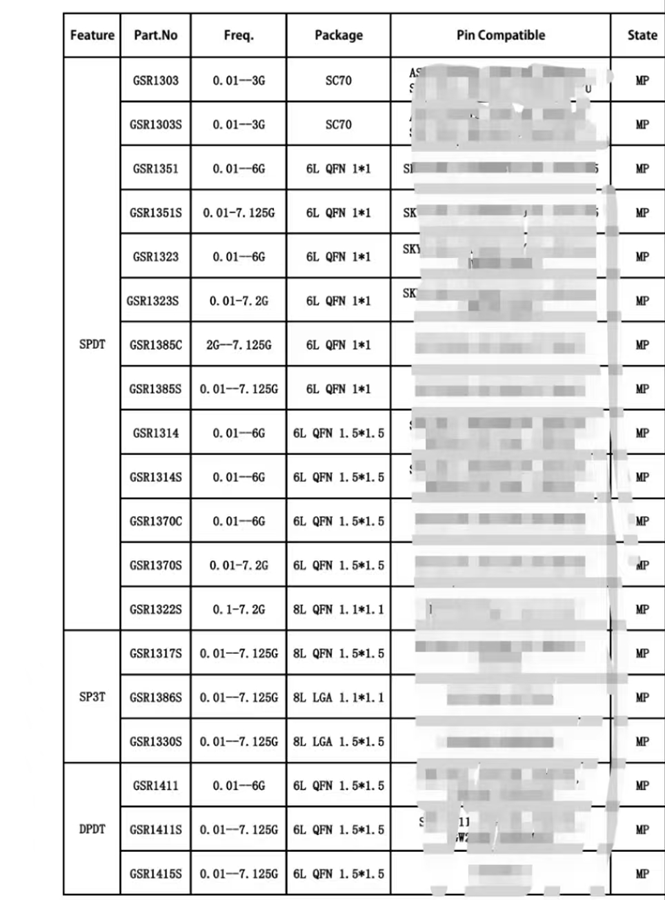

一顆射頻開關的獨白

低功耗SOC芯片的優勢

兩顆TAS5711,一顆作2.0輸出,一顆作PBTL輸出,共用一個I2S_DATA時發現失真增大,為什么?

一款4644芯片低功耗設計思路解析

RA0E1 MCU低功耗演示例程

BK7256 WIFI+BLE音視頻低功耗芯片 ,支持小家電驅屏,ipc、可視門鎖,智能貓眼

一顆改變了世界的芯片

芯嶺技術推出一顆高性價比32位的單片機—XL32F001

如何從0到1設計一顆低功耗芯片?

如何從0到1設計一顆低功耗芯片?

評論