WAYON維安ESD&EOS產品特性簡析,幫你避開保護盲區,方案設計代理商KOYUELEC光與電子提供服務

科技產品永遠不缺天馬行空的想象,設計師們腦洞大開,創造了各種既炫酷又實用的高科技電子產品,讓我們的生活更加便利和有趣。因此,創新是電子行業經久不衰的長期邏輯根基,而這背后支撐創新的引擎的則是半導體產業的頻繁迭代和工藝技術升級。

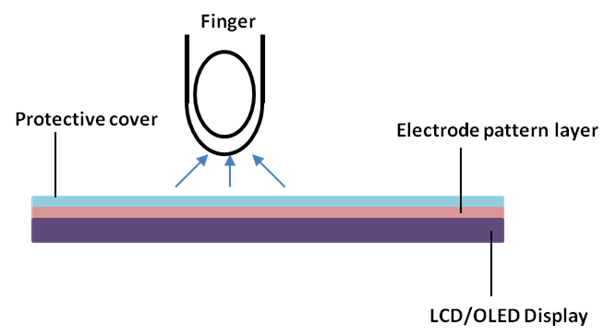

其實,半導體產品技術、工藝的升級就是在同樣的硅片上堆積更多的電子元器件,用以實現產品的體積更小、功耗更小,功能更強大。可以看到,隨著數據速率不斷提升、系統芯片計算能力日益強大、IC微型化以及有限空間中有多種電源要求,組件和系統對ESD也愈加敏感。半導體工藝小型化趨勢亦會導致ESD風險增加,因為較小的電壓會損壞較薄的柵極氧化層。盡管面臨這些挑戰,但好在通過優化ESD保護概念,可以避免或大幅減少ESD造成的損壞或EOS(電氣過應力)。

#器件結構簡述

PART 1.

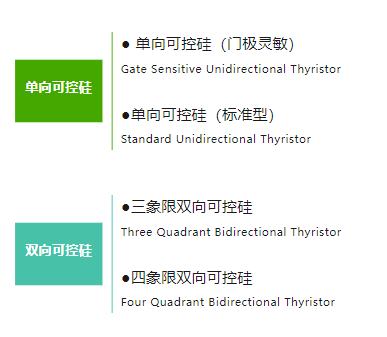

回顧歷史,早在上世紀六十年代,人們就開始注意到ESD在電子零件中產生的破壞性,并在包裝材料中增加導電性材料來達到減弱靜電的生成和積累。時至今天,ESD&EOS保護產品已經形成體系,并呈現多技術、多構架的特點。從產品工藝布局來看,半導體器件有橫向和縱向布局;從技術平臺來看,半導體器件有常規PN結結構、小驟回結構(shallow snapback)和大驟回結構(deep snapback)。

圖1 常規PN結結構

圖2 小驟回結構

圖3 大驟回結構

作為一家深耕保護器件領域20多年的廠商,維安已經完全掌握了上述所有工藝技術平臺。常規結構在同樣的工作電壓條件下擊穿電壓更低,啟動更快;而驟回結構在同樣的工作電壓條件下鉗位電壓更低。

基于不同工藝平臺的產品都有其特定的優勢,如何才能讓客戶根據自己的實際應用選擇一款最適合自己的產品呢?

#理論簡析

PART 2.

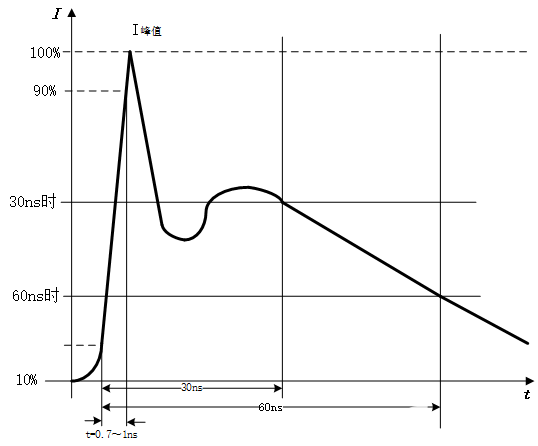

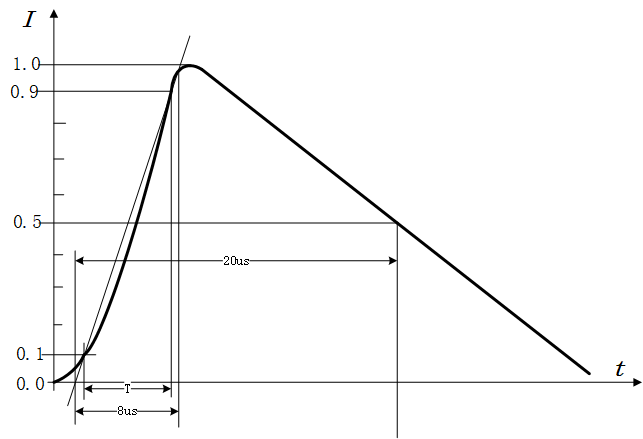

IEC61000-4-2標準波形圖模擬了電路使用環境中遇到的ESD&EOS,從該圖進行分析,似乎第一尖峰和第二尖峰都有損壞后端IC的可能。

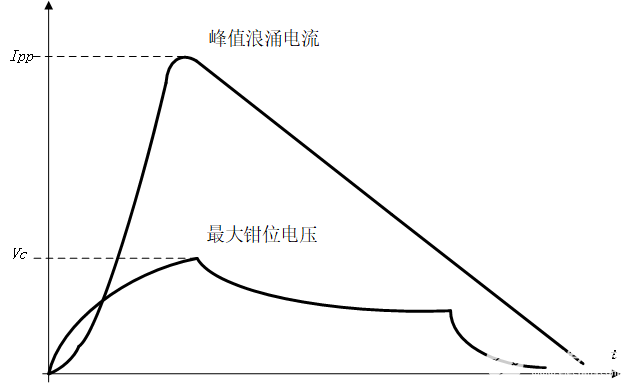

第一尖峰時間短,但是電壓高;第二尖峰電壓低,但是時間長(為了便于理解,這里直接采用標準中的電流波形乘以固定阻抗來類比,實際條件下電壓會更復雜)。而ESD&EOS保護器件可在泄放浪涌電流的同時將電壓鉗位,使得后段IC僅需承受鉗位電壓而不至于損壞。

圖4 IEC61000-4-2電流波形

圖5 IEC61000-4-5電流波形

圖6 EOS保護器件鉗位電壓波形圖

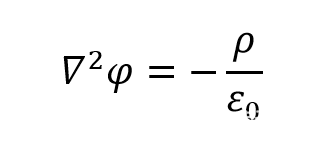

對于集成度越來越高的IC電路,其硅氧化層介質層的絕緣性能是抗ESD&EOS能力的關鍵。首先,用泊松方程來簡單分析一下IC I/O端口介質層的物理擊穿特性。

φ代表電勢(單位為伏特), ρ是電荷體密度(單位為庫侖/立方米),而ε0是真空電容率(單位為法拉/米)。

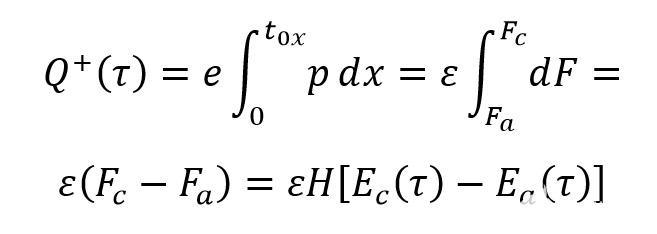

以泊松方程和電流方程得到介質表面俘獲空穴電荷密度隨時間變化的物理方程(注1):

從方程中可以看到,積累在介質表面(以氧化層為例)的電荷除了與時間τ有關系外,還與外加電場E有關系。考慮到IC I/O會受到外界的電壓是非恒定的,時間單位可能是ns、us甚至是ms,所以電場E也是非恒定的。取HBM ESD脈沖條件下的氧化層俘獲空穴密度,經過推導和計算得出:

當氧化層俘獲空穴密度達到臨界值時介質層發生擊穿。從上式簡單分析可知,發生擊穿的臨界值與所加電場強度、氧化層厚度tox和時間均有關系。

結束理論分析,我們得出,IC I/O端口在遭受外界能量時,有諸多不確定因素導致其損壞擊穿。但是研發工程師在進行實際設計的時候,很難進行理論計算,也幾乎沒有芯片供應商會在IC規格書中詳細注明其浪涌耐受能力和芯片制程等信息。

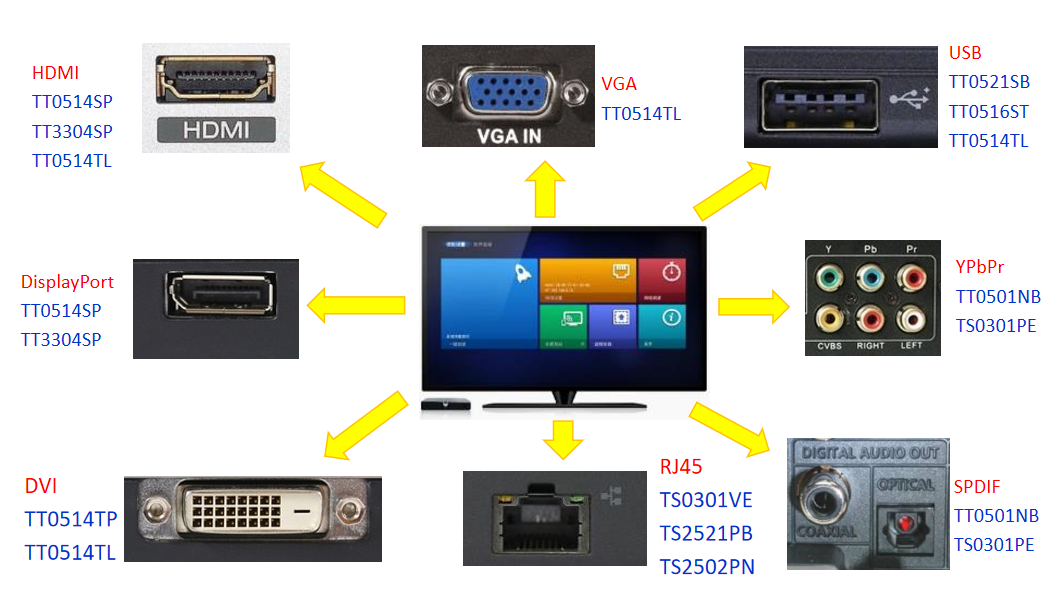

從通信端口的發展來看,最早出現的低速通信線電壓幅值都比較高,端口耐壓也相對較高;從保護的角度來看,端口的高耐壓可以容忍較高的鉗位電壓;從通信速率看,低的通信速率可以接受的較大寄生電容。

綜合上述兩點,保護器件的鉗位電壓在一定范圍內數值高低對保護效果影響不是很大,有很充裕的可選擇性。隨著通信速率的提高,信號線幅值和端口耐壓在不斷降低,對保護器件提出了新的挑戰,一方面要求相同測試條件下的鉗位電壓要更低,還要做到超低的寄生電容,傳統結構的器件已經不再滿足客戶的需求。

如HDMI端口接口芯片的耐壓低,且不同廠家的耐壓值也不同,要保證都測試通過,就要求保護器件兼容最低耐壓,在工程應用中也存在著走線過長、接地不穩定等引起的μs級別甚至ms級別的高能量破壞性波形引入,驟回結構應用而生。

驟回結構可以做到低電容、高耐壓且鉗位電壓非常低,超低電容在高速通信中不會對信號有較大的影響,高耐壓可以避免誤動作,鉗位電壓低可以有效保護在ESD打擊下被保護器件不需要耐受過高的電壓。從客戶角度出發可以相對完美地解決低電容、低鉗位電壓的應用需求。

維安通過在實際應用和方案整改過程不斷的歸納,總結出如下應用要點:

常規結構

幾乎適用于所有的端口保護,具體參數與被保護的端口電特性相關聯。但是對于一些耐壓差的器件,可能會有測試失敗的情況。

小驟回結構

適用于信號端口和部分較差工藝制程的電源IC接口。較常規結構相同測試條件下具有更低的鉗位電壓。選型需要注意VBO、IH和VH參數,防止浪涌電壓小于VBO時的保護盲區和VH低于電源波動高電壓時出現的閂鎖。

大驟回結構

適用于高工藝制程的高速信號接口,具有超低電容和鉗位電壓,對耐壓敏感型接口具有很好的保護作用,對電流源驅動型端口不建議使用。對于此類器件,關注參數較多,選型須慎重,可能會帶來端口閂鎖或失效。

#具體案例分析

PART 3.

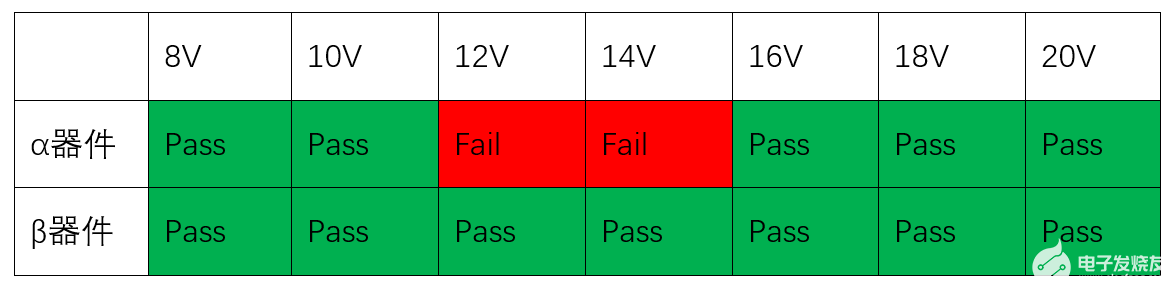

某客戶需要在信號端口進行EOS測試和ESD測試。客戶同時選取了A廠家的小驟回性器件α和維安公司的器件β。

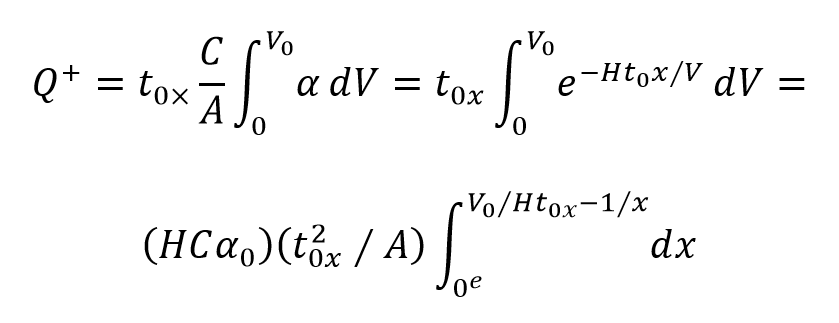

規格書數據如下:

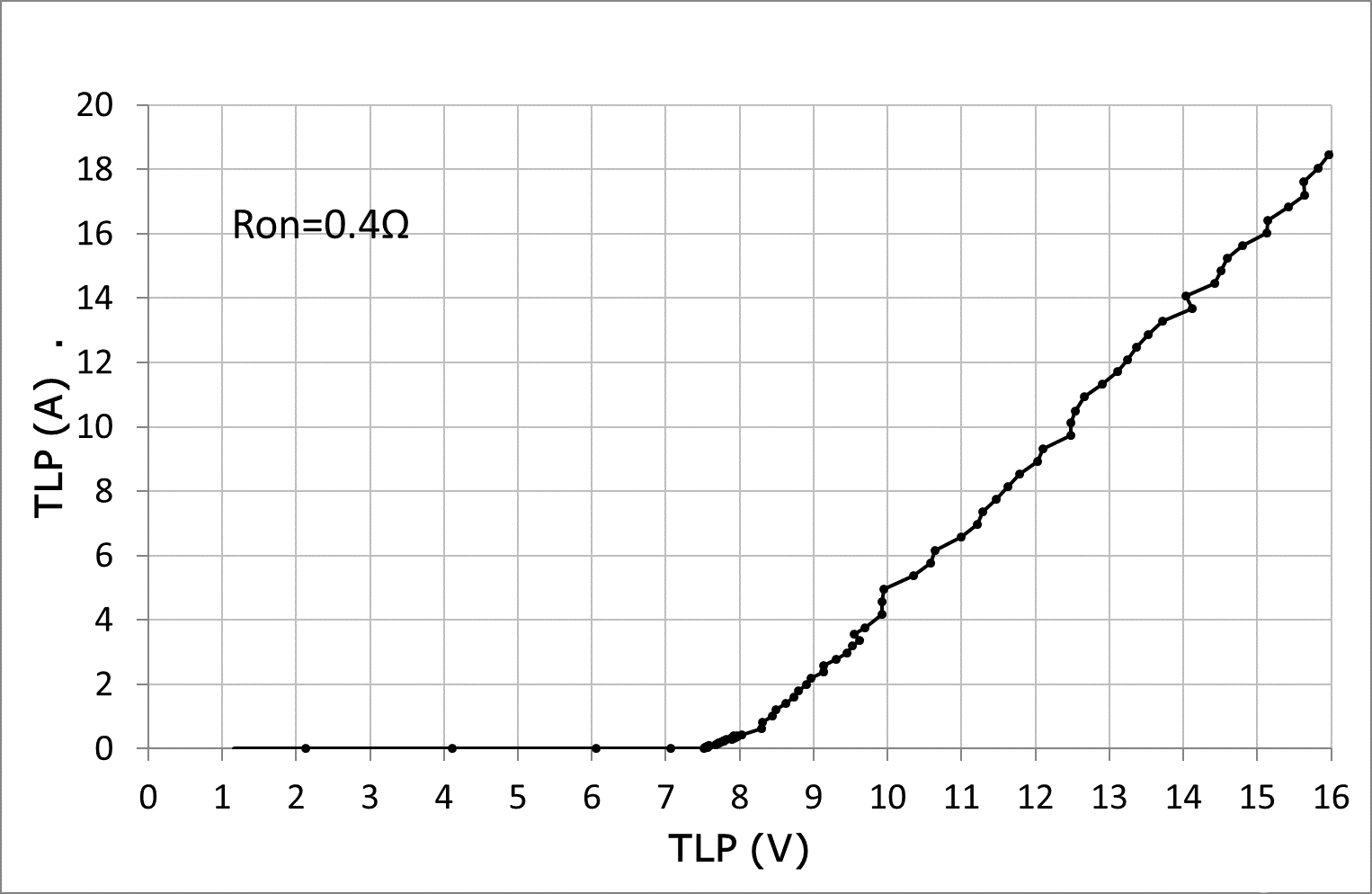

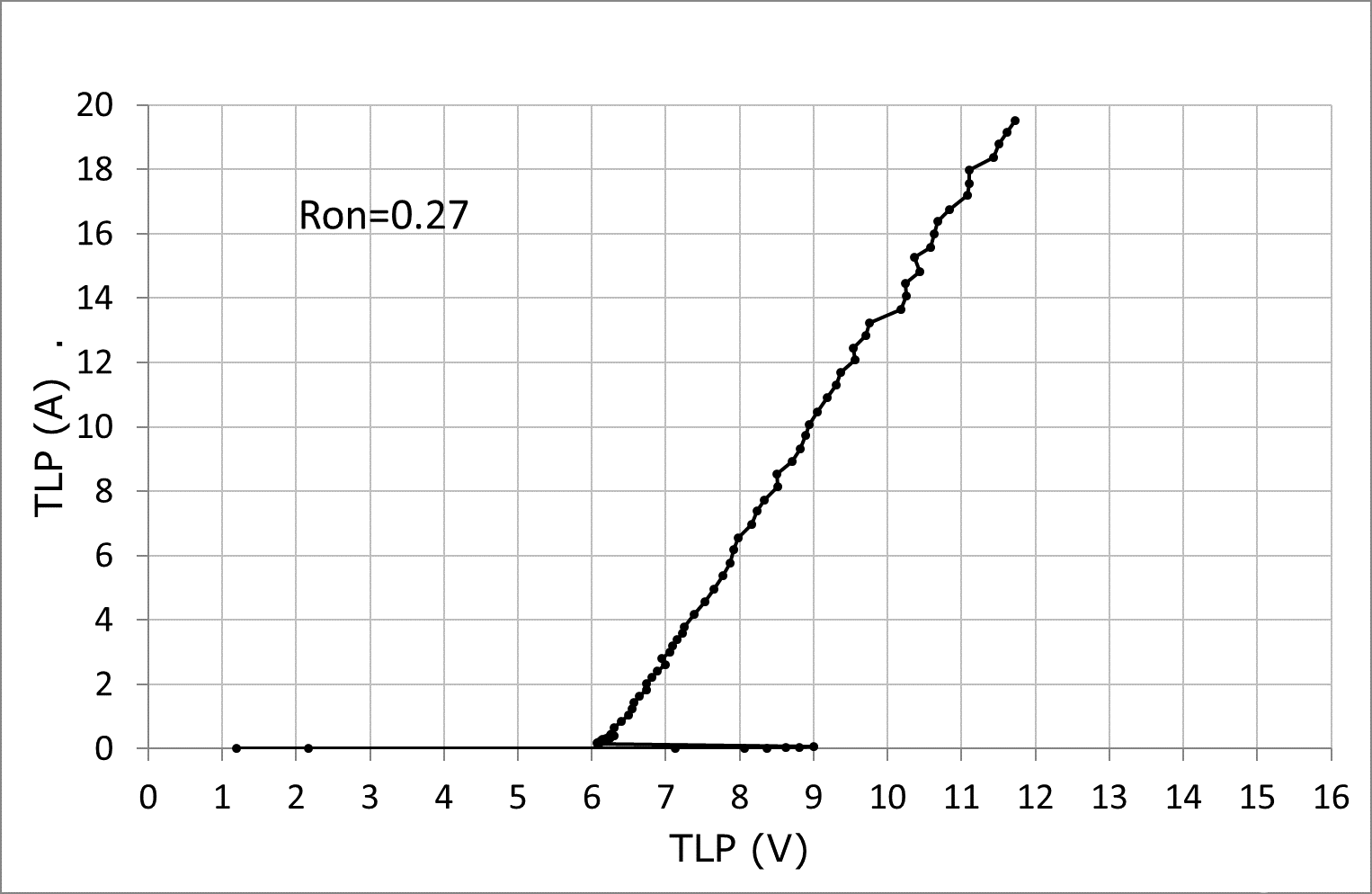

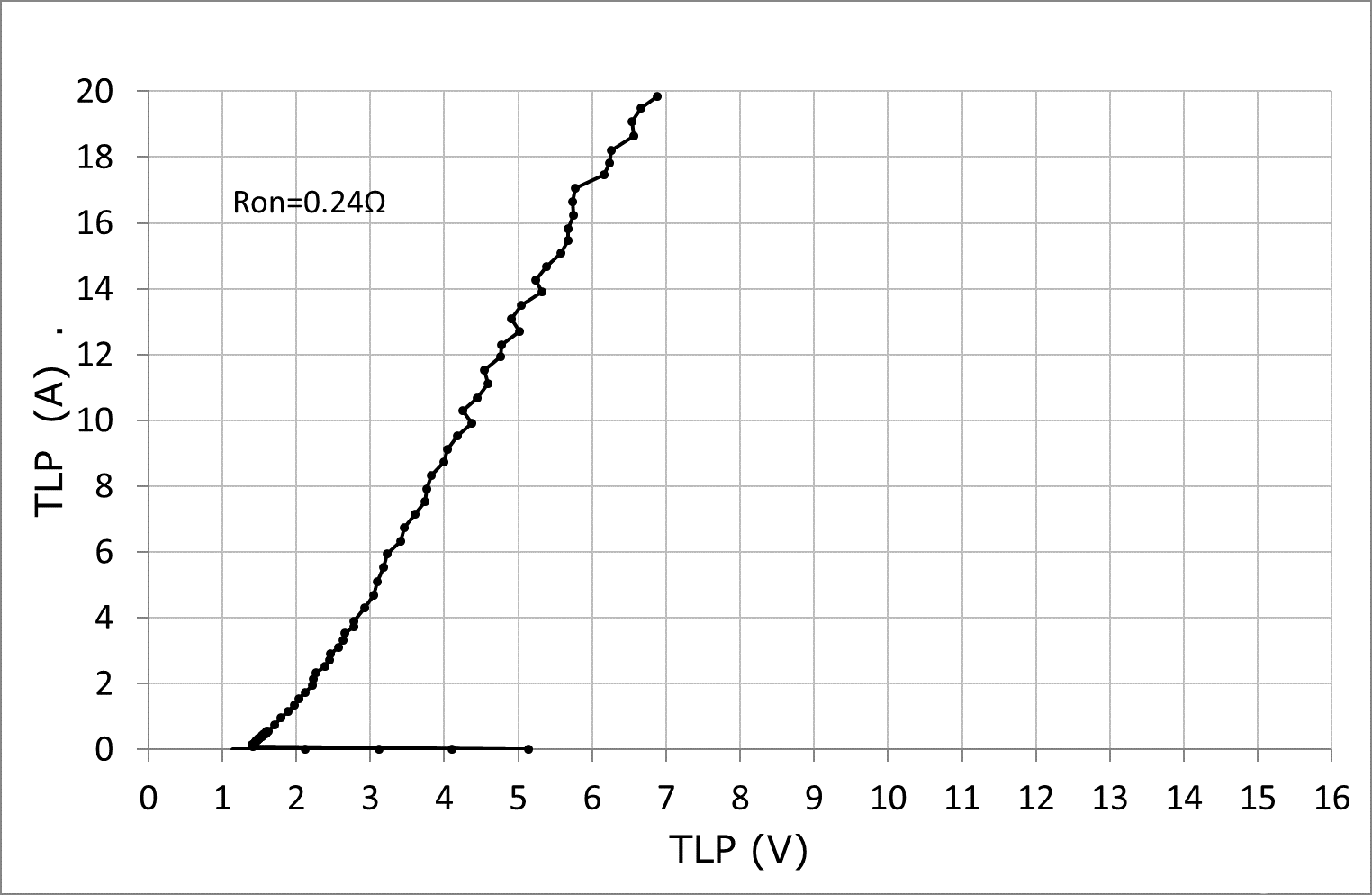

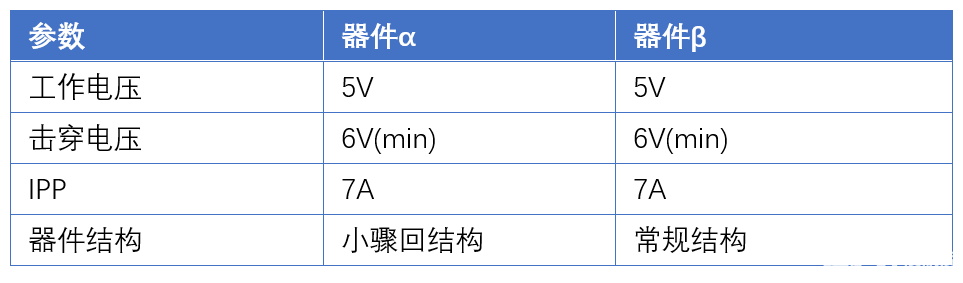

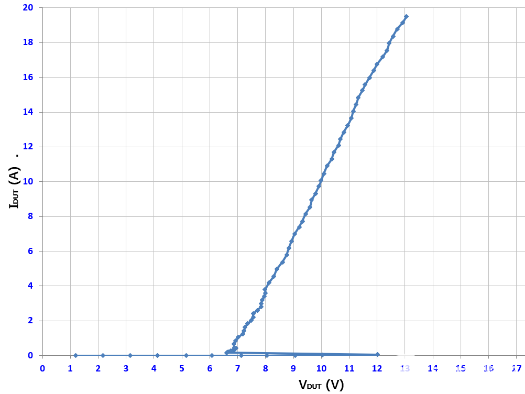

TLP曲線:

圖7 器件α TLP曲線

圖8 器件β TLP曲線

從規格書的部分參數可以得出,兩家產品的性能比較接近,主要是結構不同。測試結果如下:

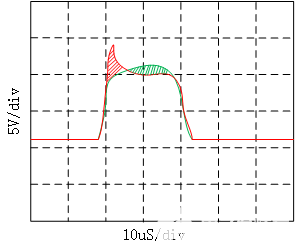

α器件能通過浪涌等級20V,但是在從8V開始的步進測試中,12V和14V卻出現了后端IC失效的結果,當浪涌電壓更高時,器件又起到了保護的作用;而β卻能通過整個浪涌等級的測試。從器件規格書對比來看,α的VC比β要好。通過示波器抓取電壓得到如下波形:

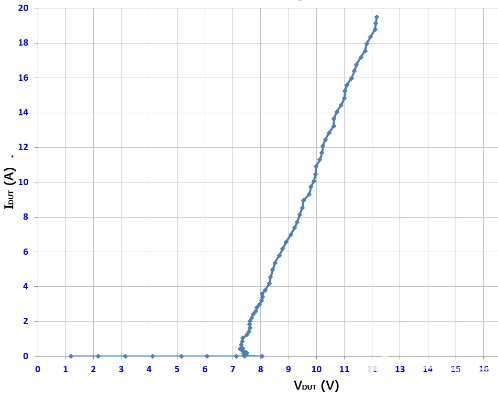

圖9 器件鉗位后的電壓波形(紅色α,綠色β)

從波形可以看出,紅色陰影S紅和綠色陰影S綠部分是兩個器件的能量分布差異;α器件在12V附近的電壓條件下,其由于促使器件trigger的打開時間偏長甚至是未打開,而后端的IC卻無法承受施加的浪涌能量,導致后端IC失效。反觀β器件,只要浪涌電壓超過器件的擊穿電壓,器件就會動作,并迅速鉗位電壓,來達到保護后端IC的目的。

對于有經驗的測試和研發人員來說,當外部施加的EOS浪涌更高時,比如16V以上,這時驟回結構的優點開始凸顯,鉗位效果也會更好。但是作為設備的可靠性保護,其保護范圍是一定要保護等級定義下的全浪涌范圍的保護,而不是有一個保護盲區。

#總結

PART 4.

不同結構的TVS器件在保護后端設備時,呈現的結果并不是確定性的。除了器件本身的參數,研發人員在進行保護方案設計的時候需要清楚自己產品的特點,可能所遭受的環境能量估算和對保護器件的大致選擇,以達到最好的產品保護的目的。

目前業內大部分廠家都是直接給推薦電路,直接告訴設計者答案選擇哪個器件,卻很少對選型過程提供理論推斷、計算。大部分電子工程師針對ESD&EOS選型時,老人憑經驗,新人憑參考,一旦更換廠家或者更換測試條件,就無從下手了。

維安依托優秀的FAE技術團隊和完善的EMC實驗室可進行方案設計、優化和整改,高質量的服務客戶,為客戶的產品提供強有力的保護。

審核編輯:湯梓紅

-

ESD

+關注

關注

49文章

2046瀏覽量

173133 -

半導體

+關注

關注

334文章

27527瀏覽量

219907 -

EOS

+關注

關注

0文章

124瀏覽量

21204

發布評論請先 登錄

相關推薦

DVI接口的ESD保護方案

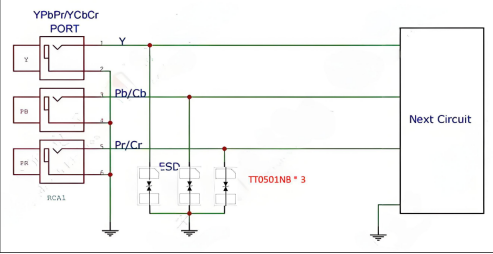

顯示視頻接口的ESD保護方案應用——VGA接口保護方案

顯示視頻接口的ESD保護方案應用——YPbPr接口保護方案

ST NPI 新上架產品【ESDA5WY】Datasheet

esd保護電路為什么加正向的二極管 esd保護是防止什么對電路板的損壞

ESD保護電路POWERclamp原理

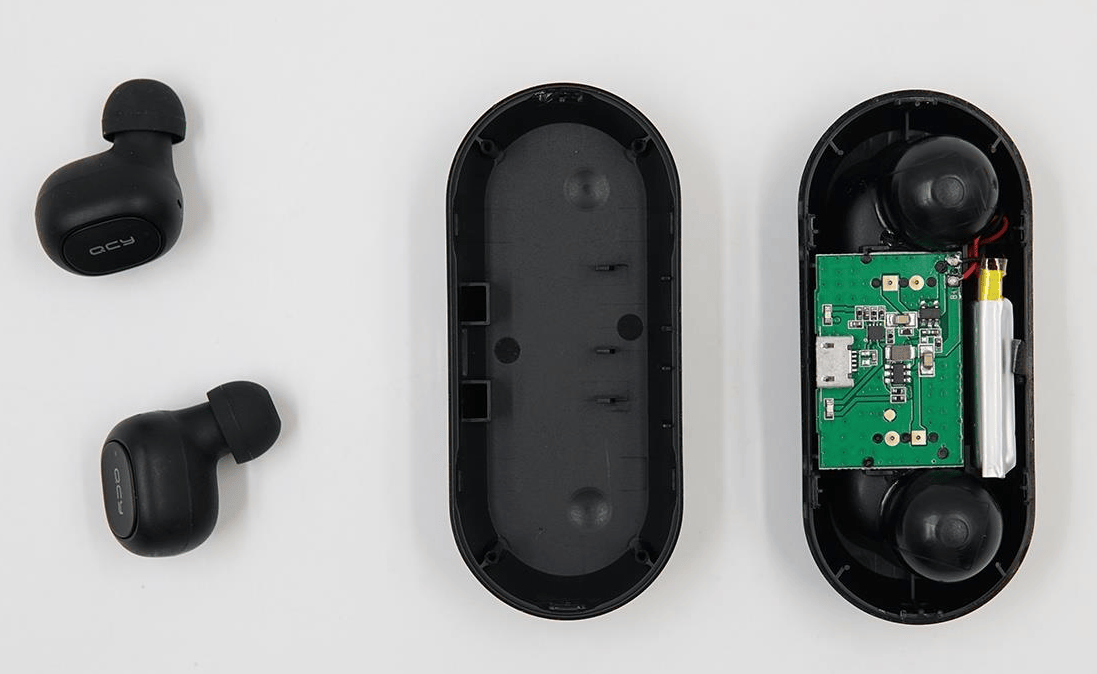

TWS 藍牙耳機 ESD EOS保護方案

簡析智慧燈桿一鍵告警功能的實用場景

優恩半導體推出一系列適用于高速數據信號ESD和EOS的保護器件

WAYON維安ESD和EOS產品特性簡析,幫你避開保護盲區

WAYON維安ESD和EOS產品特性簡析,幫你避開保護盲區

評論