編者按:模擬芯片技術的長期目標是在減少能量消耗的同時增加可操作信息量,從而實現高效、實時(低延遲)的傳感-模擬-信息通路,實際信息壓縮比期望做到10^5(即10萬):1。

在此十年中,美國將每年投資6億美元用于研究模擬電子的新方向。已選優先研究的課題羅列如下。

美國半導體十年計劃研討會牽頭制定了“模擬電子新方向”的長期目標,該研討會由學術界、工業界和政府實驗室的專家組成。“模擬電子新方向”包含以下五個研究領域:

太赫茲模擬技術

端側機器學習中的模擬技術

模擬設計的效率和生產可預測性

該文是模擬信息通信系統部分的翻譯,由于編譯人員經驗尚淺,不當之處,請多指教。

雖然沒人能準確預測未來信息與通信技術(ICT)將如何發展,但在技術可行性的前提下投入資源去探索最佳應用場景是值得的。人們的日常生活和經濟活動都離不開模擬ICT技術,正是通過模擬ICT技術來感知真實的物理世界,并與物理世界進行交互。

這部分討論模擬技術的基礎限制,并通過開放式討論以集思廣益,探討模擬技術未來的應用及其對半導體產業的影響。此外,還將討論模擬新技術帶動的新應用,或對能耗、帶寬等性能指標的顯著提高。從根本上來說,所有信號都是都是模擬信號,并被模擬或物理特性所限制。在很多場景中,相比先數字化再通過數字信號算法進行處理,模擬信號處理既快速又高效。

在眾多模擬ICT系統技術分支中,高速數模轉換器(ADC)是首要的研究方向,無論是6G無線通信、數據中心、遠程醫療和寬帶雷達波束成形,都需要高速ADC來增加帶寬。

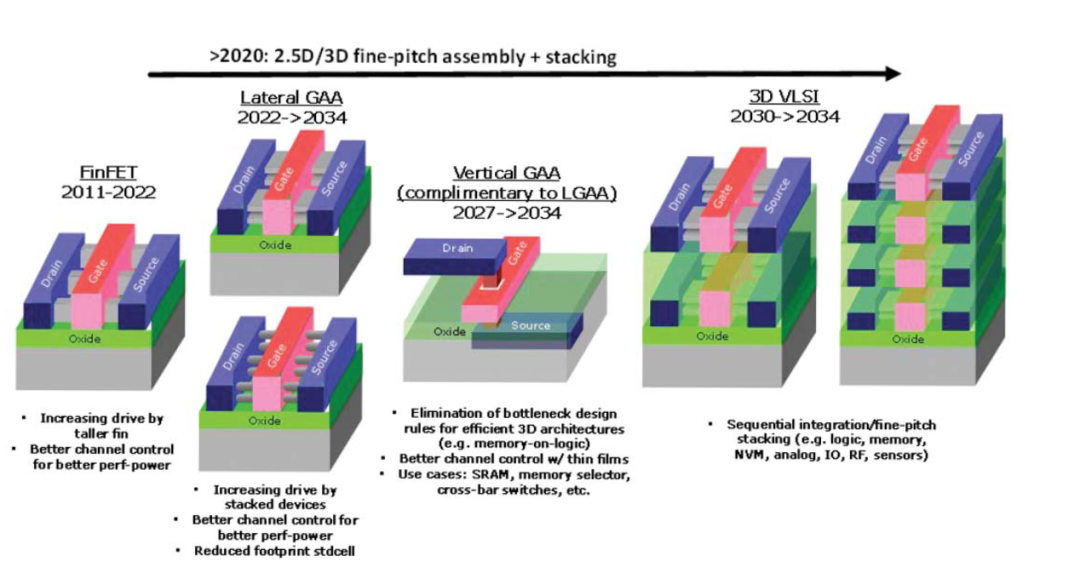

對密度和能效要求更高的存儲器技術推動了三維(3D)架構在超大規模系統集成在應用中的發展,3D集成在測試成本和熱管理上面臨挑戰,圖1顯示了從鰭式晶體管(FinFET)到全環繞柵極晶體管(Gate-All-Around FET)的發展路線圖,采用GAA工藝,有望提高存儲器的渠道控制能力,并消除設計規則帶來的瓶頸。包括“異構集成”在內的其他3D集成方法可以提供更快速高效的信息處理方法。

圖 1. 3D超大規模晶體管及架構演進路線圖

(來源:ADI Gabriele Manganaro)

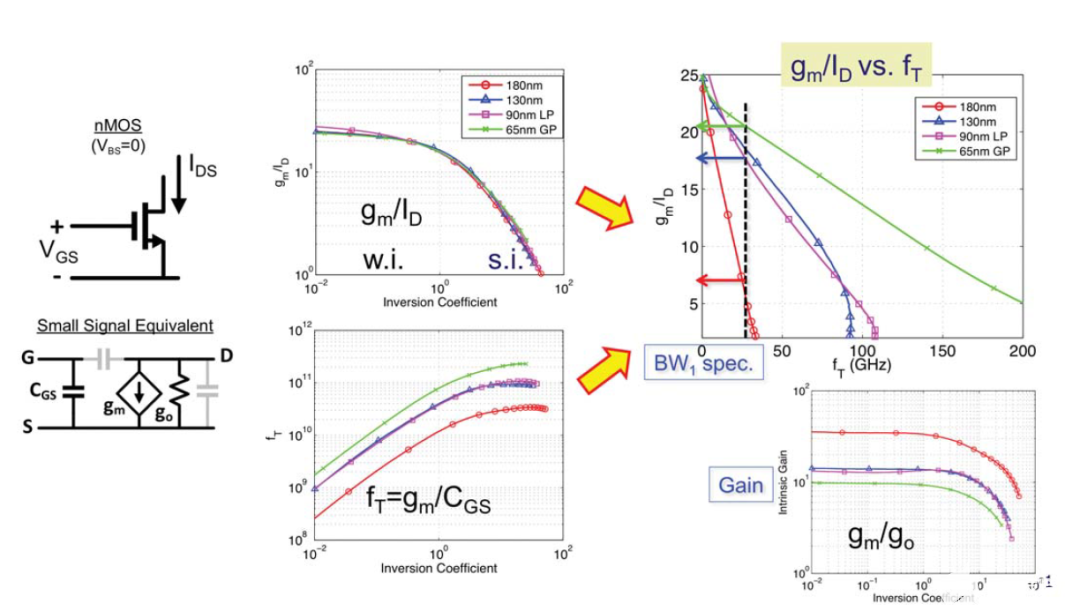

一個基礎問題是模擬電子技術創新如何助力當今先進計算與信息處理范式演進。而這就需要對器件縮放、高效信號處理與電路架構都有非常深入的理解。更需要透徹理解的是在功耗與其他性能(例如高增益、噪聲、漏電流和更低的電源干擾)之間進行平衡折中。圖2表現了一個理想NMOS晶體管在器件級的參數折中。

圖 2. MOS器件縮放應考慮參數示例

(來源:哥倫比亞大學 Peter Kinget)

伴隨工藝尺寸不斷縮小,電源效率在提升,但增益和轉換頻率的改善幅度急劇下降了,增益和轉換頻率沒有提升影響了器件在無線通信應用時的性能。也應該注意到,因為電源電壓與運行模式(Class A、ClassB等)相關,要考慮信號失真與噪聲限制,電源電壓就不能任意降低。

更新的電路架構有助于降低供電電壓。例如,傳統運算放大器的供電電壓VDD縮放技術會產生比較小的輸出擺幅、較高的飽和電壓,以及較大的噪聲預算都消耗在有噪聲限制的一階上。如果選擇開關模式拓撲,則可能同時實現軌到軌輸出、低輸出阻抗及更大的帶寬。

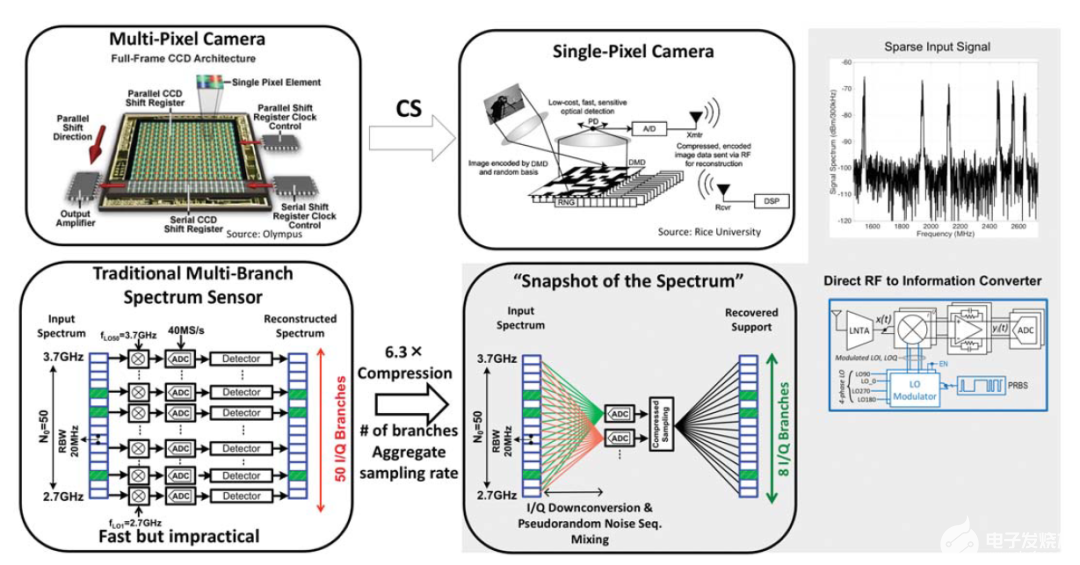

未來的(ADC)設計迭代將主要在三個方面進行。首先是更好(更高采樣率)的模數轉換技術,從而避免因有限帶寬的模擬信號而帶來的問題,模擬信號的帶寬限制是由于數字化時高效過采樣和量化操作而造成的。第二是利用壓縮采樣(compressive sampling, 簡稱CS)實現將稀疏模擬信號轉化為數字信號的信息轉化技術。第三是借助機器學習,在特征頻率低于信號最大頻率時,實現模擬信號的特征抽取。

壓縮采樣的一個應用是用單像素相機進行快速光譜掃描,如圖3所示。

圖 3. 壓縮采樣實現的快速光譜掃描

(來源:哥倫比亞大學 Peter Kinget)

下一個十年的傳感器與致動器技術

從業者對手機成本、尺寸、性能和帶寬的追求推動手機經濟不斷發展。其中,GPS導航、影像的光學和電子防抖,以及指紋認證等功能的成功,都離不開可靠的傳感器設計。過去五年來,手機常用傳感器的靈敏度和精準度提升了十倍,而功耗、成本和尺寸降為五年前的五分之一,這樣的趨勢還將延續。

物理學和人工智能在器件上的融合計算對基于MEMS(微機電系統)技術傳感器的創新設計有很好的推動作用,可以改善加速度計、陀螺儀、超聲波指紋傳感器、生物傳感器和麥克風等諸多MEMS傳感器的設計。所有這些傳感器應用到設備中,正越來越順暢地在航跡推測、穩定控制、撞擊檢測、自適應照明、圖像穩定和牽引控制等功能上發揮作用。

更好的傳感器性能,意味著更高的信噪比、更高的動態范圍,以及低于1毫瓦的功耗。研發人員也希望采用比55納米更先進的半導體工藝來制造傳感器,并采用超小尺寸環保封裝。傳感器與致動器及其相關的信號處理技術,在“智能傳感”一節中有詳述。

用16納米以下先進制程開發的

高良率與高性能兼具的ADC

下面以基于數字調制雷達(Digitally Modulated Radar)的車載雷達系統為例,說明為何需要高速ADC。(數字)偽隨機序列(Pseudo-Random Binary Sequence,簡稱PRBS)調制到連續波載波信號(79GHz)后,作為測距信號發射出去。

設計PRBS要滿足三個要求,即減少距離模糊(序列長度)和提高距離分辨率(脈沖寬度帶寬),并提供優異的抗干擾能力。雷達的工作原理,是依靠ADC對接收到的反射信號采樣,并實時進行相關與累加計算,從而得到被測目標的距離范圍,最后可以通過快速傅里葉變換(FFT)得到被測目標的速度。和基于調頻連續波(Frequency Modulated Continuous-Wave,簡稱FMCW)的雷達相比,數字調制雷達方案更簡單,但是對信號處理的能力要求極高,相關器和累加器要能處理從數吉赫茲(GHz)ADC送出的數字信號。如果再考慮利用基于多入多出(MIMO)技術的波束成形來提升探測范圍和角分辨率精度,那么計算速度就要進一步提升了。

要接收PRBS信號,就需要極高帶寬(2-5GHz)的ADC,高帶寬ADC相應也要求高采樣率(4GS/s-10GS/s),在如此高帶寬和高采樣率時,如何對抗器件信號的抖動、偏移、噪聲等非理想特性,讓開發設計變得更難。再考慮在同一顆裸芯片(die)上對數吉赫茲ADC輸出的數據進行相關、累積與快速傅里葉變換等實時處理的需求,情況就更為復雜。

這就需要用當前最先進的CMOS工藝(例如16納米或更小節點)來實現吉赫茲ADC輸出數據的處理功能,這也推動了采用與ADC數據處理器相同的工藝(16納米以下)來實現ADC的需求。以一個28納米CMOS工藝用于數字調制雷達的收發器為例,該架構能有效實現增益(大于70dB),但該收發器的性能確實受制于28納米工藝,因而處理數字信號速度還不夠快,這是需要更先進CMOS工藝來實現ADC的直接例證。

商業應用對吉赫茲ADC技術(16納米以下工藝實現)有迫切需求,例如基于數字調制雷達的車載雷達系統,所以對該領域的研究有相應的迫切需求。

在這方面,很多大學里對吉赫茲采樣率ADC的研究僅集中在功耗、有效位數(ENOB)和采樣率等三大指標上,但此類研究完全忽視了ADC在實際應用中需要考慮的關鍵因素,例如干擾、工作溫度范圍、成本等指標。因此,面向應用的商用ADC設計必須符合大批量生成的要求,能通過嚴苛的環境溫度與可靠性測試,并具備優良的品質因數。因此,學術界和工業界對吉赫茲ADC的研究都必須統一到可批量商用方向上,這就要求大學、工業界和科研資助機構(例如美國科學研究委員會SRC、美國國防部高級計劃研究局DARPA及美國國家科學基金會NSF等)通力合作,一起向著這個目標將ADC技術推進到16納米以下工藝。

基于氮化鎵等優良工藝的功率電子技術

電子系統的每個組件都需要電源供電,而電源供電的轉換方式呈現出多種多樣的形態。地球上的電子設備越來越多,所有的電子設備都在推動電源市場增長,也都需要更高的能源效率。此外,能源密度不再只是移動設備的關注點,從移動設備到數據中心,都要重視能源密度,乃至基礎的阻容元件耗電都要考慮。業界正專注于如何用創新的解決方案來滿足電子設備對于電源轉換模塊的尺寸、成本與效率的要求。用從基礎元器件到線路拓撲以及電源鏈路架構的全局思維來進行研究,從而得到更優的解決方案,以提升電源鏈路性能。

巴利加(Baliga)高頻品質因數是功率半導體在高頻工作時的重要指標。該品質因數揭示,功率器件的功率損耗會隨著工作頻率平方根而增長,也與輸出功率大小近成比例。采用更高遷移率和更大臨界擊穿電場工藝制造的功率器件可有效降低功率損耗。氮化鎵(GaN)器件的柵極電容低,阻抗低,因而柵極驅動損耗低,所以能有效減少電源損耗。在無線電力傳輸和自動駕駛中,則通常采用包絡跟蹤等技術,來有效提升電源轉換效率,減少熱損耗帶來的能量損耗。

而且,將GaN器件集成到更高層級的集成電路也是一種趨勢。例如單片柵極驅動和開關、片上電源系統、單封裝電源系統,以及集成有源功率插入器的穩壓器(Power and Active Interposers with integrated voltage regulators.)。特別是片上電源(PowerSoC),可集成控制器、柵極驅動、傳感電路、保護電路和電感(或變壓器)。集成穩壓器優點很多,例如,為超大規模集成電路系統減少片上面積,以及提高工作頻率與電池壽命等。在《2018 GaN功率電子路線圖(The 2018 GaN power electronics roadmap)》中,討論了當前GaN技術的發展趨勢。

襯底技術的進一步發展將能有效推動GaN技術向前發展。例如,200毫米硅基氮化鎵和

GaN-on-CTE(熱膨脹系數?)襯底都前途光明。而且,氧基氮化鎵(GaNoX)晶體質量奇佳,適用范圍很廣,與碳化硅器件相比(電壓到1200V),性價比又有優勢。由于成本低、效率高,預計GaN晶體管將取代普通硅功率MOSFET。最后,超寬禁帶(UWBG)器件在效率和能源密度上更具優勢。

應用于人工智能的

模擬突觸器件(Analog Synaptic Devices)

借鑒生物技術,模擬設計得以實現神經形態學習與存內計算,從而更高效地處理傳感器實時信號。但是,基于云計算的深度學習算法非常耗電,而基于物聯網技術的邊緣設備在處理傳感器數據時相對節能,因此在自適應傳輸學習(adaptive transfer learning)中更適合采用邊緣設備。

而新興非易失存儲器(eNVM)可支持每瓦每秒100萬億次運算(100 TOPS/W),應用場景廣泛,這些新興非易失存儲器技術包括導電細絲阻變存儲器和非導電細絲阻變存儲器( Filamentary and Non-Filamentary RRAMs)、相變存儲器、鐵電存儲器等。新興非易失存儲器架構如圖4所示。

這些eNVM將被優化設計以打造更高密度的計算存儲(In-Compute Memories, 簡稱ICM),該類器件耗能更低,可以增加密文并有助于實現同態加密。

另外,理想情況下,新架構中使用的交叉開關陣列能實現高效ADC,可以調節每列數據的精度。新架構在解決適定性(satisfi ability,簡稱SAT)問題方面將有很多應用,例如預測集成電路中的串擾噪聲、模型核驗、有效狀態系統測試、邏輯綜合中的技術映射,以及自動推理。

據此,模擬SAT解算方案在時鐘、面積和能耗上將(比數字SAT解算方案)更高效,利用單變單元(single variable cells)或開關可變電容技術,模擬SAT獨辟蹊徑,可以更好地在時鐘和功耗之間達到平衡。模擬SAT解算方案與計算存儲(ICM)是熱門領域,正在受到廣泛研究,其中可擴展模塊化并行電路與系統可用于SAT解算,而本地SRAM和低功耗電荷域乘積計算元素技術可用于開發可編程ICM單元。在傳感器數據處理方面,模仿人腦對信息處理的仿生系統是大熱方向,例如用電路實現神經突刺(neural spiking)以及如何激發更多神經突刺,而大規模并行單可變單元實現的偽模擬存儲(pseudo-analog memory)也將有助提高傳感器數據處理效率。

圖 4. 應用于AI引擎的模擬突觸器件結構

審核編輯 :李倩

-

adc

+關注

關注

98文章

6524瀏覽量

545202 -

無線通信

+關注

關注

58文章

4587瀏覽量

143687 -

數模轉換器

+關注

關注

14文章

1016瀏覽量

83273

發布評論請先 登錄

相關推薦

電子技術在智能電網中的應用

單片機在電子技術中的應用及發展

醫療電子技術:創新與挑戰

心態年輕 篤行至善 ——專訪金航標電子技術顧問張武軍教授

直流高壓電源技術發展淺析

智能面膜的設計生產與發展——印刷電子技術應用

模擬電子技術如何助力信息通信系統發展

模擬電子技術如何助力信息通信系統發展

評論