無論你使用圖形化設計程序,ANSIC語言還是VHDL語言,如此復雜的合成工藝會不禁讓人去想FPGA真實的運作情況。在這個芯片中的程序在這些可設置硅片間到底是如何工作的。本文會使非數字化設計人員明白FPGA(現場可編程門陣列)的基礎知識及其工作原理。此信息在使用高端設計工具時同樣十分有用,希望可以為理解這一特別技術提供一些線索。

1FPGA-現場可編程門陣列

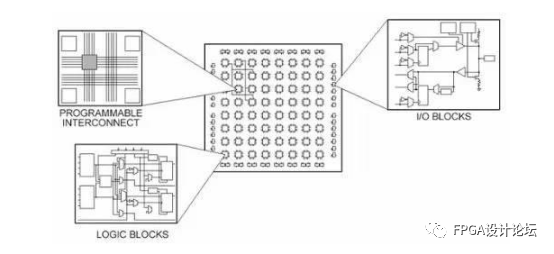

每一塊FPGA芯片都是由有限多個帶有可編程連接的預定義源組成來實現一種可重構數字電路。

FPGA芯片說明書中,包含了可編程邏輯模塊的數量、固定功能邏輯模塊(如乘法器)的數目及存儲器資源(如嵌入式RAM)的大小。FPGA芯片中還有很多其它的部分,但是以上指標通常是為特定應用選擇和比較FPGA時,最重要的參考指標。

在最底層,可配置邏輯模塊(如片或邏輯單元)有著兩種最基本的部件:觸發器和查找表(LUT)。這很重要,因為各種FPGA家族之所以各不相同,就是因為觸發器和查找表組合的方式不同。例如,Virtex-II 系列的FPGA ,它的片具有兩個查找表和兩個觸發器,而Virtex-5 FPGA的片具有4個查找表和4個觸發器。查找表本身的結構也可能各不相同(4輸入或6輸入)。

表1中列出了在NI LabVIEW FPGA硬件目標中使用的FPGA的指標。邏輯門的數量是一種將FPGA芯片與ASIC技術進行比較的傳統方法,但是它并不能真實地表述FPGA內部的獨立單元的數量。這就是Xilinx公司沒有在新型Virtex-5系列中指定邏輯門數量的原因之一。

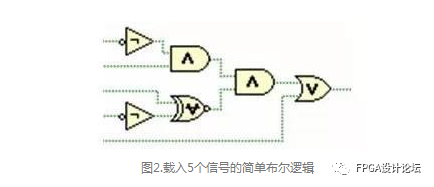

為了更好地理解這些規格的意義,將編碼考慮為合成的數字電路模式。對任何一段合成代碼,或圖形化或文本形式,都有相應的電路圖反映邏輯組件該如何連線。通過一段簡單布爾邏輯電路了解下相應的示意圖。圖2表示的是傳遞5個布爾信號并且可圖形化計算所得的二進制值的功能組。

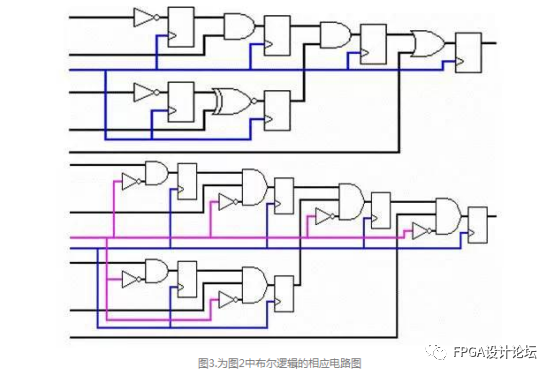

在通常情況下(除LabVIEW SCTL—單周期定時環路外),圖2所示相應電路圖同圖3所示相近。

雖然很難明白,但是實際上這里創建了兩個并行分支的電路。最上面的5條黑線被反饋到第一個分支,它在每個布爾操作間添加了觸發器。最下面的5條黑線構成了第二個邏輯鏈。其中一支路在每步操作之間增加了同步寄存器,另一條邏輯鏈是確保執行數據流的。本電路圖正常工作時總共需要12個觸發器和12個查找表。

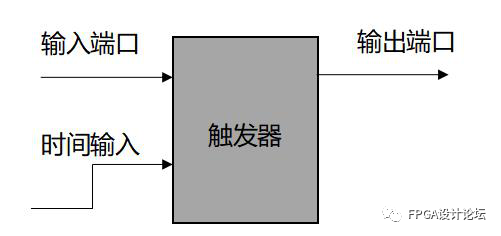

2觸發器

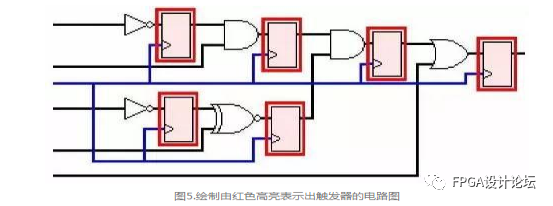

觸發器是二進制移位寄存器,用于同步邏輯以及保存時鐘(脈沖)周期內的邏輯狀態。在每個時間(脈沖)邊沿,觸發器在輸入時鎖定1(真)或0(假)值并且保存此值直到下次時鐘(脈沖)邊沿。在正常情況下,LabVIEW FPGA在每次操作之間都設置一個觸發器,以保證有足夠的時間來執行每步操作。對此律的例外只發生在SCTL結構中寫代碼的情況。在這個特殊的環路結構中,觸發器只放置在閉環迭代的始末段,并且由編程者考慮定時因素來決定如何放置。圖5表示的是圖3的上端分支,觸發器由紅色高亮表示。

3查找表

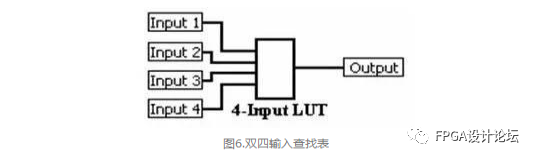

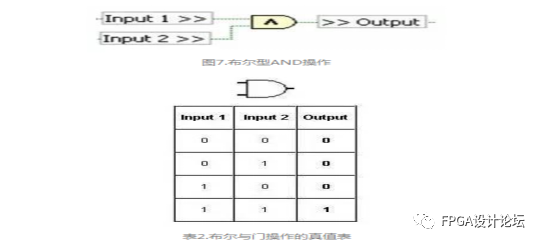

圖6所示示意圖中的其他邏輯電路通過使用少量查找表形式的隨機存取存儲器實現。我們可以簡單地假定FPGA中系統門的數量可參考與非門(NAND)以及或非門(NOR)的數量,但實際上,所有的組合邏輯(與門、或門、與非門、異或門等)都是通過查找表存儲器中的真值表來實現。真值表是輸出對應于每個輸入值組合的預定義表(現在卡諾圖的重要性在你的頭腦中可能會慢慢淡化)。以下是對數字邏輯電路課程的快速回顧:比如,圖7是布爾邏輯與門操作過程。

這是對數字邏輯課程的快速回顧:

例如,圖7中顯示了布爾型AND操作。

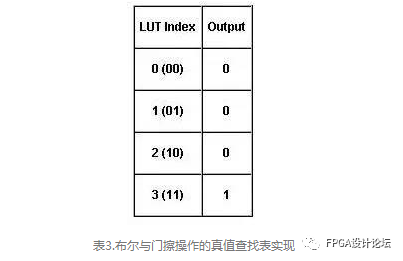

你可以認為輸入值是所有輸出值的數字索引,如表3所示。

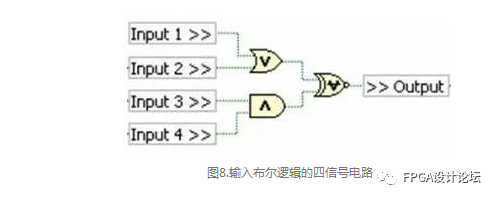

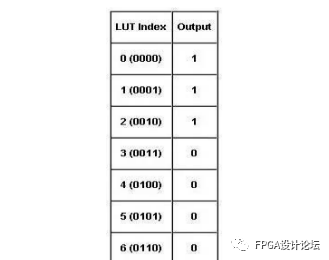

Virtex-II和Spartan-3系列FPGA芯片有著4輸入查找表來實現真正的4輸入信號的16種組合。圖8就是一個四輸入電路實現的例子。

表4所示為使用雙四輸入查找表實現的相應的真值表。

Virtex-5系列的FPGA使用雙六輸入查找表,可以通過6個不同輸入信號的64種組合來實現真值表。因為觸發器之間的組合邏輯十分復雜,所以在LabVIEW FPGA中使用SCTL也越來越重要。下一節將講述SCTL如何優化利用LabVIEW中的FPGA源。

4SCTL

上幾節中使用的代碼例子假定代碼是設置在SCTL外部,并為保證執行同步數據量也同步了附加電路。SCTL是LabVIEW FPGA中一個特殊結構,生成一個更為優化的電路圖,以期望達到在一個時鐘(脈沖)周期內執行完所有邏輯電路分支。例如,若設置SCTL在40MHZ運行,則所有邏輯電路分支將在25ns內執行完畢。

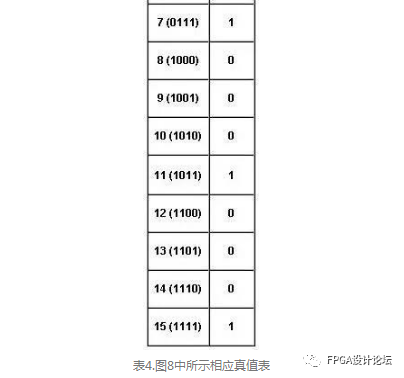

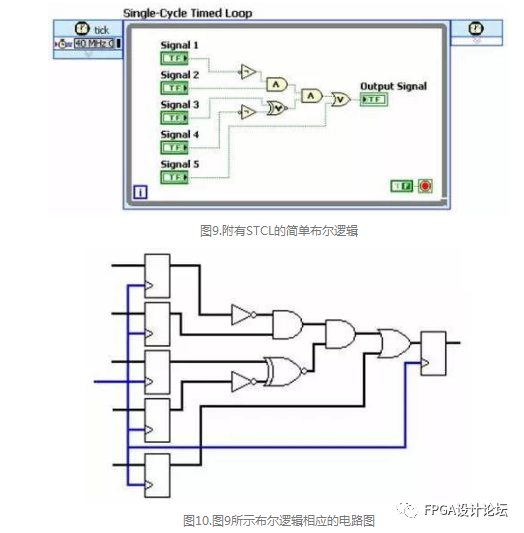

如果在SCTL中設置前例中同樣的布爾邏輯電路(如圖9所示),則生成如圖10所示的相應電路示意圖。

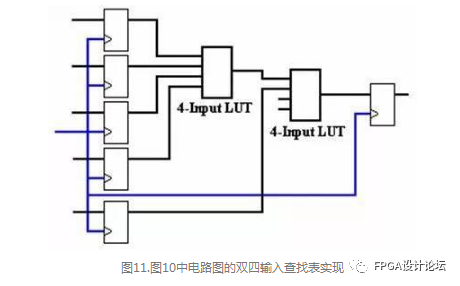

很明顯,這種實現方法簡單多了。在Virtex-II或Spartan-3系列FPGA中,觸發器間的邏輯需要至少2個4輸入查找表,如圖11所示。

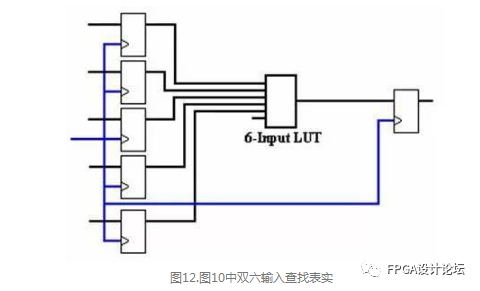

由于Virtex-5系列FPGA有著6輸入的查找表,用戶可以在一個查找表中實現相同數量的邏輯,如圖12所示。

本例中使用的SCTL(如圖9所示)設置在40MHZ下運行,這意味著在任意觸發器之間邏輯電路必須在25ns內完成執行。電子在電路中傳播的速度決定了代碼執行的最大速度。關鍵路線是有最長傳播延遲的邏輯電路分支,它決定了該部分電路中理論最大時鐘速率。Virtex-5 FPGA上的雙六輸入查找表不僅減少實現給定邏輯電路所需要的查找表總數,而且減少電子通過邏輯電路的傳播延遲(時間)。Virtex-5系列FPGA中的6輸入查找表不僅可以減少實現特定邏輯而需要的查找表的數量,而且可以降低邏輯中電流的傳輸延時。這意味著,您可簡單地通過選擇一個基于Virtex-5的硬件指標設置相同的SCTL,追求更快的時間速度。

5乘法器和DSP片

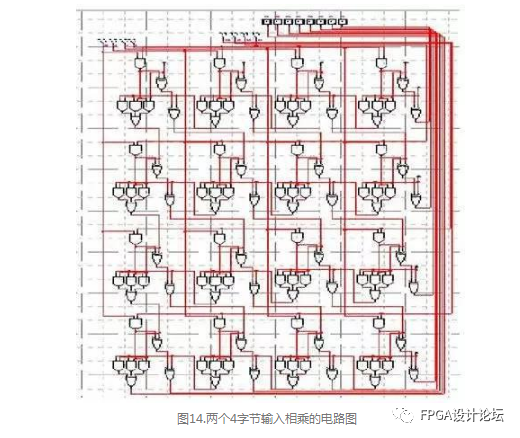

看起來簡單的兩數相乘運算在數字電路中實現起來是十分復雜的,也是極為消耗資源的。為提供相關參考,圖14所示是一種使用組合邏輯電路實現4×4字節乘數器的示意圖。

試想兩個32字節的數字相乘要通過2000多步操作才能得到結果。因此,FPGA預設了乘數器電路,在數學和信號處理應用中保存對查找表和觸發器使用。Virtex-II和Spartan-3 FPGA擁有18×18bit乘法器,所以兩個32字節數字相乘的運算需要三個乘法器來實現。許多信號處理算法都包括連乘運算結果的功能,因此Virtex-5等高性能FPGA都預設被稱為DSP片的乘數器累加電路.這些預設處理組件,也被稱為DSP48片,包括25×18bit乘數器以及加法器電路,盡管您可單獨使用乘數器功能。表5所示為不同FPGA系列DSP決策。

6塊隨機存取存儲器

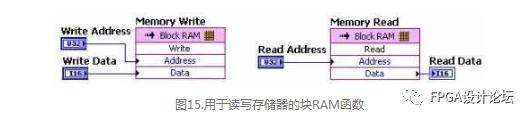

選擇FPGA時,記憶源是另一個需要考慮的關鍵因素。嵌入FPGA芯片中的用戶自定義隨機存取存儲器(RAM),對儲存數據設置或平行環路之間傳送數值很有幫助。基于FPGA系列,您可在16或36kb組件中設置板載RAM,或者使用觸發器以數組來執行數據設置;然而,對于FPGA邏輯源來說,大型數組很快就變得十分“奢侈”。由100個32字節元素數組可消耗Virtex-II 1000 FPGA中超過30%的觸發器,或者占用少于1%的嵌入式塊RAM。DSP算法通常需要追蹤整個數據塊或是復雜等式的系數,而在沒有板載存儲器情況下,許多處理功能在FPGA芯片的硬件邏輯電路中都不適用。圖16所示為使用塊RAM讀寫存儲器的圖形化功能。

同樣,你也可以使用內存塊,將一段完整周期存儲為數值和索引的順序表,為板載信號發生器存儲周期性波形數據。輸出信號的最終頻率由檢索數值的速度決定,這樣您就可用此方法動態改變輸出頻率,而不需要輸入波形中的急劇變化。

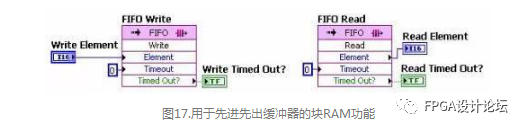

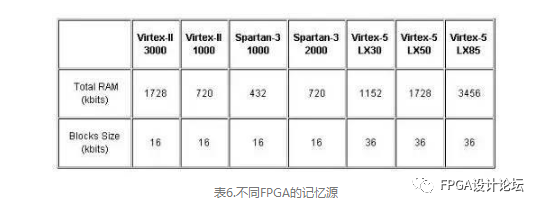

FPGA固有的并行執行要求邏輯電路獨立元件可在不用時間脈沖下驅動。在不同運行速度下的邏輯電路之間傳遞數據是很棘手的。使用先進先出(FIFO)緩沖器時,板載存儲器可用來是傳輸更加平穩。如圖16所示,用戶可以將FIFO緩沖器配置成不同大小以確保數據在FPGA芯片的非同步部件間不會丟失。表6所示為嵌入不同FPGA系列的用戶可設置快RAM。

7總結

隨著高端技術的發展以及新概念的深入概括,FPGA技術地采用將不斷增加。然而探究FPGA其中奧秘,感嘆這硅片中在方框圖間匯編出的變化,也是十分重要的。在發展階段,如果您懂得如何利用和優化資源,比較和選擇觸發器、查找表、乘數器和塊RAM等硬件指標是十分有幫助的。這些基本的功能塊并不是包含所有資源的完整清單,而且這篇白皮書并沒有包含對所有FPGA部件的討論。

審核編輯 :李倩

-

FPGA

+關注

關注

1629文章

21750瀏覽量

604084 -

存儲器

+關注

關注

38文章

7507瀏覽量

163955

發布評論請先 登錄

相關推薦

FPGA-現場可編程門陣列

FPGA-現場可編程門陣列

評論