隨著FPGA的集成度越來越高,規模越來越大,設計越來越復雜,IC行業的競爭也越來越激烈,產品的交付周期越來越短,這與人類有限的設計能力形成了巨大矛盾。如果FPGA設計還是全部由設計者從最底層的代碼寫起,那么必然不能在越來越苛刻的開發周期內完成相關項目。

而IP核的出現,解決了這個問題。IP核是一段具有特定電路功能的硬件描述語言程序,該程序通常與集成電路工藝無關,可以移植到不同的半導體工藝中去生產集成電路芯片。由于IP核將一些在數字電路中常用,但比較復雜的功能塊設計成可修改參數的模塊,因此FPGA的設計人員可以通過調用相關IP核來完成所需邏輯功能,從而節省了大量的開發時間。調用IP核能避免重復勞動,大大減輕設計人員的負擔,因此使用IP核必然成為將來FPGA設計的一個發展趨勢。

按IP核的硬件描述級實現程度,可將它分為三類:即軟核、硬核、固核。

IP軟核一般指的是用硬件描述語言描述的功能塊,它并不涉及用什么具體電路元件實現這些功能,軟核的代碼直接參與設計的編譯流程,就像我們自己編寫的HDL代碼一樣,雖然一般會對軟核的RTL代碼進行加密,但是其保密性還是比較差。

IP硬核是以經過完全的布局布線的網表形式提供,由于不再參與設計的編譯流程,因此它的性能具有很強的可預見性,并且保密性好,不過移植性差。

IP固核是軟核與硬核的一個折中,它只對描述功能中一些比較關鍵的路徑進行預先的布局布線,而其他部分仍然可以任由編譯器進行相關優化處理。例如,當你使用IP核生成一個8x8的乘法器時,如果選擇使用邏輯資源塊來實現的話,那么此時的乘法器IP核就相當于一個軟核;

如果你選擇使用DSP資源來實現的話,那么此時的乘法器IP核就相當于一個硬核;如果你要用DSP資源生成一個36x36的乘法器時,那么FPGA恐怕需要若干DSP資源來實現,這時候,每個DSP核的布局布線是固定的,但是到底選擇那幾個DSP資源來實現是可以由編譯器來決定的,因此此時的乘法器IP核就相當于一個固核。

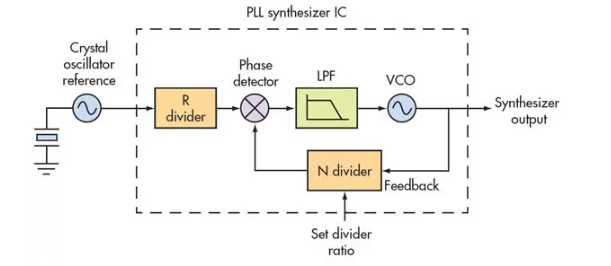

PLL(Phase Locked Loop): 為鎖相回路或鎖相環,用來統一整合時鐘信號,使高頻器件正常工作,如內存的存取資料等。PLL用于振蕩器中的反饋技術。許多電子設備要正常工作,通常需要外部的輸入信號與內部的振蕩信號同步。

一般的晶振由于工藝與成本原因,做不到很高的頻率,而在需要高頻應用時,由相應的器件VCO,實現轉成高頻,但并不穩定,故利用鎖相環路就可以實現穩定且高頻的時鐘信號。鎖相環路是一種反饋控制電路,簡稱鎖相環(PLL,Phase-Locked Loop)。

鎖相環的特點是:利用外部輸入的參考信號控制環路內部振蕩信號的頻率和相位。因鎖相環可以實現輸出信號頻率對輸入信號頻率的自動跟蹤,所以鎖相環通常用于閉環跟蹤電路。鎖相環在工作的過程中,當輸出信號的頻率與輸入信號的頻率相等時,輸出電壓與輸入電壓保持固定的相位差值,即輸出電壓與輸入電壓的相位被鎖住,這就是鎖相環名稱的由來。鎖相環通常由鑒相器(PD,Phase Detector)、環路濾波器(LF,Loop Filter)和壓控振蕩器(VCO,Voltage Controlled Oscillator)三部分組成。

FIFO: 是英文First In First Out 的縮寫,是一種先進先出的數據緩存器,他與普通存儲器的區別是沒有外部讀寫地址線,這樣使用起來非常簡單,但缺點就是只能順序寫入數據,順序的讀出數據, 其數據地址由內部讀寫指針自動加1完成,不能像普通存儲器那樣可以由地址線決定讀取或寫入某個指定的地址。

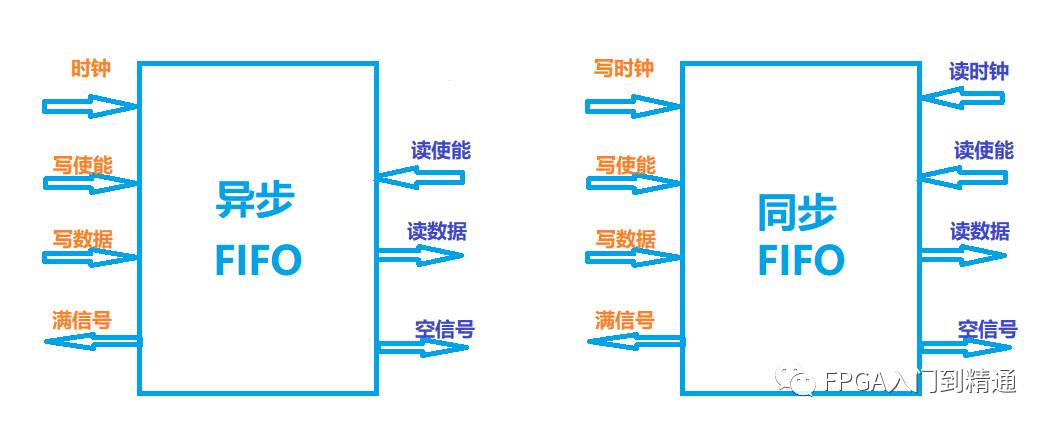

FIFO的分類根均FIFO工作的時鐘域,可以將FIFO分為同步FIFO和異步FIFO。同步FIFO是指讀時鐘和寫時鐘為同一個時鐘。在時鐘沿來臨時同時發生讀寫操作。異步FIFO是指讀寫時鐘不一致,讀寫時鐘是互相獨立的。

FIFO的寬度: 也就是英文資料里常看到的THE WIDTH,它指的是FIFO一次讀寫操作的數據位,就像MCU有8位和16位,ARM32位等等,FIFO的寬度在單片成品IC中是固定的,也有可選擇的,如果用FPGA自己實現一個FIFO,其數據位,也就是寬度是可以自己定義的。FIFO的深度:THE DEEPTH,它指的是FIFO可以存儲多少個N位的數據(如果寬度為N)。如一個8位的FIFO,若深度為8,它可以存儲8個8位的數據,深度為12 ,就可以存儲12個8位的數據,FIFO的深度可大可小,個人認為FIFO深度的計算并無一個固定的公式。

在FIFO實際工作中,其數據的滿/空標志可以控制數據的繼續寫入或讀出。在一個具體的應用中不可能由一些參數精確算出所需的FIFO深度為多少,這在寫速度大于讀速度的理想狀態下是可行的,但在實際中用到的FIFO深度往往要大于計算值。

一般來說根據電路的具體情況,在兼顧系統性能和FIFO成本的情況下估算一個大概的寬度和深度就可以了。而對于寫速度慢于讀速度的應用,FIFO的深度要根據讀出的數據結構和讀出數據由那些具體的要求來確定。

ADC/DAC: adc是analog-to-digital converter的縮寫,指模擬/數字轉換器。我們常用的模擬信號,如溫度、壓力、電流等,如果需要轉換成更容易儲存、處理的數字形式,用模/數轉換器就可以實現這個功能。

adc將模擬輸入信號轉換成數字信號的電路或器件。模數轉換器的實例有逐次逼近adc,電壓-頻率(v/f)轉換器,雙斜率adc和高速閃爍adc。模數轉換器也稱為數字化儀。a/d轉換的作用是將時間連續、幅值也連續的模擬量轉換為時間離散、幅值也離散的數字信號,因此,a/d轉換一般要經過取樣、保持、量化及編碼4個過程。

在實際電路中,這些過程有的是合并進行的,例如,取樣和保持,量化和編碼往往都是在轉換過程中同時實現的。dac是digital-to-analog converter的縮寫,指數字/模擬轉換器。數字量是用代碼按數位組合起來表示的,對于有權碼,每位代碼都有一定的位權。

為了將數字量轉換成模擬量,必須將每1位的代碼按其位權的大小轉換成相應的模擬量,然后將這些模擬量相加,即可得到與數字量成正比的總模擬量,從而實現了數字/模擬轉換。dac主要由數字寄存器、模擬開關、位權網絡、求和運算放大器和基準電壓源(或恒流源)組成。用存于數字寄存器的數字量的各位數碼,分別控制對應位的模擬電子開關,使數碼為1 的位在位權網絡上產生與其位權成正比的電流值,再由運算放大器對各電流值求和,并轉換成電壓值。

IP代表知識產權,從它的名字我們就能猜到IP核應該不是可以隨便使用的。事實上,大部分IP核都是需要付費的,例如RS編碼器、FIR濾波器、SDRAM控制器、PCI接口等。不過仍有很多免費的IP核資源,這其中最主要的就是每個FPGA廠商都會為自己的軟件集成開發環境提供一些比較基本的免費的IP核來增加自家產品的行業競爭力。例如最最常用的FIFO模塊、PLL模塊等等。對于我們平常的設計來說,利用好這些免費的IP核就能達到事半功倍的效果。

-

FPGA

+關注

關注

1630文章

21759瀏覽量

604340 -

IC

+關注

關注

36文章

5965瀏覽量

175795

發布評論請先 登錄

相關推薦

分享一些FPGA常見IP核

分享一些FPGA常見IP核

評論