DS2780電流測(cè)量失調(diào)誤差與電路板布局密切相關(guān)。測(cè)量電路的總環(huán)路面積應(yīng)最小化,以限制電感對(duì)測(cè)量失調(diào)的影響。

介紹

與任何庫(kù)侖計(jì)數(shù)IC一樣,正確的電路板布局對(duì)于在測(cè)量電流時(shí)保持精度非常重要。DS2780補(bǔ)償與增益相關(guān)的電流測(cè)量誤差,但不能補(bǔ)償失調(diào)誤差。為了將電流測(cè)量失調(diào)誤差降至最低,Dallas Semiconductor建議使用DS2780的電路設(shè)計(jì)人員遵循本應(yīng)用筆記中的布局建議。

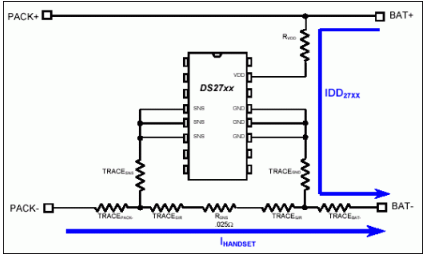

應(yīng)用電路

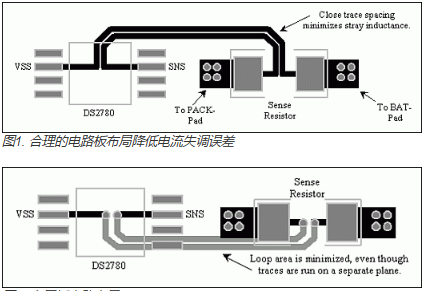

由于電池組的尺寸限制,元件通常僅安裝在PCB的一側(cè)。此外,較窄的PCB寬度通常會(huì)限制TSSOP8封裝(如DS2780)只能使用與PCB長(zhǎng)度對(duì)齊的封裝引線進(jìn)行安裝。這嚴(yán)重限制了元件安裝選項(xiàng)。圖 1 顯示了 SNS 和 VSS 跟蹤的理想布局。檢測(cè)電阻應(yīng)盡可能靠近IC放置,VSS和SNS之間的環(huán)路面積應(yīng)保持在絕對(duì)最小值,以盡量減少走線之間的雜散電感。有時(shí)這無(wú)法在單個(gè)PCB平面上完成。圖 2 顯示了必須通過(guò)單獨(dú)的平面路由 VSS 和 SNS 時(shí)的最佳布局。未能限制PCB電感會(huì)產(chǎn)生大于數(shù)據(jù)手冊(cè)規(guī)格的A/D失調(diào)誤差。

圖1.正確的電路板布局,以最大限度地降低電流失調(diào)誤差。

圖2.在多個(gè)平面上正確的電路板布局。

總結(jié)

DS2780無(wú)法調(diào)整VSS阻抗或VSS電感引起的電流測(cè)量失調(diào)誤差。電路板的設(shè)計(jì)應(yīng)通過(guò)限制VSS和SNS走線之間的閉環(huán)空間來(lái)最大程度地減少這些影響。增益誤差可以通過(guò)軟件調(diào)整來(lái)校正,因此不需要針對(duì)增益精度的特定布局規(guī)則。

審核編輯:郭婷

-

pcb

+關(guān)注

關(guān)注

4335文章

23245瀏覽量

402258 -

電路板

+關(guān)注

關(guān)注

140文章

5027瀏覽量

99818

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

TAS5630如何才能最大限度地減少電壓失調(diào),或者調(diào)節(jié)為0?

如何在密集PCB布局中最大限度降低多個(gè)isoPower器件的輻射

在密集PCB布局中最大限度降低多個(gè)isoPower器件的輻射

怎么減小相電流測(cè)量的誤差影響?

合理的DS2780線路板布局降低電流測(cè)量失調(diào)誤差

在密集PCB布局中最大限度降低多個(gè) isoPower器件的輻射資料下載

具有降低電流測(cè)量失調(diào)誤差的替代DS2740U應(yīng)用電路

DS27xx電量計(jì)電路板布局技巧,實(shí)現(xiàn)測(cè)量誤差最小化

合理的DS2780線路板布局降低電流測(cè)量失調(diào)誤差

如何最大限度地降低差分測(cè)量誤差?

DS2780電路板布局,最大限度降低電流測(cè)量失調(diào)誤差

DS2780電路板布局,最大限度降低電流測(cè)量失調(diào)誤差

評(píng)論