1. 斜體和粗體

使用 * 和 ** 表示斜體和粗體。

示例:

這是 斜體 ,這是 粗體 。

2. 分級標題

使用 === 表示一級標題,使用 --- 表示二級標題。

示例:

這是一個一級標題

============================

這是一個二級標題

--------------------------------------------------

### 這是一個三級標題

你也可以選擇在行首加井號表示不同級別的標題 (H1-H6),例如:# H1, ## H2, ### H3,#### H4。

3. 外鏈接

使用 描述 為文字增加外鏈接。

示例:

這是去往 本人帳號 的鏈接。

4. 無序列表

使用 *,+,- 表示無序列表。

示例:

- 無序列表項 一

- 無序列表項 二

- 無序列表項 三

5. 有序列表

使用數字和點表示有序列表。

示例:

- 有序列表項 一

- 有序列表項 二

- 有序列表項 三

6. 文字引用

使用 > 表示文字引用。

示例:

野火燒不盡,春風吹又生。

7. 行內代碼塊

使用 代碼 表示行內代碼塊。

示例:

讓我們聊聊 html。

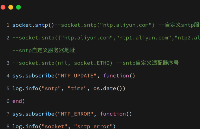

8. 代碼塊

使用 四個縮進空格 表示代碼塊。

示例:

這是一個代碼塊,此行左側有四個不可見的空格。

9. 插入圖像

使用 !\\[描述](圖片鏈接地址) 插入圖像。

10.空白行

(1)html換行標簽:

在任意的位置輸入即可以實現換行效果。

<br/>

(2)使用nbsp:

只有在空白行才能換行,否則只能作為一個空格。

更多MarkDown語法請參見 :

學習更多編程知識,請關注我的公眾號:

[代碼的路]

聲明:本文內容及配圖由入駐作者撰寫或者入駐合作網站授權轉載。文章觀點僅代表作者本人,不代表電子發燒友網立場。文章及其配圖僅供工程師學習之用,如有內容侵權或者其他違規問題,請聯系本站處理。

舉報投訴

-

編程

+關注

關注

88文章

3633瀏覽量

93848 -

代碼

+關注

關注

30文章

4808瀏覽量

68808 -

語法

+關注

關注

0文章

44瀏覽量

9844 -

MarkDown

+關注

關注

0文章

46瀏覽量

278

發布評論請先 登錄

相關推薦

Verilog硬件描述語言參考手冊

一. 關于 IEEE 1364 標準二. Verilog簡介三. 語法總結四. 編寫Verilog HDL源代碼的標準五. 設計流程

發表于 11-04 10:12

?2次下載

Lua語法基礎教程(下篇)

今天我們繼續學習Lua語法基礎教程,下篇。 九、函數 9.1 初識函數 函數是指一段在一起的、可以做某一件事兒的程序,也叫做子程序。 在前面的內容中,我們已經接觸過了函數的調用,這個函數就是前面用到

Lua語法基礎教程(中篇)

今天我們繼續學習Lua語法基礎教程,中篇。 五、變量 5.1 number變量 變量,可以看作是一個桶,在里面裝你想要裝的內容。這些內容可以是Lua包含的所有合法類型。 例如:我想要新建一個桶,名叫

Lua語法基礎教程(上篇)

今天我們來學習Lua語法基礎教程。由于篇幅過長,將分為上中下三篇進行講解,本篇為上篇。 一、初識Lua Lua 是一種輕量小巧的腳本語言,它用標準C語言編寫并以源代碼形式開放。這意味著什么呢?這

《DNK210使用指南 -CanMV版 V1.0》第七章 基于CanMV的MicroPython語法開發環境搭建

第七章 基于CanMV的MicroPython語法開發環境搭建 前面章節中已經介紹了如何編譯CanMV固件,并將編譯好的CanMV固件燒錄至Kendryte K210,本章將介紹如何在Windows

發表于 09-13 09:30

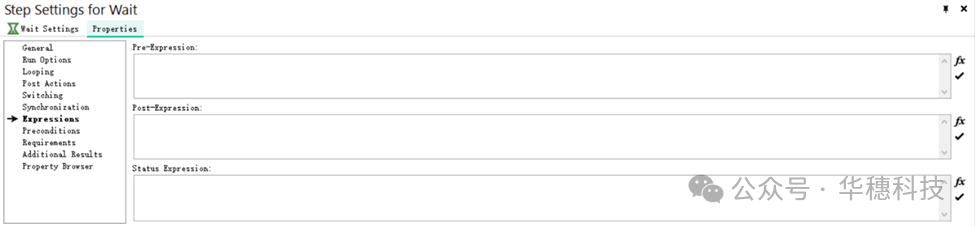

TestStand表達式中常用的語法規則和運算符使用

TestStand也有自己的語言嘛?在回答這個問題之前大家可以想一下在使用TestStand時有一個和語言密切相關的屬性。沒錯那就是表達式(Expressions),在這篇文章中,小編將以Q&A的方式來帶著大家來理解并熟悉TestStand表達式中較為常用的一些語法規則以及運算符使用。

鴻蒙原生應用元服務開發-初識倉頡開發語言

倉頡編程語言是一種面向全場景應用開發的通用編程語言,可以兼顧開發效率和運行性能,并提供良好的編程體驗,主要具有如下特點:

語法簡明高效 :倉頡編程語言提供了一系列簡明高效的語法,旨在減

發表于 08-15 10:00

鴻蒙原生應用元服務開發-初識倉頡開發語言

倉頡編程語言是一種面向全場景應用開發的通用編程語言,可以兼顧開發效率和運行性能,并提供良好的編程體驗,主要具有如下特點:

語法簡明高效 :倉頡編程語言提供了一系列簡明高效的語法,旨在減

發表于 07-30 17:49

HarmonyOS Next 原生應用開發-ArkTS語法適配背景說明

ArkTS在保持TypeScript(簡稱TS)基本語法風格的基礎上,進一步通過規范強化靜態檢查和分析,使得在程序開發期能檢測更多錯誤,提升程序穩定性,并實現更好的運行性能。本文將進一步解釋為

發表于 07-01 16:49

FPGA學習筆記---基本語法

Verilog語法是指硬件能夠實現的語法。它的子集很小。常用的RTL語法結構如下:

1、模塊聲明:module ... end module

2、端口聲明:input, output, inout

發表于 06-23 14:58

MarkDown簡明語法手冊

MarkDown簡明語法手冊

評論