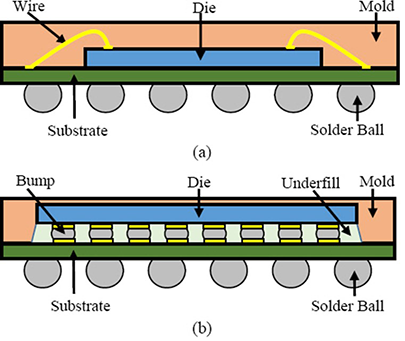

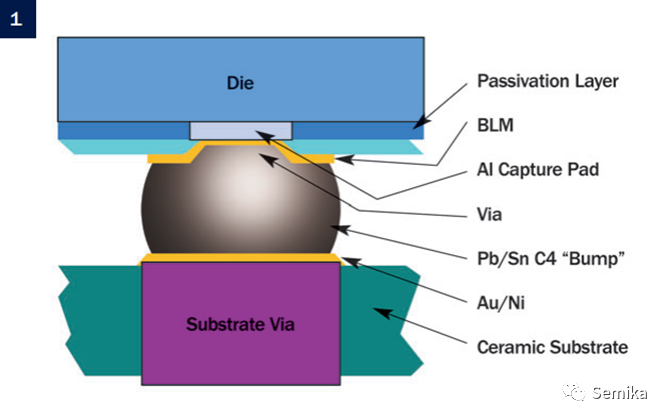

替代引線鍵合最常用、先進的互連技術是倒裝芯片技術稱為C4,即可控塌陷芯片連接(Controlled Collapse Chip Connection)或FC(Flip Chip,倒裝芯片)。這項技術是在20世紀60年代中期由IBM發明,每個引線具有最低的電感,為0.05~0.1nH(相比而言,線徑為25μm的引線電感約為1nH/m),因此具有最高的頻率響應以及最低的串擾和同步開關噪聲。

倒裝芯片還提供最高的Si芯片封裝密度,在密封的封裝體內,在陶瓷基板上Si芯片以接近125μm(5mil)高度緊密“疊放”在一起,對于需要環氧樹脂底部填充的層壓基板,倒裝芯片的間隔約為0.5mm(20mil)。通過焊料凸點可以將適量的熱量通過芯片的正面傳導至下面的封裝體,但是,非常高的熱量(在運算速率最快的器件中產生)必須從裸芯片的背面(面朝上)移除。盡管使用硅脂或聚合物的散熱連接已成為一種更便宜的選擇,但這可能需要精心制備的導熱片/棒和昂貴的封裝體,封裝體和I/O焊盤必須圍繞特定目的植球芯片進行設計,這意味著非常高的體積或高的成本。

最近,倒裝芯片已用于層壓基板(如PCB)上,其通過使用底部填充的聚合物糾正熱膨脹系數的失配(CTE)問題,雖然這些聚合物基板降低了封裝成本,但是可能進一步降低了散熱能力。為了進一步降低工藝成本,在現存的Al焊盤周邊,部分研究采用熱超聲球形鍵合技術(移除引線)在鍵合焊盤上形成凸點。同時,還使用了導熱聚合物或微球。

為了充分利用倒裝芯片技術的優勢,有必要對現有芯片重新設計面陣列I/O的倒裝芯片焊盤,但該焊盤在常規封裝中并不能進行有效的引線鍵合(盡管正在開發面陣列自動鍵合)。最初這種重新設計減慢了倒裝芯片技術的使用,盡管長期以來已有程序將外圍鍵合焊盤重新排版為面陣列的焊盤格式 2-711,與最初面陣列 I/O 的芯片設計相比,這些設計的熱傳遞效率(通過凸點)較低且串擾較大,因此這只是一個過渡階段。然而,由于小體積和高頻的需求,大量使用的便攜式終端,如移動電話的應用,已經克服了這個問題。當前,這些應用需要更高性能的芯片和更高的Si芯片密度(疊放),且目前更多的芯片設計成真實的面陣列、倒裝芯片格式。這種互連方法的增長速度比引線鍵合快,并且猜測最終(許多年)可能會取代它們,成為許多產品應用的首選互連方法。給大家介紹完半導體集成電路焊球倒裝是什么,下面__【科準測控】__小編接著給大家介紹倒裝芯片剪切力試驗怎么做?

一、倒裝芯片剪切力測試

1、 試驗目的

本試驗的目的是測試底部填充前芯片與基板之間的剪切強度,或測量底部填充后對芯片所加力的大小,觀察在該力下產生的失效類型,判定器件是否接收。

- 測試設備要求

測試設備應使用校準的負載單元或傳感器,設備的最大負載能力應足以把芯片從固定位置上分離或大于規定的最小剪切力的2倍。設備準確度應達到滿刻度的±5%。設備應能提供并記錄施加于芯片的剪切力,也應能對負載提供規定的移動速率。

3、試驗設備(以科準Alpha-W260推拉力測試機為例)

4、 試驗程序

4.1 安裝

在試驗設備上安裝剪切工具和試驗樣品,剪切工具正好在位于基板之上的位置與芯片接觸,在垂直于芯片或基板的一個邊界并平行于基板的方向上施加外力,使芯片可以被平行于器件表面的剪切工具剪切,如圖8所示。應小心安放器件以免對芯片造成損傷。對于某些類型的封裝,由于封裝結構會妨礙芯片的剪切力測試,當規定要采用本試驗方法時,需要采用有效的化學或物理方法將妨礙部分去除,但不得破壞芯片倒裝區和填充區。

剪切力和失效模式受剪切速度、剪切高度以及器件存儲時間的影響。為保證試驗結果的有效性,應對任何檢驗批進行相同條件的剪切試驗,如剪切速度、剪切高度等都應一致。

夾具應防止器件在軸向上移動,保證剪切方向與基板的表面平行,并且不損傷芯片,不使基板變形。圖9給出了夾具的示例,可使用其他工具替代夾具。

夾具應和機器保持剛性連接,移動和變形應最小化,避免對器件產生諧振激勵。對長方形芯片,應從與芯片長邊垂直的方向施加應力。

剪切工具應由堅硬的剛性材料、陶瓷或其他非易彎曲的材料構成。剪切工具應和器件底面成90°士5°。把剪切工具和芯片對齊,使其可以接觸芯片的一側。應保證剪切工具在行進時不會接觸基板。

最好能使用可移動的試驗臺和工具臺進行對齊,并使移動平面垂直于負載方向。

由于頻繁使用會造成剪切工具磨損,從而影響試驗結果。如果剪切工具有明顯的磨損,如圖7所示,則應替換。

4.2 芯片剪切

4.2.1 剪切速度

芯片剪切過程中應保持恒定速率,并記錄剪切速度。剪切速度一般為0.1 mm/s~0.8 mm/s。

4.2.2 剪切力

試驗數據應包括芯片剪切力數值和標準要求數值。芯片剪切力數值應滿足應用條件所要求的最小值。

5、 失效判據

5.1 倒裝芯片剪切強度(無底填充器件)

使倒裝芯片和基板產生分離的最小剪切力應按式(1)計算,小于其值而發生分離則視為不合格。

最小剪切力=0.05N×凸點數 (1)

當有規定時,應記錄造成分離時的剪切力數值,以及分離或失效的主要類別:

a) 焊點材料或基板焊接區(適用時)的失效;

b) 芯片或基板的破裂(緊靠在焊點處下面的芯片或基板失掉一部分);

c) 金屬化層浮起(金屬化層或基板焊接區與芯片或基板分離)。

5.2 倒裝芯片剪切強度(底填充器件)

若芯片黏接面積大于4.13 mm2,應最小承受25 N的力或其倍數;若芯片黏接面積大于或等于0.32mm2,但不大于4.13 mm2時,芯片承受的最小應力可通過圖11確定;若芯片黏接面積小于0.32mm2,應承受的最小力為(0.1倍)時的6N/mm2或(2倍)時的12N/mm2。

符合以下任一判據則應視為失效:

a) 小于圖10中曲線所表示的最小芯片剪切強度要求。

b) 適用時,使芯片與基板脫離時施加的力小于圖10中最小芯片剪切強度的1.25倍,同時芯片在填充材料上的殘留小于填充區面積的50%。

c) 適用時,使芯片與基板脫離時施加的力小于圖10中最小芯片剪切強度的2.0倍,同時芯片在填充材料上的殘留小于填充區面積的10%。

當有規定時,應記錄造成分離時的剪切力數值,以及分離或失效的主要類別:

- 芯片被剪切掉后,基板上殘留有芯片的碎片;

b) 芯片與填充材料間脫離;

c) 芯片與填充材料一起脫離基板。

6、 說明

有關采購文件或詳細規范中應規定以下內容:

a) 最小剪切力強度(若不用本試驗判據時);

b) 試驗的芯片數和接收數;

c) 數據記錄要求。

以上就是小編對半導體集成電路焊球倒裝是什么?以及倒裝芯片剪切力試驗目的、測試設備、試驗方法以及失效判據的介紹了,希望能給大家帶來幫助!科準專注于推拉力測試機研發、生產、銷售。廣泛用于與LED封裝測試、IC半導體封裝測試、TO封裝測試、IGBT功率模塊封裝測試、光電子元器件封裝測試、大尺寸PCB測試、MINI面板測試、大尺寸樣品測試、汽車領域、航天航空領域、軍工產品測試、研究機構的測試及各類院校的測試研究等應用。如果您有遇到任何有關推拉力機、半導體集成電路等問題,歡迎給我們私信或留言,科準的技術團隊也會為您免費解答!

審核編輯 hhy

-

芯片

+關注

關注

456文章

50889瀏覽量

424237 -

集成電路

+關注

關注

5388文章

11562瀏覽量

362017

發布評論請先 登錄

相關推薦

倒裝封裝(Flip Chip)工藝:半導體封裝的璀璨明星!

芯片倒裝與線鍵合相比有哪些優勢

芯片熱管理,倒裝芯片封裝“難”在哪?

剪切力測試儀用設備安全裝置及技術指標,夾具選擇

淺談FCCSP倒裝芯片封裝工藝

半導體集成電路|什么是倒裝芯片?倒裝芯片剪切力測試怎么做?

半導體集成電路|什么是倒裝芯片?倒裝芯片剪切力測試怎么做?

評論