據Ameya360電子元器件采購網報導:防靜電和浪涌TVS layout設計要點

電子產品精密化

剛看過了CES2023,雷卯的外貿伙伴們看了新的AR,VR,5G產品,新的電子產品更智能、更復雜,嵌入了脆弱和敏感的集成電路。這些設備的環境往往很惡劣,產生高水平靜電和快速瞬態浪涌。這些ESD事件可能會干擾設備,從故障到集成電路的破壞。

將這些問題的好方法是從PCB入口放置瞬態電壓抑制器(TVS),放置在可能出現浪涌的地方;但在選擇這些組件PCB布局必須小心,以確保很好的保護。

電磁兼容可靠性要求

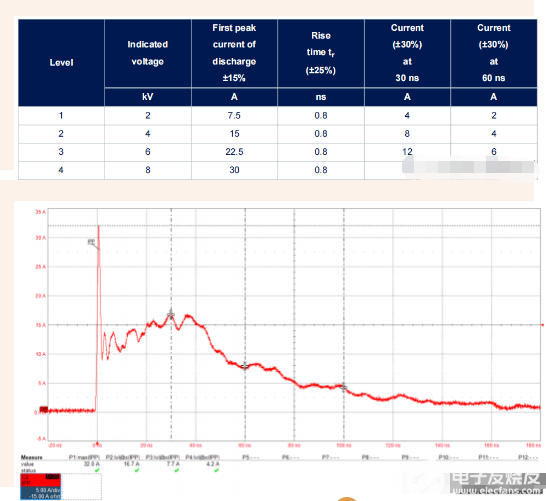

很明顯,敏感部件可能會出現靜電損壞風險。國際電工委員會IEC委員會定義了標準,該標準定義了四種嚴重等級,對應于四種電壓等級,有兩種放電、接觸和空氣類型。對接觸放電的類別與電壓水平和電流波形的定義顯示了對接觸放電的這些類別的定義以及與不同電壓水平的波形的定義。

下表是IEC61000-4-2規定的接觸靜電放電的波形4級測試要求,附帶測試標準波形的具體時間和電壓圖。

線路中TVS設置

大家都知道要在接口處設置TVS保護器件,但有時候達不到理想的測試效果,這里要分析一下原因:

1 TVS型號選型不當

2 PCB設計不合理,導致TVS保護效果不佳

這里主要討論在PCB上怎么合理設計讓TVS發揮優異的保護功效。

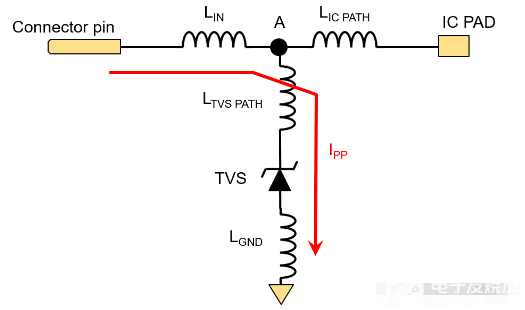

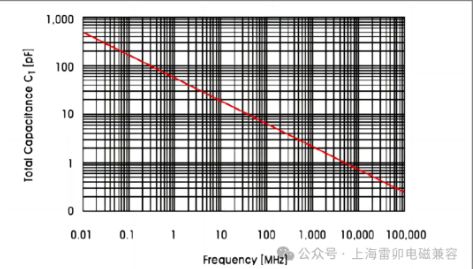

這里就要考慮線路上的各種寄生電感,包括TVS管腳自身的寄生感值。這會影響靜電或浪涌發生時后端IC處的箝位電壓Vc值。

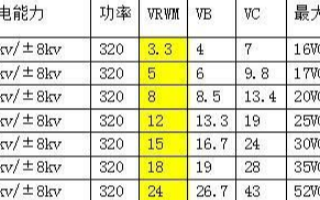

TVS本身遵從以下公式

VCL = VBR + RD × IPP

R為TVS本身的寄生電容值,越小的產品他的箝位電壓會更好,更有效保護IC,IPP是測試瞬間通過TVS本身的電流值。

在測試圖中,A點的電壓并不是Vc值,Va電壓需要加上TVS 兩端的電壓。

LIN和LIC由PATH通常由線路的控制阻抗(例如50Ω或100 Ω差分)驅動。為了迫使浪涌電流通過保護電路,我們必須確保LGND和LTVS路徑盡可能低。此外,為了減少PCB上的輻射,好的方法是將保護電路盡可能靠近連接器針腳。

總結

以上我們看到,為了限制各種寄生電路的布局,必須注意產生的過電壓和電磁干擾。注意接地連接和將TVS放置在正確的方式上,保證一個成功的電路,以確保設備的高可靠性水平的關鍵。綜上所述,以下要點:確保保護裝置連接到地面盡可能短,盡量減少寄生電感路徑從靜電電源到保護組件,然后從保護組件到芯片保護(而不是從靜電電源到芯片保護,然后保護連接到該路徑)。這也是一種避免寄生電感,將保護組件盡可能接近ESD源:這將PCB上的EMI,與其他路徑耦合化PCB上的EMI,與其他路徑耦合。

審核編輯:湯梓紅

-

TVS

+關注

關注

8文章

797瀏覽量

60714 -

Layout

+關注

關注

14文章

406瀏覽量

61903 -

浪涌

+關注

關注

3文章

259瀏覽量

28564 -

防靜電

+關注

關注

3文章

152瀏覽量

13035 -

雷卯電子

+關注

關注

0文章

55瀏覽量

129

發布評論請先 登錄

相關推薦

Ameya360數字溫度計解決方案概述

汽車電子瞬態浪涌保護用TVS如何選型? ?

5G!AMEYA360簽約芯訊通授權代理商

防靜電ESD功率可以更大了

AMEYA360:位移傳感器安裝要點及使用注意事項

雷卯推薦萬兆、千兆、百兆網口防靜電ESD

AMEYA360:上海雷卯電子推出小封裝高壓防靜電二極管SD60C

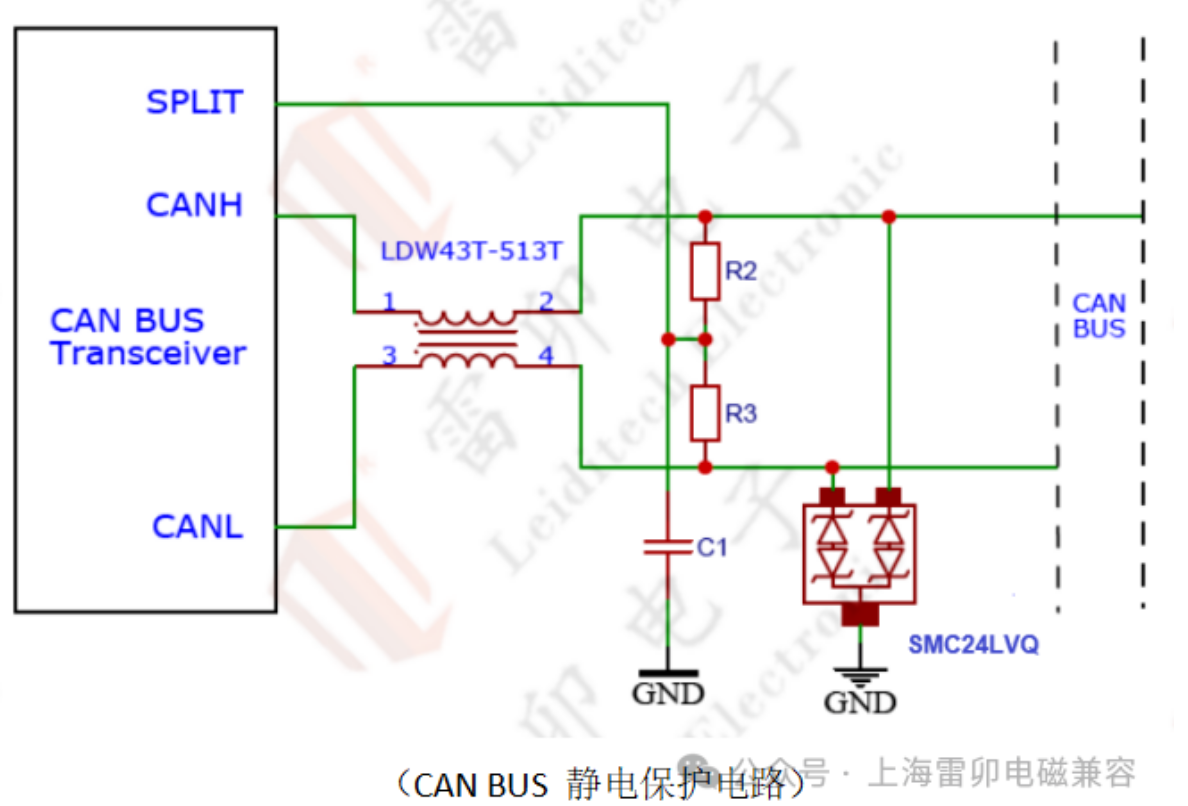

AMEYA360:上海雷卯電子CAN BUS芯片靜電浪涌擊穿整改方案

Ameya360雷卯電子:防靜電和浪涌TVS layout設計要點

Ameya360雷卯電子:防靜電和浪涌TVS layout設計要點

評論