隨著電子產品的集成度越來越高,PCB板的尺寸越來越小,板級芯片散熱的問題越來越成為電子工程師的一個重要挑戰。 對于板級芯片散熱,主要依靠工程師對 PCB自身的設計進行優化 ,同時要兼顧系統的尺寸和成本。 本文分別從芯片角度和PCB角度進行建模,芯片模型選用QFN封裝,PCB模型采用走線導入模型,探討了芯片結構,PCB銅厚,PCB疊層厚度對芯片散熱的影響。

2、建模過程

為了最大程度的還原仿真對象,PCB模型采用Icepak自帶PCB模型,通過導入真實的走線Trace真實模擬PCB的散熱能力。 芯片也是采用Icepak自帶的Package模型 對QFN封裝進行詳細建模。

2.1 PCB 板建模

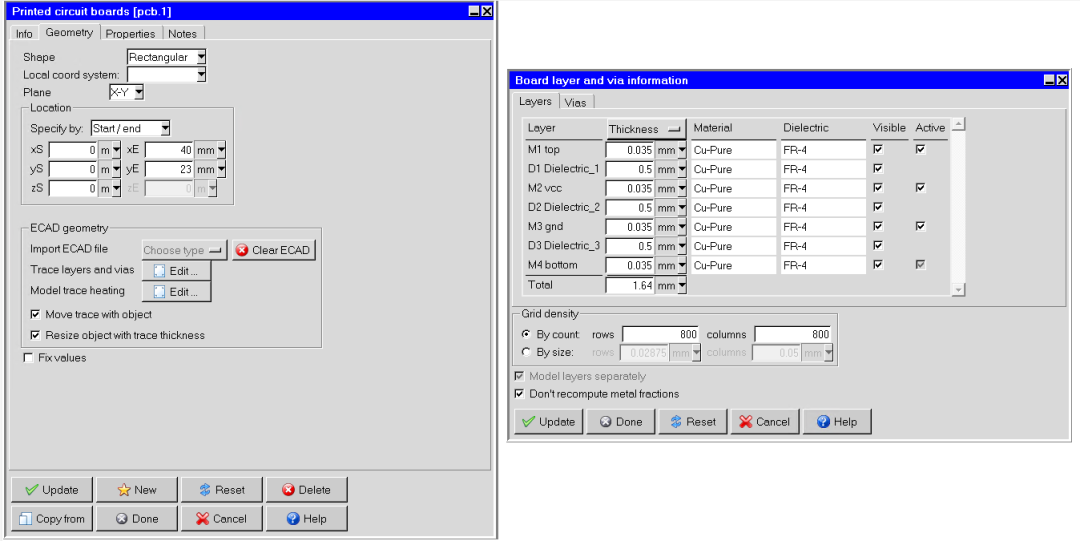

通過ODB模型導入PCB 走線信息,并編輯PCB的疊層及銅厚:

設置板子尺寸為23X40mm

PCB銅厚為1oz(0.035mm)

PCB總疊層厚度為1.64mm

不考慮走線電流發熱影響( 可通過SIwave導入,關注我后續帶你分析! )

圖2.1 PCB 參數和走線導入設置

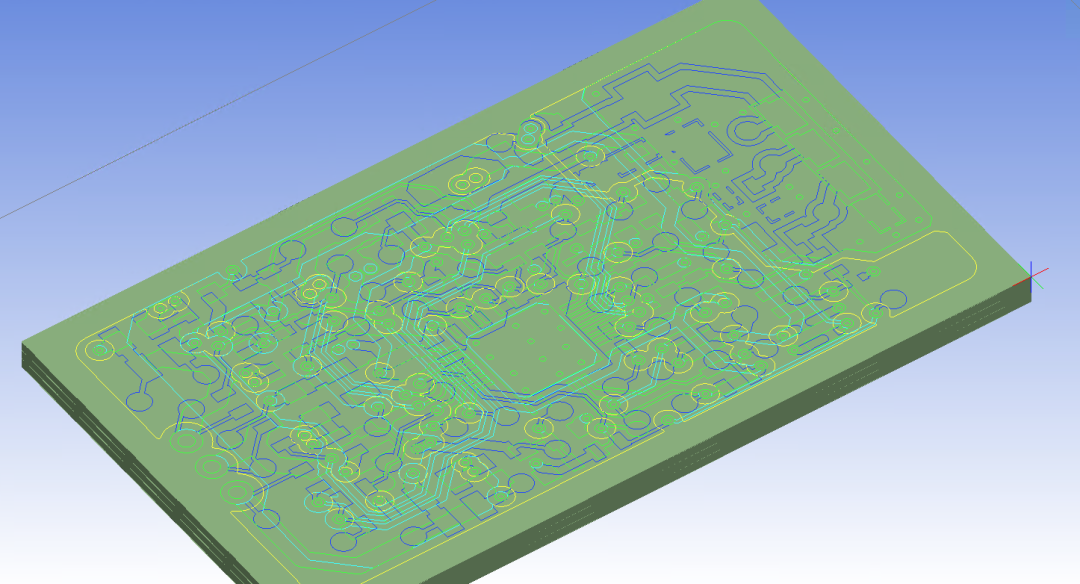

圖2.2 PCB 導入走線后視圖

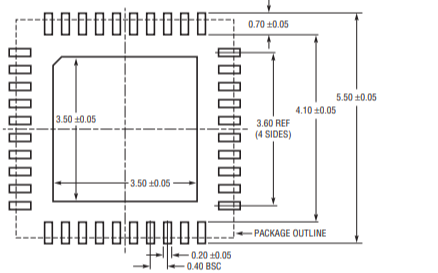

2.2 QFN 芯片封裝建模

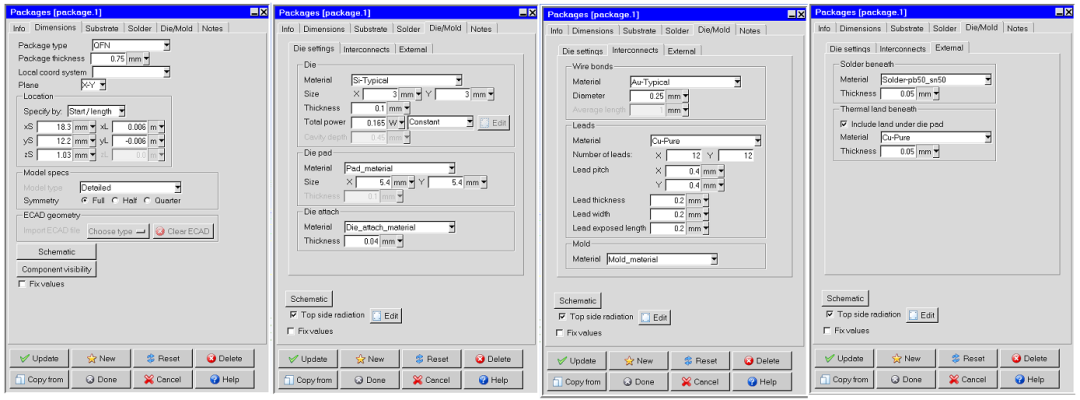

根據數據手冊尺寸設置QFN 芯片尺寸:

芯片外尺寸6x6x0.75mm

芯片Die尺寸3x3mm

散熱盤尺寸5.4x5.4mm

芯片損耗為0.165w

其他按照規格書設置

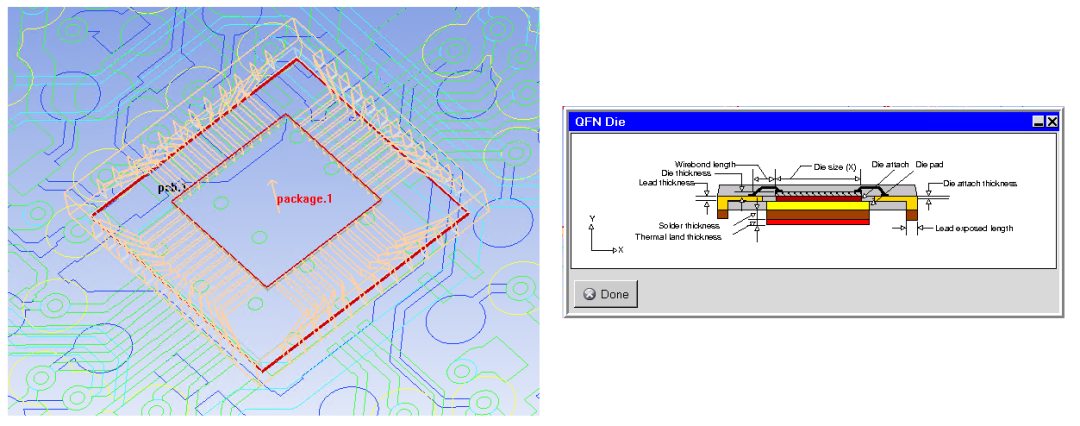

圖2.3 QFN 芯片封裝設置

圖2.4 QFN 芯片參數說明

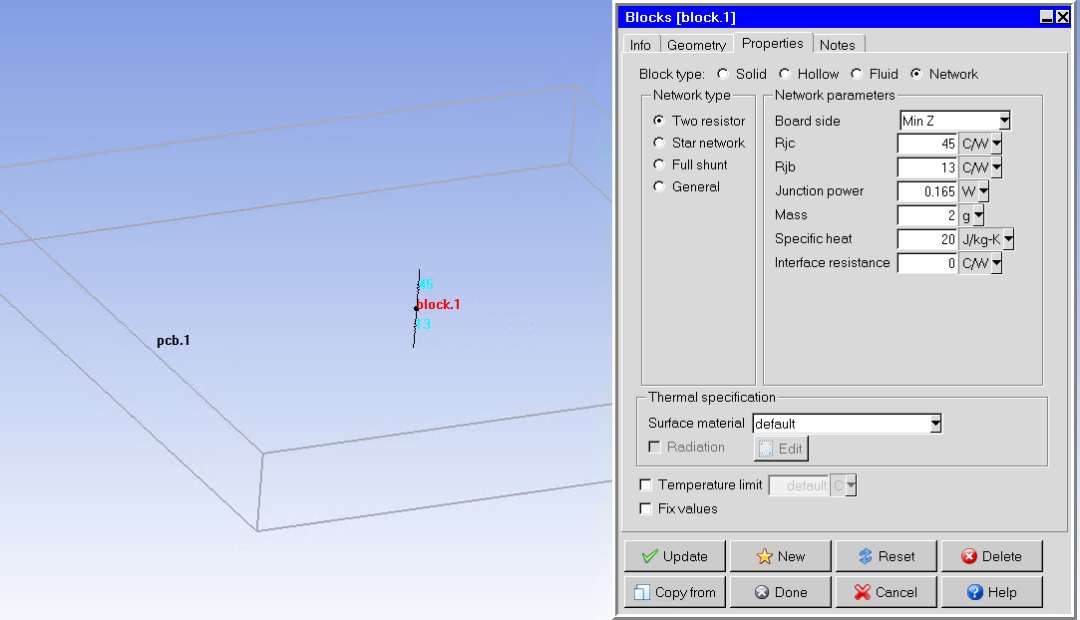

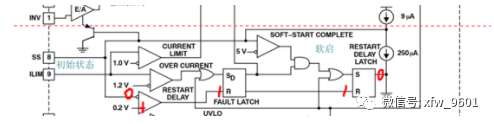

2.3 基于熱阻模型的芯片建模

使用QFN的熱阻參數,建立二維熱阻模型:

MinZ 為緊貼PCB的面(Bottom)

Rjc為 Junction-Case 熱阻

Rjb為 Junction-Bottom 熱阻,為主要傳熱路徑

芯片損耗為0.165w

圖2.5 QFN的二維熱阻模型

3、仿真結果

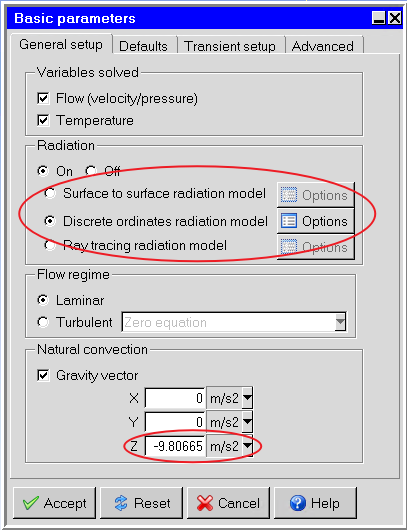

靜態PCB散熱主要形式為 自然對流和輻射散熱 ,通過重力模擬,和DO輻射模型對PCB進行仿真,參數設置如下:

圖3.1 仿真參數設置

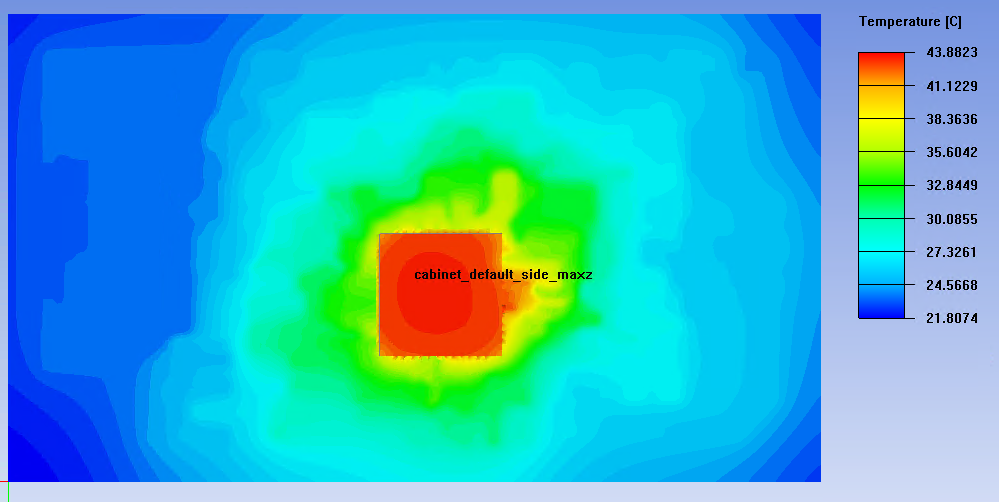

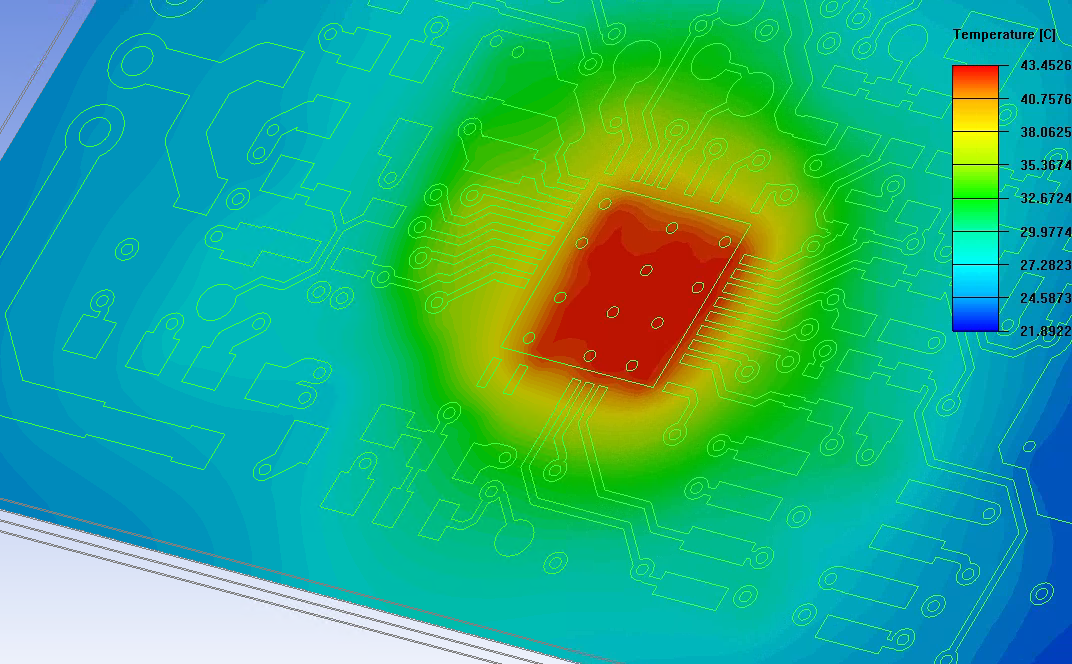

通過芯片和PCB的詳細建模,可以獲得散熱模型的各種散熱細節的仿真結果:

圖3.2 PCB 表面散熱云圖

圖3.3 PCB 內層散熱云圖

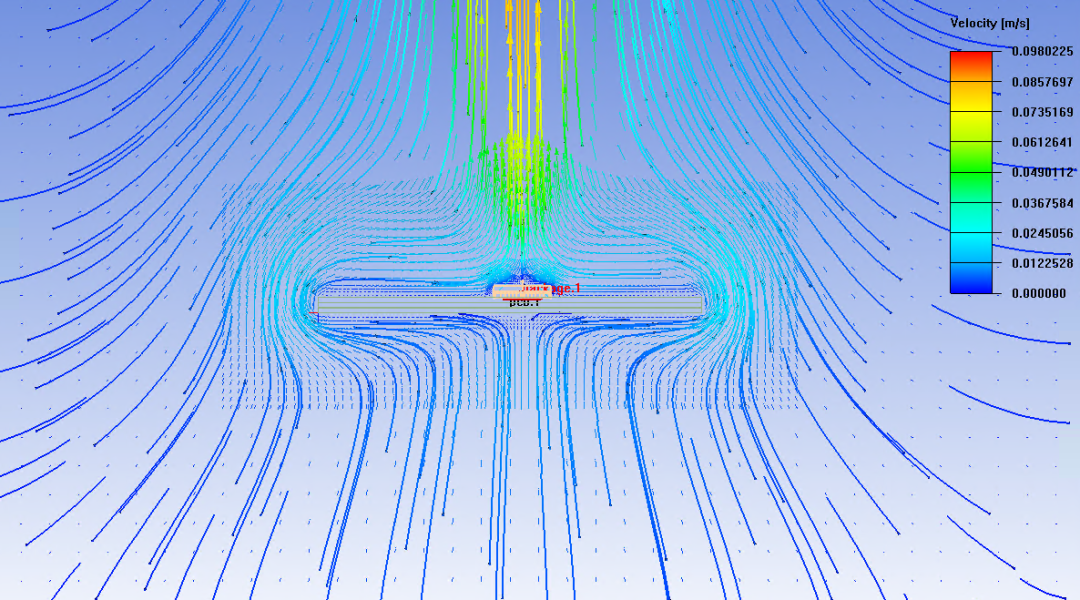

圖3.4 PCB 周邊自然對流情況

對仿真結果進行處理和分析:

| 仿真序號 | 仿真條件 | 仿真溫度 | 溫升 |

|---|---|---|---|

| --------------------------------------------------------------------------------- | |||

| 1,102 | 20C,Pdis=0.165W,真實QFN模型; 銅厚1oz,疊層絕緣層0.5mm | 56.8攝氏度 | 36.8攝氏度 |

| - | - | - | - |

| 2,104 | 20C,Pdis=0.165W, 熱阻QFN模型 ; 銅厚1oz,疊層絕緣層0.5mm | 59.3攝氏度 | 39.3攝氏度 |

| 3,105 | 20C,Pdis=0.165W,真實QFN模型; 銅厚2oz ,疊層絕緣層0.5mm | 43.9攝氏度 | 23.9攝氏度 |

| 4,106 | 20C,Pdis=0.165W,真實QFN模型; 銅厚2oz ,疊層絕緣層0.25mm | 36.2攝氏度 | 16.2攝氏度 |

| 5,107 | 20C,Pdis=0.165W,真實QFN模型; 銅厚1oz,疊層絕緣層0.5mm,PCB倒立放置 | 57.0攝氏度 | 37.0攝氏度 |

| 6,108 | 20C,Pdis=0.165W,真實QFN模型; 銅厚1oz,疊層絕緣層0.5mm,側面0.1m/s風冷 | 54.7攝氏度 | 34.7攝氏度 |

由上述仿真結果看出:

真實的QFN模型和熱阻模型溫度偏差不大,通過使用熱阻模型可以簡化建模過程

增加PCB 銅厚可以大幅度降低芯片溫度,但是成本增加

減少PCB 疊層厚度能夠降低芯片溫度,成本幾乎不變

PCB的擺放角度對芯片溫度有一定影響,但是影響有限

微弱的空氣對流,對芯片溫度影響不大

小結

本文通過對PCB和QFN芯片建模,模擬的多種工況條件下的芯片散熱,其中影響PCB散熱最直接的因素為 PCB疊層厚度和走線銅厚 !

-

芯片

+關注

關注

456文章

50873瀏覽量

424074 -

封裝

+關注

關注

126文章

7924瀏覽量

143028 -

建模

+關注

關注

1文章

307瀏覽量

60778 -

qfn

+關注

關注

3文章

190瀏覽量

56200 -

PCB

+關注

關注

1文章

1809瀏覽量

13204

發布評論請先 登錄

相關推薦

QFN封裝的組裝和PCB布局指南

求各位高手相助 關于PCB設計中QFN封裝芯片的問題

什么是小間距QFN封裝PCB設計串擾抑制?

大家焊接QFN芯片有什么妙招嗎?

基于PSO和SVM的發酵過程建模與優化控制

軟件過程建模方法研究

如何在 QFN 封裝芯片的 PCB 設計上得到盡可能好的串擾性能(中文講解視頻 + PPT下載)

過程系統建模與仿真.pdf

QFN封裝是什么?有什么特點?

技術資訊 | 通過倒裝芯片 QFN 封裝改善散熱

PCB和QFN芯片建模過程

PCB和QFN芯片建模過程

評論