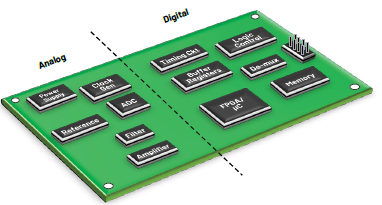

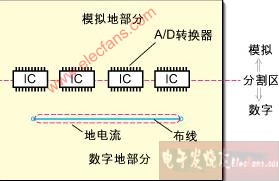

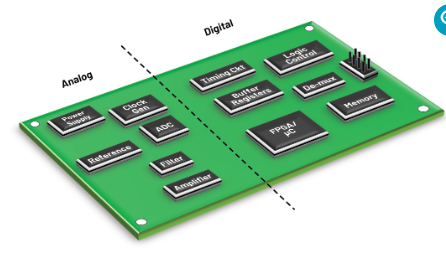

本應用筆記提供了RF印刷電路板(PCB)設計和布局的指南和建議,包括對混合信號應用的一些討論,例如同一PCB上的數字、模擬和RF元件。該材料按主題領域排列,并提供“最佳實踐”指導。它應與可能適用于特定組件的所有其他設計和制造指南結合使用, PCB 制造商, 和材料組(如適用)。

射頻傳輸線

ADI公司的許多RF元件都需要受控阻抗傳輸線,該傳輸線將RF功率傳輸到PCB上的IC引腳(或從PCB引腳傳輸)。這些傳輸線可以在外層(頂部或底部)上實現,也可以埋在內層中。這些傳輸線的指南包括與微帶、懸掛帶狀線、共面波導(接地)和特性阻抗相關的討論。它還描述了傳輸線彎曲和拐角補償,以及傳輸線的層變化。

微帶

這種類型的傳輸線由固定寬度的金屬布線(導體)以及位于正下方(相鄰層)的堅固不間斷接地層組成。例如,第 1 層(頂部金屬)上的微帶需要第 2 層上的實心接地層(圖 1)。布線寬度、介電層厚度和電介質類型決定了特性阻抗(通常為50Ω或75Ω)。

圖1.微帶示例(等軸測視圖)。

懸掛帶狀線

該線路由內層上的固定寬度布線組成,中心導體上方和下方具有實心接地層。導體可以位于接地層之間的中間(圖 2),也可以偏移(圖 3)。這是在內層上進行射頻路由的適當方法。

圖2.懸掛帶狀線(端視圖)。

圖3.偏移懸掛帶狀線。帶狀線的一種變體,用于層厚度不等的 PCB(端視圖)。

共面波導(接地)

共面波導可在附近的RF線以及其他信號線(端視圖)之間提供更好的隔離。該介質由中心導體組成,其兩側和下方都有接地層(圖 4)。

圖4.共面波導可在附近的RF線和其他信號線之間提供更好的隔離。

建議在共面波導的兩側設置過孔“圍欄”,如圖5所示。此頂視圖提供了中心導體兩側每個頂部金屬平面上的一排接地過孔的示例。頂層感應的返回電流短路至底層接地層。

圖5.建議在共面波導的兩側使用過孔圍欄。

特性阻抗

有幾種計算器可用于正確設置信號導體線寬以實現目標阻抗。但是,在輸入層的介電常數時應小心。典型PCB的外層壓層通常比電路板的芯含有更少的玻璃含量, 因此介電常數較低.例如,FR4 核心通常作為εR= 4.2,而外層壓板(預浸料)層通常εR= 3.8。下面給出的示例僅供參考,假設金屬厚度為1盎司銅(1.4密耳,0.036毫米)。

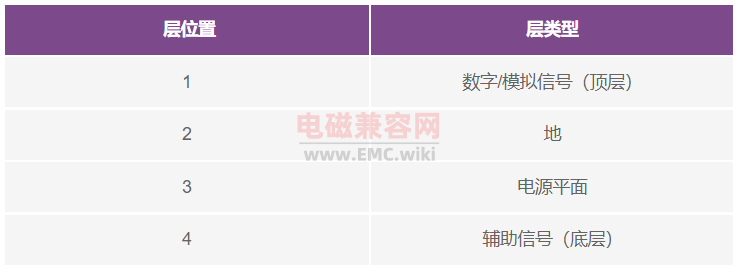

| 媒體 | 電介質 | 層厚(密耳) | 中心導體,單位為密耳(毫米) | 差距 | 特性阻抗 |

| 微帶 | 預浸料 (3.8) | 6 (0.152) | 11.5 (0.292) | 不適用 | 50.3 |

| 10 (0.254) | 20 (0.508) | 50.0 | |||

| 差分對 | 預浸料 (3.8) | 6 (0.152) | 25 (0.635) | 6 (0.152) | 50.6 |

| 帶狀線 | FR4 (4.5) | 12 (0.305) | 3.7 (0.094) | 不適用 | 50.0 |

| 偏移帶狀線 |

預浸料 (3.9) |

6 (0.152) 上, |

4.8 (0.122) |

不適用 |

50.1 |

| 低 10 (0.254) | |||||

| 共面工作組 |

預浸料 (3.8) |

6 (0.152) | 14 (0.35) | 20 (0.50) | 49.7 |

傳輸線彎曲和拐角補償

當傳輸線由于布線約束而需要彎曲(改變方向)時,請使用至少為中心導體寬度 3 倍的彎曲半徑。換句話說:

彎曲半徑≥ 3 ×(線寬)。

這將最大限度地減少通過彎曲的任何特性阻抗變化。

在無法逐漸彎曲的情況下,傳輸線可以進行直角彎曲(非彎曲)。參見圖 6。但是,必須對此進行補償,以減少由于通過彎曲的有效線寬的局部增加而導致的阻抗不連續性。標準補償方法是斜接,如下圖所示。最佳微帶直角斜接由杜維爾和詹姆斯的公式給出:

其中 M 是斜接與未斜接折彎相比的分數 (%)。該公式與介電常數無關,并且受w/h≥0.25的約束。

其他傳輸線也可以采用類似的方法。如果正確補償存在任何不確定性,如果設計需要高性能傳輸線,則應使用電磁模擬器對彎曲進行建模。

圖6.當無法彎曲時,傳輸線可以進行直角彎曲。

傳輸線的層更改

當布局限制要求傳輸線移動到不同的層時,建議每個過渡至少使用兩個通孔,以最小化過孔電感負載。一對過孔將有效降低50%的過渡電感,并且應使用與傳輸線寬度兼容的最大通孔直徑。例如,在 15 密耳微帶生產線上,將使用 15 密耳至 18 密耳的通孔直徑(成品電鍍直徑)。如果空間不允許使用較大的過孔,則應使用三個直徑較小的過渡過孔。

信號線隔離

必須注意防止信號線之間的意外耦合。一些潛在的耦合和預防措施的例子:

射頻傳輸線:線路應盡可能保持距離,并且不應在近距離布線以延長距離。平行微帶線之間的耦合將隨著間距的減小和平行布線距離的增加而增加。在單獨層上交叉的線應具有使它們分開的接地平面。承載高功率水平的信號線應盡可能遠離所有其他線路。接地共面波導可在線路之間提供出色的隔離。在小型PCB上實現優于約-45dB的RF線路之間的隔離是不切實際的。

高速數字信號線:這些線應分別布線在與RF信號線不同的層上,以防止耦合。數字噪聲(來自時鐘、PLL等)可以耦合到RF信號線上,并且可以調制到RF載波上。或者,在某些情況下,數字噪聲可以上/下變頻。

V抄送/電源線:這些應在專用層上布線。應在主V處提供足夠的去耦/旁路電容抄送分布節點,以及 V 處抄送分支。旁路電容的選擇必須基于RF IC的整體頻率響應,以及時鐘和PLL的任何數字噪聲的預期頻率分布特性。這些線路還應與任何將傳輸大量RF功率的RF線路分開。

地面平面

建議的做法是在第 2 層使用實心(連續)接地層,假設第 1 層用于射頻組件和傳輸線。對于帶狀線和偏移帶狀線,需要在中心導體上方和下方的接地層。這些平面不得共享或分配給信號或電源網絡,但必須唯一地分配給地面。層上的部分接地層(有時由于設計約束而需要)必須位于所有RF組件和傳輸線的基礎。接地層不得在傳輸線布線下斷開。

層之間的接地通孔應在整個PCB的RF部分自由添加。這有助于防止由于接地電流返回路徑而產生寄生接地電感。過孔還有助于防止來自PCB上的RF和其他信號線的交叉耦合。

偏置和地層的特殊考慮

分配給系統偏置(直流電源)和接地的層必須根據元件的返回電流來考慮。一般的指導是不要在偏置層和接地層之間的層上路由信號。

圖7.層分配不正確:偏置層和接地層上的接地電流返回路徑之間存在信號層。偏置線噪聲可以耦合到信號層。

圖8.更好的層分配:偏置層和接地返回層之間沒有信號層。

電源(偏置)路由和電源去耦

一種常見的做法是,如果一個組件有多個電源連接,則對電源路由使用“星形”配置(圖 9)。較大的去耦電容(數十μFds)安裝在星形的“根部”,較小的電容安裝在每個星形分支上。后一種電容器的值取決于RF IC的工作頻率范圍及其特定功能(即級間與主電源去耦)。下面顯示了一個示例。

圖9.如果一個組件有多個電源連接,則電源路徑可以按星形配置排列。

“星形”配置避免了長接地返回路徑,如果連接到同一偏置網絡的所有引腳都串聯,則會導致長接地返回路徑。較長的接地返回路徑會產生寄生電感,從而導致意外的反饋環路。電源去耦的關鍵考慮因素是,直流電源連接必須電氣定義為交流接地。

去耦或旁路電容器的選擇

實際電容器由于其自諧振頻率(SRF)而具有有限的有效頻率范圍。SRF 可從制造商處獲得,但有時必須通過直接測量來表征。在SRF上方,電容是電感性的,因此不會執行去耦或旁路功能。當需要寬帶去耦時,標準做法是使用幾個尺寸(電容)不斷增加的電容器,所有電容器都并聯連接。較小值的電容器通常具有較高的SRF(例如,SRF = 14GHz的0402 SMT封裝中的0.2pF值),而較大的值具有較低的SRF(例如,SRF = 4GHz的同一封裝中的2pF值)。典型排列如表2所示。

| 元件 | 電容 | 包 | 戰略成果框架 | 有效頻率范圍* |

| 超高范圍 | 20pF | 0402 | 2.5千兆赫 | 800兆赫至 2.5兆赫 |

| 非常高的范圍 | 100pF | 0402 | 800兆赫 | 250兆赫至800兆赫 |

| 高范圍 | 1000pF | 0402 | 250兆赫 | 50兆赫至 250兆赫 |

| 中檔 | 1μF | 0402 | 60兆赫 | 100kHz 至 60MHz |

| 低范圍 | 10μF | 0603 | 600千赫 | 10kHz 至 600kHz |

| *有用頻率范圍的低端定義為小于5Ω的容抗。 | ||||

旁路電容布局注意事項

由于電源線必須為交流接地,因此必須盡量減少添加到交流接地返回路徑的寄生電感。這些寄生電感可能是由布局或元件方向選擇引起的,例如去耦電容接地的方向。有兩種基本方法,如圖 10 和圖 11 所示。

圖 10.這種配置是旁路電容和相關過孔的最小總占位面積。

在這種配置中,連接V的過孔抄送頂層到內部電源層(層)的焊盤可能會阻礙交流接地電流返回,迫使返回路徑更長,從而產生更高的寄生電感。流入 V 的任何交流電流抄送引腳穿過旁路電容到達其接地側,然后返回內部接地層。這種配置是旁路電容和相關過孔的最小總占位面積。

圖 11.這種配置需要更多的PCB面積。

在這種替代配置中,電源層過孔不會阻擋交流接地返回路徑。通常,這種配置需要更多的PCB面積。

并聯組件的接地

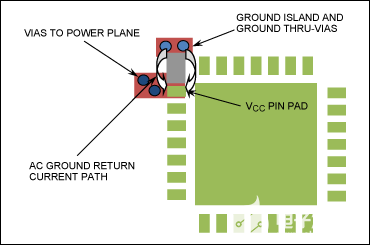

對于并聯(接地)元件(如電源去耦電容器),建議的做法是每個元件至少使用兩個接地過孔(圖 12)。這降低了過孔寄生電感的影響。通孔接地“孤島”可用于分流連接的組件組。

圖 12.為每個元件使用至少兩個接地過孔可降低過孔寄生電感的影響。

IC 接地層(“焊盤”)

大多數IC要求元件正下方的元件層(PCB的頂部或底部)具有堅實的接地層。該接地層將通過PCB將直流和RF返回電流傳輸到指定的接地層。該元件“接地焊盤”的次要功能是提供散熱片,因此焊盤應包括PCB設計規則允許的最大直通孔數。下面的示例顯示了嵌入在 RFIC 正下方中央接地層(組件層上)中的 5 × 5 通孔陣列(圖 13)。應使用其他布局考慮因素可以容納的最大過孔數。這些過孔是理想的直通孔(即,一直穿透PCB),并且必須電鍍。如果可能,過孔應填充導熱漿料以增強散熱器(焊膏在通孔電鍍后和最終電路板電鍍之前涂覆)。

圖 13.嵌入在RF IC正下方中央接地層中的5×5通孔陣列。

審核編輯:郭婷

-

pcb

+關注

關注

4319文章

23099瀏覽量

397889 -

射頻

+關注

關注

104文章

5585瀏覽量

167745 -

RFIC

+關注

關注

1文章

60瀏覽量

24474

發布評論請先 登錄

相關推薦

RF和混合信號PCB布局最佳指南(專家應用筆記)

混合信號PCB布局設計的基本準則

射頻和混合信號的PCB布局指南

射頻和混合信號的PCB布局指南

評論