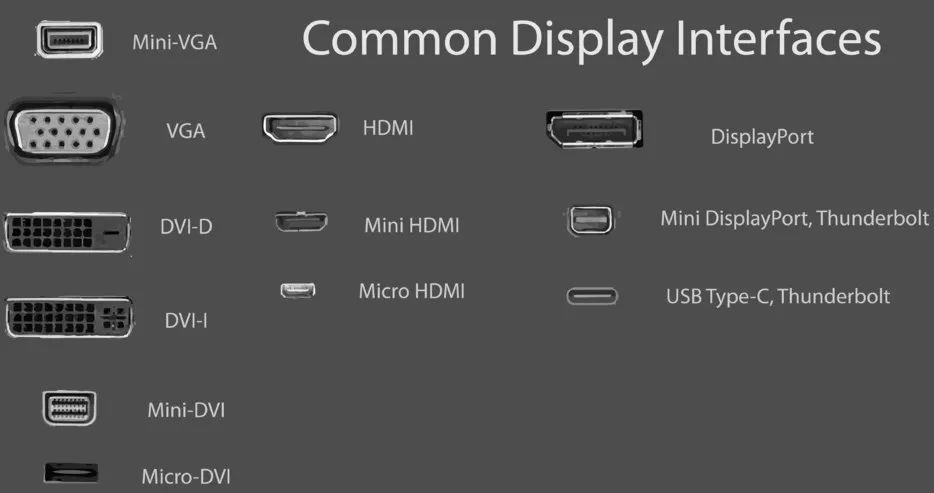

視頻圖像經過數十年的發展,已形成了一系列的規范,以VGA和HDMI為主的視頻圖像接口協議也得到定義與推廣。盡管DP、DVI、Type-C等圖像接口技術近年來得到了推廣與應用,且VGA傳輸性能發展逐漸落后于時代,但作為顯示器和顯卡等設備的通用顯示接口,VGA和HDMI仍是當前主流的視頻圖像接口技術。

? ?

? ?

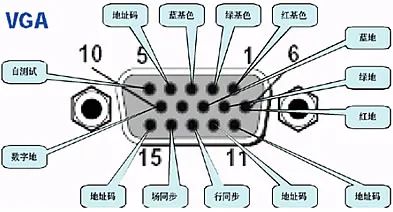

1.1 VGA視頻接口

視頻圖形陣列(VGA,Video Graphics Array),也可稱作D-Sub,是IBM于1987年提出的一個使用模擬信號的電腦顯示標準,因此VGA傳輸信號為模擬信號,并且只能傳輸視頻信號,不能傳輸音頻信號。

VGA接口共有15針,分成3排,每排5個孔,是顯卡上應用最為廣泛的接口類型,絕大多數顯卡都帶有此種接口。它傳輸紅、綠、藍模擬信號以及同步信號(水平和垂直信號)。

VGA各針腳定義如下:

VGA支持在640×480的較高分辨率下同時顯示16種色彩或256種灰度,同時在320×240分辨率下可以同時顯示256種顏色。使用VGA連接設備時,線纜長度通常不超過10米,而且要注意接頭是否安裝牢固,否則可能引起圖像中出現虛影。

1.2 HDMI視頻接口

高清晰度多媒體接口(High Definition Multimedia Interface,HDMI)是一種數字化視頻/音頻接口技術,是適合影像傳輸的專用型數字化接口,HDMI可同時傳送音頻和影音信號,且在信號傳送前無需進行數/模或者模/數轉換,是當前視音頻主選接口。

HDMI自2002年提出以來,已發展到HDMI 2.1標準。該標準能夠支持4K 120Hz、8K 60Hz以及高動態范圍成像(HDR),能夠針對場景或幀數進行優化,并向后兼容HDMI 2.0和HDMI 1.4,其中HDMI 1.4最高數據傳輸速度為10.2Gbps,HDMI 2.0最高數據傳輸速度為18Gbps。

HDMI在物理接口上主要包括以下幾種類型:標準HDMI接口、mini HDMI接口和Micro HDMI接口。長距離傳輸通常線材較硬 ,采用標準HDMI接口以確保穩固連接;而小設備通常采用mini HDMI接口和Micro HDMI接口。

1.3 VGA與HDMI對比

VGA與HDMI的對比如下:

1. VGA傳輸模擬信號,傳輸過程需要轉換和緩存,存在一定損失;HDMI傳輸數字信號,數據需要無壓縮,短距離無轉換無損失;

2. VGA僅支持視頻傳輸;HDMI同時支持音頻傳輸;

3. VGA采用PC標準,色階從0至255;HDMI采用TV標準,色階默認從15至255;

4. VGA在高分辨率下會存在失真虛化的問題;HDMI支持4K高清分辨率;

5. VGA不存在兼容顧慮;HDMI在PC上兼容性一般,通常不支持三屏以上多屏顯示。

隨著數字圖像的發展,VGA接口被淘汰已成為趨勢,目前大部分新生產的PC和顯示器設備都不再支持VGA接口。然而,由于VGA標準早期的影響較大,大量投影儀等設備仍采用VGA,因此VGA接口目前仍被大量使用。

02圖像顯示時序分析

盡管HDMI接口為減少干擾、增強傳輸可靠性采用了TMDS編碼,但其圖像掃描的本質方法與VGA相同:通過行同步與場同步進行掃描控制。在設計過程中通常采用專用芯片(例如SIL9134 HDMI編碼芯片與SIL9013 HDMI解碼芯片)完成TMDS編碼操作,因此掌握行同步與場同步的控制時序,就可以完成視頻圖像的顯示。

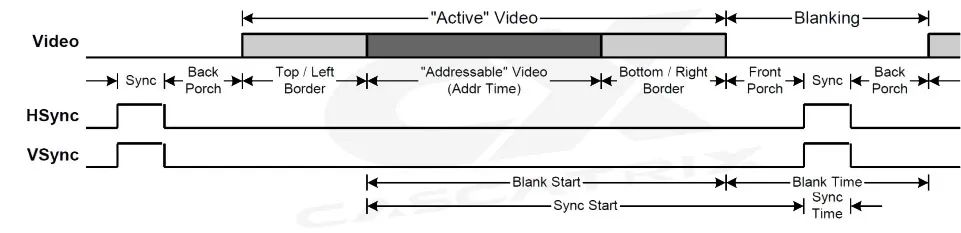

2.1 圖像顯示時序

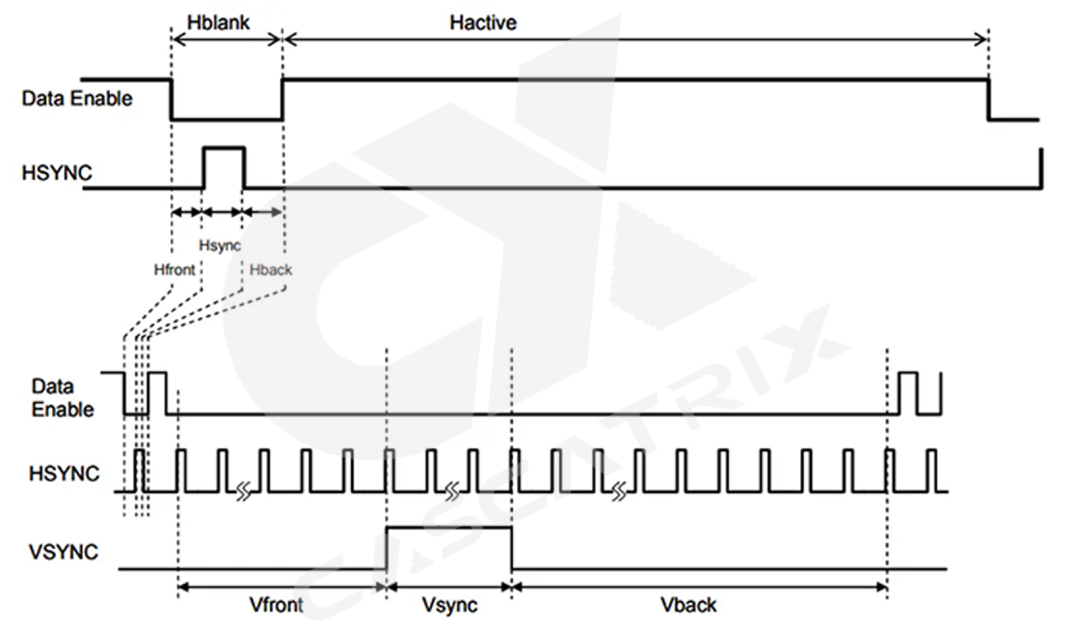

視頻圖像顯示通常采用逐行掃描的方法:從屏幕左上方開始,從左向右逐點掃描。每行掃描完成時,用行同步信號HSYNC進行同步,電子束回到下一行最左側起始位置,同時CRT對電子束進行行消隱;每幀所有行掃描完成時,用場同步信號VSYNC進行幀同步,電子束回到屏幕左上方,同時CRT對電子束進行進行場消隱,開始下一幀掃描。

HSYNC為行同步信號(Horizontal Synchronization),低電平時完成圖像行數據掃描,高電平時進行行同步;VSYNC為場同步信號(Vertical Synchronization),低電平時進行圖像數據掃描,高電平時進行幀同步。

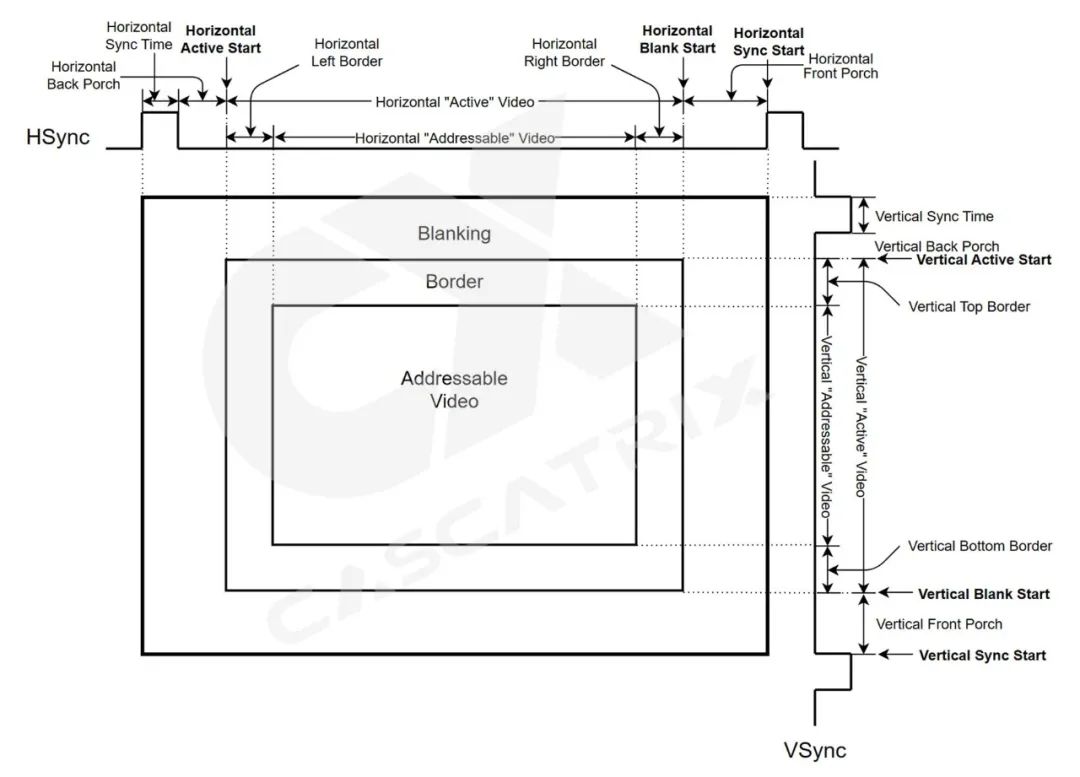

行同步信號HSYNC和場同步信號VSYNC均由四部分組成:Sync同步脈沖 + Back Porch消隱后肩時間 + Active Video數據有效時間 + Front Porch消隱前肩時間。

一幅圖片的顯示包括有效數據部分和消隱區部分,Blanking為圖像的消隱區,Border和Addressable Video部分為圖像的有效數據部分,在800×600及以上分辨率中Horizontal Left Border、Horizontal Right Border、Vertical Top Border、Vertical Bottom Border四個參數為0,即不存在Border區域。

行同步時序以像素為單位,場同步時序以行為單位。例如1920×1080分辨率的圖像,行時序以每行1920個像素進行同步和有效傳輸,場時序以每幀1080行進行同步和有效傳輸。

2.2 不同分辨率顯示參數

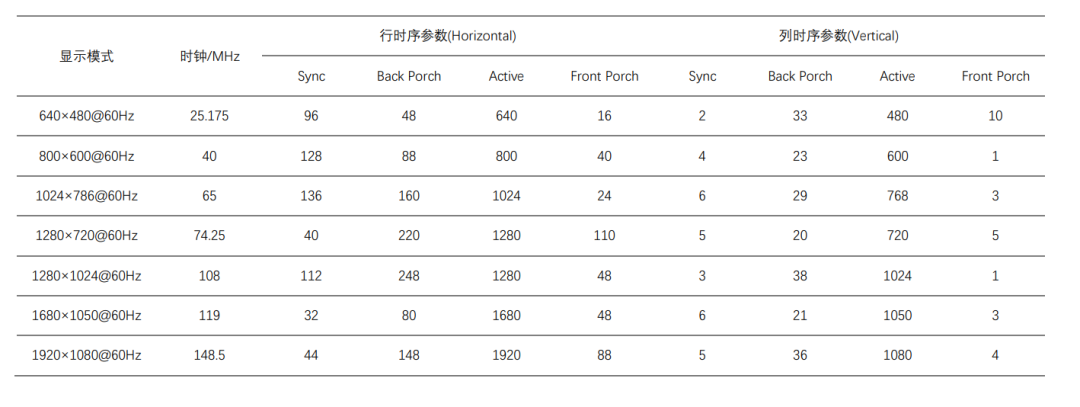

通過行場同步時序分析可知,對于圖像分辨率為1920×1080@60Hz的圖像顯示,時鐘傳輸頻率并非僅考慮有效數據像素1920×1080×60=124.416MHz,而應當同時考慮有效數據和消隱區數據2200×1125×60=148.5MHz。

不同分辨率圖像有效數據和消隱區像素分布如下:

03圖像顯示代碼實現

3.1 Verilog代碼

通過HDMI接口顯示圖像信息,主要包括兩部分:行場同步等信號生成模塊與IIC配置TMDS編碼芯片模塊。由于IIC協議配置芯片寄存器實現方法已在IIC協議中介紹,所以這里給出不同分辨率下HDMI行場同步信號的生成代碼:

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company: Cascatrix

// Engineer: Carson

//

// Create Date: 2023/01/15

// Design Name: Image_Base

// Module Name: cx_image

// Tool Versions: v1.0

// Description: Image read and generate display parameters

//

//////////////////////////////////////////////////////////////////////////////////

`define PIXEL_1920_1080

//`define PIXEL_1680_1050

//`define PIXEL_1280_1024

//`define PIXEL_1280_720

//`define PIXEL_1024_768

//`define PIXEL_800_600

//`define PIXEL_640_480

module cx_image(

inputwireclk,

outputreghs,

outputregvs,

outputwireen,

outputwire [23:0]data

);

//1920x1080 148.5Mhz

`ifdef PIXEL_1920_1080

parameter H_ACTIVE = 1920;// 行數據有效時間

parameter H_FRONT_PORCH = 88; // 行消隱前肩時間

parameter H_SYNC_TIME = 44; // 行同步信號時間

parameter H_BACK_PORCH = 148; // 行消隱后肩時間

parameter V_ACTIVE = 1080;// 列數據有效時間

parameter V_FRONT_PORCH = 4; // 列消隱前肩時間

parameter V_SYNC_TIME = 5; // 列同步信號時間

parameter V_BACK_PORCH = 36; // 列消隱后肩時間

`endif

//1680x1050 119Mhz

`ifdef PIXEL_1680_1050

parameter H_ACTIVE = 1680;// 行數據有效時間

parameter H_FRONT_PORCH = 48; // 行消隱前肩時間

parameter H_SYNC_TIME = 32; // 行同步信號時間

parameter H_BACK_PORCH = 80; // 行消隱后肩時間

parameter V_ACTIVE = 1050;// 列數據有效時間

parameter V_FRONT_PORCH = 3; // 列消隱前肩時間

parameter V_SYNC_TIME = 6; // 列同步信號時間

parameter V_BACK_PORCH = 21; // 列消隱后肩時間

`endif

//1280x1024 108Mhz

`ifdef PIXEL_1280_1024

parameter H_ACTIVE = 1280;// 行數據有效時間

parameter H_FRONT_PORCH = 48; // 行消隱前肩時間

parameter H_SYNC_TIME = 112; // 行同步信號時間

parameter H_BACK_PORCH = 248; // 行消隱后肩時間

parameter V_ACTIVE = 1024;// 列數據有效時間

parameter V_FRONT_PORCH = 1; // 列消隱前肩時間

parameter V_SYNC_TIME = 3; // 列同步信號時間

parameter V_BACK_PORCH = 38; // 列消隱后肩時間

`endif

//1280X720 74.25MHZ

`ifdef PIXEL_1280_720

parameter H_ACTIVE = 1280;// 行數據有效時間

parameter H_FRONT_PORCH = 110; // 行消隱前肩時間

parameter H_SYNC_TIME = 40; // 行同步信號時間

parameter H_BACK_PORCH = 220; // 行消隱后肩時間

parameter V_ACTIVE = 720; // 列數據有效時間

parameter V_FRONT_PORCH = 5; // 列消隱前肩時間

parameter V_SYNC_TIME = 5; // 列同步信號時間

parameter V_BACK_PORCH = 20; // 列消隱后肩時間

`endif

//1024x768 65Mhz

`ifdef PIXEL_1024_768

parameter H_ACTIVE = 1024;// 行數據有效時間

parameter H_FRONT_PORCH = 24; // 行消隱前肩時間

parameter H_SYNC_TIME = 136; // 行同步信號時間

parameter H_BACK_PORCH = 160; // 行消隱后肩時間

parameter V_ACTIVE = 768; // 列數據有效時間

parameter V_FRONT_PORCH = 3; // 列消隱前肩時間

parameter V_SYNC_TIME = 6; // 列同步信號時間

parameter V_BACK_PORCH = 29; // 列消隱后肩時間

`endif

//800x600 40Mhz

`ifdef PIXEL_800_600

parameter H_ACTIVE = 800;// 行數據有效時間

parameter H_FRONT_PORCH = 40 ;// 行消隱前肩時間

parameter H_SYNC_TIME = 128;// 行同步信號時間

parameter H_BACK_PORCH = 88 ;// 行消隱后肩時間

parameter V_ACTIVE = 600;// 列數據有效時間

parameter V_FRONT_PORCH = 1 ;// 列消隱前肩時間

parameter V_SYNC_TIME = 4 ;// 列同步信號時間

parameter V_BACK_PORCH = 23 ;// 列消隱后肩時間

`endif

//640x480 25.175Mhz

`ifdef PIXEL_640_480

parameter H_ACTIVE = 640; // 行數據有效時間

parameter H_FRONT_PORCH = 16 ; // 行消隱前肩時間

parameter H_SYNC_TIME = 96 ; // 行同步信號時間

parameter H_BACK_PORCH = 48 ; // 行消隱后肩時間

parameter V_ACTIVE = 480; // 列數據有效時間

parameter V_FRONT_PORCH = 10 ; // 列消隱前肩時間

parameter V_SYNC_TIME = 2 ; // 列同步信號時間

parameter V_BACK_PORCH = 33 ; // 列消隱后肩時間

`endif

parameter H_TOTAL_TIME = H_ACTIVE + H_FRONT_PORCH + H_SYNC_TIME + H_BACK_PORCH;

parameter V_TOTAL_TIME = V_ACTIVE + V_FRONT_PORCH + V_SYNC_TIME + V_BACK_PORCH;

reg h_act;

reg v_act;

reg [12:0] h_syn_cnt;

reg [12:0] v_syn_cnt;

reg [31:0] image_cnt;

// 有效數據控制

assign en = h_act & v_act;

// 行掃描計數器

always@(posedge clk)

begin

if(h_syn_cnt == H_TOTAL_TIME - 1)

h_syn_cnt <= 13'b0;

else

h_syn_cnt <= h_syn_cnt + 1'b1;

end

// 列掃描計數器

always@(posedge clk)

begin

if(h_syn_cnt == H_TOTAL_TIME - 1)

begin

if(v_syn_cnt == V_TOTAL_TIME-1)

v_syn_cnt <= 13'b0;

else

v_syn_cnt <= v_syn_cnt + 1'b1;

end

end

// 行同步控制

always@(posedge clk)

begin

if(h_syn_cnt < H_SYNC_TIME)

hs <= 1'b0;

else

hs <= 1'b1;

end

// 場同步控制

always@(posedge clk)

begin

if(v_syn_cnt < V_SYNC_TIME)

vs <= 1'b0;

else

vs <= 1'b1;

end

// 行有效控制

always@(posedge clk)

begin

if(h_syn_cnt == H_SYNC_TIME + H_BACK_PORCH - 1)

h_act = 1'b1;

else if(h_syn_cnt == H_SYNC_TIME + H_BACK_PORCH + H_ACTIVE - 1)

h_act = 1'b0;

end

// 列有效控制

always@(posedge clk)

begin

if(v_syn_cnt == V_SYNC_TIME + V_BACK_PORCH - 1 && h_syn_cnt == 0)

v_act = 1'b1;

else if(v_syn_cnt == V_SYNC_TIME + V_BACK_PORCH + V_ACTIVE - 1 && h_syn_cnt == 0)

v_act = 1'b0;

end

// 像素數計數器

always@(posedge clk)

begin

if(image_cnt == H_ACTIVE*V_ACTIVE - 1)

image_cnt <= 'd0;

else if(h_act & v_act)

image_cnt <= image_cnt + 1;

end

// 圖像像素值存儲rom

rom_image inst_rom_image

(

.clk (clk),

.en (h_act & v_act),

.addr (image_cnt),

.dout (data)

);

endmodule

rom_image為圖像像素數據存儲模塊,根據不同地址依次存入對應像素的像素值。該模塊可通過Matlab生成,具體方法將在后續FPGA數字圖像仿真中介紹。部分代碼如下:

module rom_image

(

input clk,

input[31:0] addr,

inputen,

output[23:0]dout

);

reg [23:0] DATA;

assigndout = DATA;

always@(*)

begin

if(en)

case(addr)

0 : DATA<=24'hB18D81;

1 : DATA<=24'h967266;

2 : DATA<=24'h987468;

...

2073597 : DATA<=24'hAE8070;

2073598 : DATA<=24'hAE8070;

2073599 : DATA<=24'hC79989;

default: DATA<= 0;

endcase

else

DATA <= 0;

end

endmodule

3.2 實現效果分析

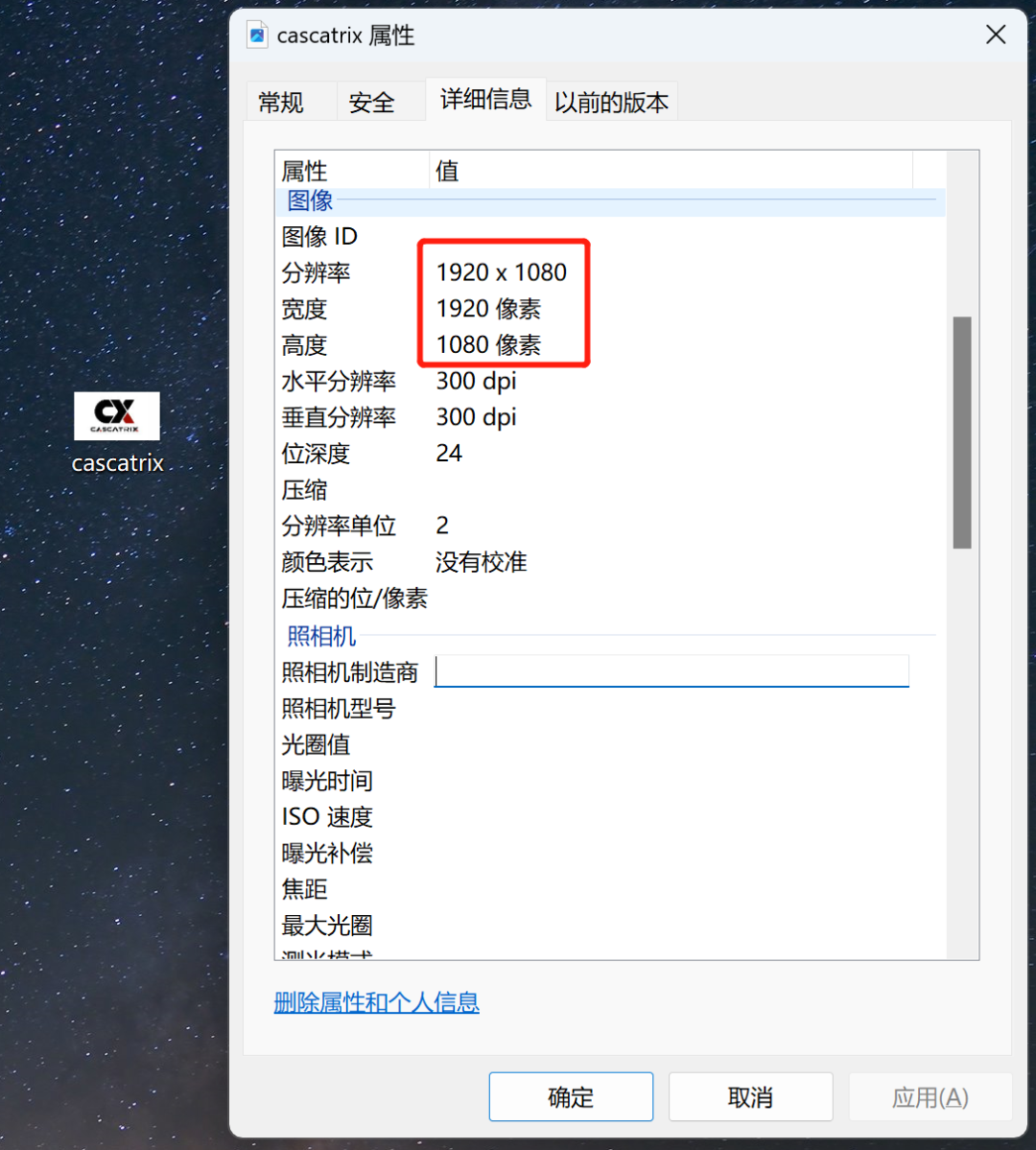

選擇分辨率為1920×1080的圖像:

FPGA通過HDMI輸入到顯示器,顯示效果如下:

-

FPGA

+關注

關注

1641文章

21910瀏覽量

611664 -

HDMI

+關注

關注

32文章

1804瀏覽量

154043 -

接口

+關注

關注

33文章

8873瀏覽量

152936 -

Verilog

+關注

關注

28文章

1363瀏覽量

111398 -

數字圖像

+關注

關注

2文章

119瀏覽量

18990

原文標題:FPGA數字圖像顯示原理與實現(Verilog)

文章出處:【微信號:Carlinx FPGA,微信公眾號:Carlinx FPGA】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

評論