作者:Doug Mercer and Joe DiPilato

引腳兼容的AD976x系列8位、10位、12位和14位TxDAC?低失真DAC以高達125 MSPS的時鐘速率提供出色的無雜散動態范圍(SFDR)規格,具有CMOS器件典型的低價格和功耗水平。

面向消費者的無線和有線通信市場的迅速擴張催生了對高速模數和數模轉換器的永不滿足的需求,這些轉換器具有良好的動態(頻域)性能,成本低,功耗低。最明顯的表現是為滿足接收路徑的需求而開發的新型CMOS ADC產品的盛宴;但是,目前缺乏適合許多發射信號路徑應用的具有動態性能的低成本CMOS DAC產品。

傳統的時域和直流線性度特性,如積分非線性(INL)、差分非線性(DNL)、毛刺脈沖和建立時間,都不足以反映頻域中的響應和失真。大多數現有的高速CMOS DAC主要用于視頻應用,其無雜散動態范圍(SFDR)和諧波失真(THD)往往較差。雙極性和BiCMOS器件可以提供所需的動態性能,但它們通常成本太高,需要雙電源,并且功耗過高,不適合未來的大容量通信應用。

低功耗需求是由通信平臺的變化驅動的。它們要么在物理上變得越來越小,需要更高的組件封裝密度(例如,微型和微型基站封裝在懸掛在電線桿和建筑物側面的小盒子中);或便攜式和電池供電(例如,電話、尋呼機、抄表終端等);或由電話線供電(無線本地環路);或需要備用電池(電纜電話、生命線服務)。這些要求都要求低功耗以延長電池壽命,最大限度地減少散熱,并在有限的可用功率下運行。在這方面,單電源組件避免了額外電源的成本和低效率。3V 單電源器件正變得非常流行,以實現更低的功耗并與高密度數字電路兼容。

這些對低成本、低功耗和良好動態性能的要求導致了用于發射應用的新型高速CMOS DAC的開發。這種新型低成本TxDAC?系列的額定更新速率高達125 MHz,是高速發送路徑CMOS DAC的重大突破。它們提供的SFDR性能是迄今為止高速CMOS DAC無法實現的。

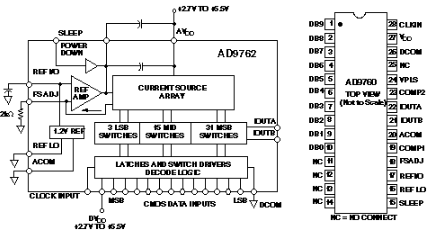

TxDAC系列的前五款產品包括8位、50 MSPS AD9708AR;10位、50 MSPS AD9760AR-50;10位、125 MSPS AD9760AR;12位、125 MSPS AD9762AR;以及14位、125MSPS AD9764AR。所有五種型號均采用引腳兼容的28引腳SOIC封裝,使設計人員能夠在設計周期的評估階段輕松權衡性價比。圖1顯示了12位AD9762的功能框圖和10位AD9760的引腳排列。無論分辨率如何,MSB (DB N1) 在該系列中始終是引腳 1;低分辨率設備可以直接連接到為高分辨率設備布線的電路。這允許統一的設計尺寸和直接交換不同分辨率的模型,以便進行比較、升級和降低定價。

圖1.AD9762框圖和AD9760引腳排列。

這些器件采用低成本亞微米單多晶硅雙金屬CMOS工藝制造。每個DAC的模擬和數字電路均可采用+2.7 V至+5.5 V單電源供電(提供全3 V單電源供電)。每個DAC包括一個溫度補償型1.2 V帶隙基準電壓源,提供高達20 mA滿量程(順從電壓= 1.25 V)的差分電流輸出,由片內基準電壓放大器調節,可使用外部電阻在2 mA至20 mA范圍內進行設置。DAC輸出在35 ns內穩定至最終值的0.25%以內。滿量程10%至90%的上升和下降時間規定為2.5 ns,輸出傳播延遲僅為1 ns。

設計特點

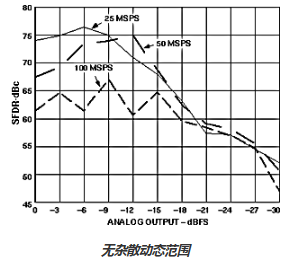

為了消除與傳統R-2R梯形架構相關的幅度相關失真,并實現卓越的交流和直流性能,TxDAC采用了分段電流源。例如,12位AD9762的核心是49個電流源(圖1)。5 個最高有效位對輸出的貢獻由最多 31 個相等的電流源相加而成,每個電流源的權重為 25司 司長。接下來四位的貢獻是通過將最多 15 個電流源相加,其權重是第一組的 1/16(即 29FS 每個)。3 LSB 由或多或少的傳統 3 位二進制 DAC 開關電流組成,其權重為第二組的 1/2、1/4 和 1/8。這種分段架構是AD9762實現±0.5 LSB 12位DNL性能和5 pV-s低輸出毛刺脈沖規格以及多音應用中出色SFDR的關鍵,在這些應用中,DAC的輸出通常以1/2或1/4滿量程工作。圖2顯示了AD9762在不同速率下的單音SFDR與輸出電平的關系。

對于通信應用的傳輸路徑,分段電流源架構本身不足以實現所需的SFDR。為了減少交流失真的固有原因,尤其是諧波,我們集中精力在改進輸出開關時序上。由此產生的創新專有鎖存器和開關電路使SFDR比傳統的CMOS“視頻”DAC產品提高了約20 dB。此外,TxDAC 系列的 SFDR 性能可與最好的雙極性和 BiCMOS IC 器件相媲美,但功耗和價格僅為其一小部分。

無雜散動態范圍圖2.SFDR與不同采樣率下的輸出幅度的關系。

為什么SFDR在通信中很重要?通常,傳輸的信息與其他通信信道和應用程序共享頻譜/帶寬(例如,通過公共電纜廣播或傳輸的不同電視頻道,蜂窩系統中的不同呼叫者,不同的FM廣播電臺等)。如果發射器將雜散信號發送到其他頻段,它們可能會損壞、中斷或消除相鄰信號。這被認為是不好的做法,違反了FCC(和其他監管機構)的規定,并可能導致法律訴訟。

TxDAC系列在奈奎斯特頻段的SFDR從時鐘頻率為100 MSPS并產生40 MHz輸出信號時的57 dB(10位AD9760)到78 dB(時鐘頻率為20 MSPS,產生2 MHz輸出)(14位AD9764)。表1顯示了AD9760、AD9762和AD9764在不同時鐘速率和輸出頻率下的典型SFDR和THD規格。雖然 12 位和 14 位器件為滿量程正弦波提供類似的 SFDR,但更高分辨率器件對于具有高峰均比和大量低電平內容的信號具有更好的 SFDR。圖3顯示了12位AD9762奈奎斯特范圍內的典型頻譜圖,輸出由時鐘速率為100 MSPS的單個20 MHz信號組成;圖中為60.8 dB的二次諧波,其余雜散為<75 dB。在大多數窄帶應用中,諧波被濾除,“一個窗口”或“無諧波”內的SFDR才是最重要的。在這種情況下,TxDAC系列提供80 dB范圍內的性能,即使對于10位AD9760,時鐘頻率為100 MSPS的5 MHz范圍內的輸出也是如此。

在寬帶應用中,DAC將在其輸出端產生多個信號,雙音或多音性能尤其令人感興趣。突出的應用是通過電纜同時發送兩個或多個數據/語音/視頻通道。寬帶蜂窩基站是另一個,除此之外,還有ADSL(非對稱數字用戶線)等應用,它利用基于多音調的離散調制方案,并依賴于良好的多音性能。

| 表 1.典型的 SFDR 和 THD 規格 | |||

| SFDR | AD9760 | AD9762 | AD9764 |

|

FC=50兆赫;F外=5.05 MHz 至奈奎斯特 |

67分貝 |

70分貝 |

70分貝 |

|

FC=50兆赫;F外=20.2 MHz 至奈奎斯特 |

642分貝 |

67分貝 |

67分貝 |

|

FC=100兆赫;F外=5.05 MHz 至奈奎斯特 |

61分貝 |

64分貝 |

64分貝 |

| FC=100兆赫;F外=40.4 MHz 至奈奎斯特 | 57分貝 | 60分貝 |

60分貝 |

| FC=50兆赫;F外=5.05兆赫;2 兆赫跨度 | 84分貝 | 84分貝 | 84分貝 |

| FC=100兆赫;F外=5.05兆赫;2 兆赫跨度 | 84分貝 | 84分貝 | 84分貝 |

| 諧波失真 | |||

| FC=50兆赫;F外=5.05兆赫 |

-61 分貝 |

-64 分貝 |

-64 分貝 |

| FC=100兆赫;F外=5.05 |

-57 分貝 |

-60 分貝 |

-60 分貝 |

圖3.以 100 MSPS 采樣的 19.96MHz 正弦波;差分輸出,50(歐姆),20 pf,SFDR = 60.8 dB。

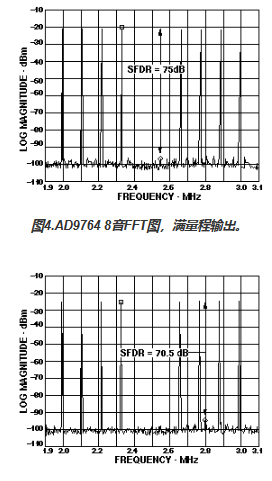

在大多數多音應用中,發射路徑DAC的輸出通常在滿量程范圍的一小部分(例如,1/2或1/4 FS)下工作,以確保DAC輸出不會與接近滿量程的所有通道削波(削波發射波形產生的諧波可能導致非法“飛濺”)。圖4和圖5分別顯示了AD9764滿量程和半量程8音波形的頻譜圖;兩者都表示SFDR>70 dBc,這是創新轉換器架構的重要結果。TxDAC系列的各種型號已經針對在單音測試中表現相當的BiCMOS DAC進行了測量;TxDAC在多音應用中實現了可重復的更好性能。這可能與廣泛使用的R-2R梯形網絡架構引起的時序偏差有關,TxDAC專有的電流開關架構已經過優化以最小化。

圖5.AD9764 8音FFT圖,1/2電平輸出。

TxDAC 內核中使用的開關電路提供真正的差分輸出,從而在差分使用器件時提高性能。盡管TxDAC系列的單端性能本身非常出色,但當輸出通過變壓器差分驅動時,可以實現最佳的諧波性能。表2顯示了12位AD9762的差分性能比單端性能的改善,特別是在較高頻率下。

| 表 2.AD9762 無雜散動態范圍,fs = 125 MSPS | ||

| 單音 | 單端 | 微分 |

|

1兆赫 |

70分貝 |

72分貝 |

|

5兆赫 |

63分貝 |

70分貝 |

|

10兆赫 |

58分貝 |

65分貝 |

| 39兆赫 | 46分貝 | 54分貝 |

每個DAC采用+5 V單電源供電,時鐘頻率為100 MSPS,功耗為150 mW,配置為20 mA滿量程電流輸出。時鐘頻率為40 MSPS,采用+3 V單電源供電,配置為2 mA滿量程輸出,功耗降至極低的35 mW。每個器件都支持睡眠模式,當DAC不工作時,功耗從+5 V降至<30 mW。

在許多情況下,數字通信系統的品質因數是其誤碼率(BER)。誤碼率通常由適當的標準/規范決定,并受模擬元件性能、傳輸介質、調制方案、數據速率以及可用的均衡和糾錯電路的組合影響。各種不同的無線和有線應用(包括用于蜂窩、PCS、尋呼機、無線本地環路和衛星服務的無線基站和終端,以及用于互聯網接入的有線調制解調器、交互式視頻機頂盒和數字用戶線路,如 ADSL、HDSL、VDSL 等)使用許多不同的調制方案,適應不同的數據速率,并需要不同的系統級性能。

在這些情況下,由于與DAC性能缺乏獨特的關系,通信系統設計人員很難確定轉換器所需的分辨率/動態范圍。幸運的是,TxDAC的引腳兼容尺寸允許在開發周期的任何階段進行性價比權衡,并為未來更高性能的系統提供了升級途徑。系統設計人員可以靈活地在誤碼率性能與系統成本之間進行權衡。該選擇允許設計人員適應一定的誤差范圍,補償均衡和糾錯方法和性能。此外,由于給定調制方案的數據速率與帶寬和動態范圍成正比,因此設計人員可以在高端器件上提供更高的數據速率。

兩種基本的發射架構如圖6和圖7所示。在基于正交的調制方案中,例如QPSK和QAM,部署混頻器以將同相(I)和正交(Q-90度異相)信號混合成復合單邊帶信號以進行傳輸。圖6所示為基帶發射架構,該架構可模擬I和Q信號混合。在本例中,每個發射通道需要兩個DAC。即使在許多基帶應用中使用的低輸出頻率下,TxDAC系列也是最佳選擇,因為該系列的所有成員在低輸出頻率下都結合了(1)高SFDR;(2)低功耗,單電源和3V操作,提高系統電源效率;(3)有競爭力的價格(通過對信號進行過采樣(插值)來減少DAC的帶內混疊鏡像,從而減輕低通濾波器的工作,從而進一步降低總成本);(4) 同一引腳布局中提供的各種分辨率允許最終的成本/性能權衡。例如,在許多 TxDAC 測試版站點應用程序中,用戶從一個分辨率模型開始,然后根據實際系統性能設計更高或更低分辨率的設備。

圖6.具有模擬正交混頻的基帶發射架構。

圖7中的系統架構使用I和Q信號的數字混頻,并將調制信號直接輸入到單個DAC。在這種情況下,DAC的帶寬要求更加嚴格。通過數字調制,可以通過TxDAC芯片產生40 MHz范圍內的中頻(IF)。這足以直接傳輸高速調制解調器中的數據和交互式機頂盒中的上游信息。在其他應用中,它可以消除上變頻器級。在這里,高SFDR、低價格、低功耗和系列引腳兼容性也是理想的(必需)屬性。如果將多個數字I&Q調制器饋入圖7所示的單個DAC,則系統將對應于寬帶發射架構,為此,TxDAC系列產品的卓越多音性能是一個主要的性能屬性。

10位AD9760正在進入高速互聯網數據調制解調器和交互式機頂盒,其中SFDR要求在50 dB范圍內,輸出頻率為40 MHz,時鐘速率高達120 MSPS。它們還用于無線本地環路和高速無線集群基站。這些 12 位器件被設計用于蜂窩和個人通信服務 (PCS) 基站、電纜頭端設備和混合光纖同軸調制解調器,在這些器件中,在不同的時鐘和采樣速率下需要高達 70 dB 的 SFDR。14位AD9764正在ADSL調制解調器和下一代PCS基站中找到一>,在這些基站中,1 MHz至6 MHz信號需要70 dB<時鐘速率為15 MSPS。

圖7.具有數字調制的傳輸架構。

用于普通CMOS制造的芯片設計的一個主要優勢是數字集成兼容性。TxDAC內核基于CMOS工藝進行了優化,可實現與數字信號處理(DSP)電路的高效集成,從而進一步節省電路板和成本,并增強性能和可靠性。通過將數字處理與DAC內核集成,可以實現比以往任何時候都更高速的數字切換。

例如,在使用數字DDS引擎和高性能(雙極性)DAC的傳統雙芯片直接數字合成(DDS)系統中,速度和分辨率受到將數字數據從DDS芯片時鐘傳輸到DAC所需的速度和功率的限制(TTL邏輯限制為約100 MSPS)。通過將DDS電路與DAC集成,內部數據速率將>200 MSPS可用且經濟。除了單芯片高性能DDS(見第12頁)外,未來的片上數字電路還將包括數字調制器和插值濾波器。

審核編輯:郭婷

-

電源

+關注

關注

184文章

17732瀏覽量

250442 -

轉換器

+關注

關注

27文章

8709瀏覽量

147277 -

變頻器

+關注

關注

251文章

6560瀏覽量

144904

發布評論請先 登錄

相關推薦

FPGA通過SPI對DAC進行了配置,用頻譜儀測不到輸出是怎么回事?

HV857已針對各種應用進行了優化

AD9637-80EBZ,在小封裝尺寸至關重要的應用中針對出色的動態性能和低功耗進行了優化

采用AD9114雙路低功耗8位TxDAC的AD9114-EBZ評估板

DC2103A演示電路針對低啟動電壓進行了優化,采用100:1匝數比變壓器

MIKROE-2815,基于MAX31865電阻數字轉換器,針對鉑電阻溫度檢測器或RTD進行了優化

AD9481-PCB,AD9481評估板是一款8位,單芯片模數轉換器(ADC),針對高速和低功耗進行了優化

對結構體成員進行了賦值

RS通信編碼器怎么進行優化設計?

STM32CubeIDE是否針對新MAC中的Apple M1芯片進行了優化?

TxDAC系列高速DAC的引腳兼容性

DAC針對通信傳輸路徑進行了優化

DAC針對通信傳輸路徑進行了優化

評論