基本的SAR逐次逼近寄存器原理及模型

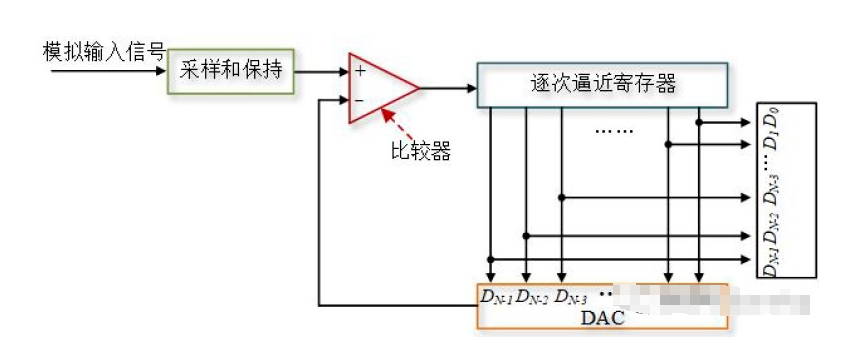

1、逐次逼近寄存器在原理圖中的位置和作用

逐次逼近寄存器英文原稱是Successive Approximation Register,在電路中的主要作用是起邏輯控制和存儲的作用。ADC收到啟動命令后,SHA進入保持模式。SAR的最高有效位(MSB)設置為邏輯1,所有其他位設置為邏輯0。SAR的輸出反饋到DAC,DAC的輸出與輸入輸入信號進行比較。如果DAC輸出大于模擬輸入,則MSB復位,否則保持置位狀態。現在將下一個MSB設置為1,并重復該過程,直到比較SAR的每一位為止。在此過程結束時,SAR的最終值對應于模擬輸入值。轉換過程的結束由就緒 信號指示。

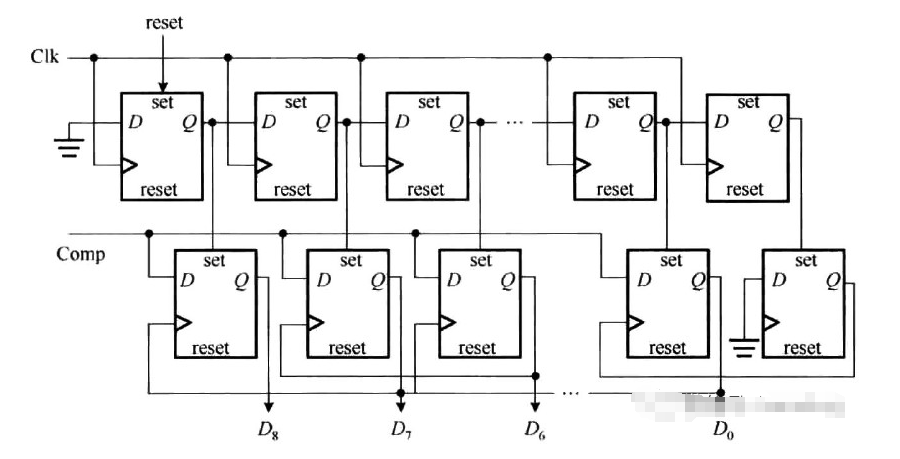

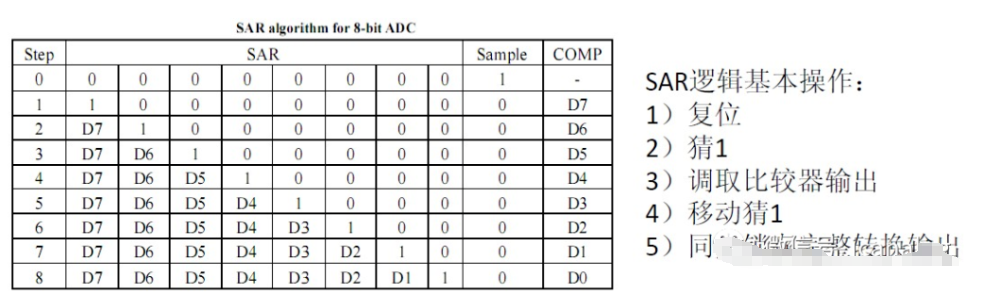

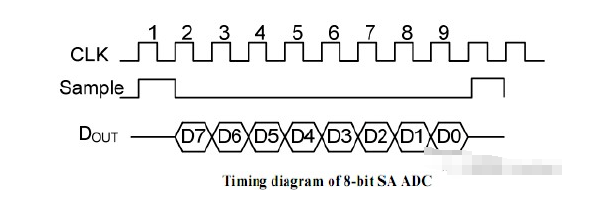

2、SAR的原理圖

圖示由Anderson提出的SAR邏輯的簡要框圖。采樣階段,reset信號把移位寄存器中的第一個觸發器的輸出置1,同時其余觸發器的輸出置0,從而D8也被置1,D7~D0被置0。轉換周期到來時,在時鐘信號(CLK)的控制下,上面一排觸發器的輸出依次變成高電平,從而下面一排觸發器輸出被依次置1,同時它們各自的輸出作為前一級觸發器 的時鐘信號,因此D8~D0分別在被置位后根據比較器的輸出結果(COMP)在下一個時鐘上升沿再次觸發得到逐次逼近邏輯信號。

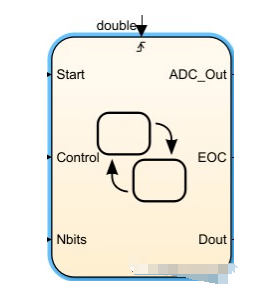

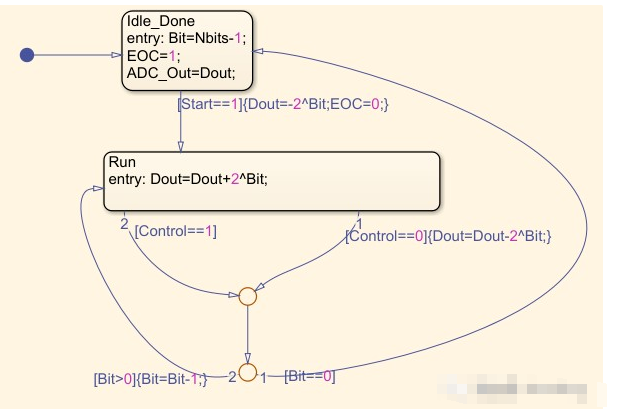

3、MATLAB state flow建模

狀態轉移圖

上圖是MATLAB Simulink中的state chart 其中橢圓符號代表一個狀態,箭頭代表轉移的方向,箭頭中間的字母括號代表著轉移的條件。當一個時間發生時,只有當[]括號中的語句為真或非零時,帶有條件標簽的轉移才有效。轉移可以同時擁有事件和條件;條件要放在事件名之后。當轉移標簽既有事件又有條件時,只有當指定的事件發生并且條件為真時轉移才有效。{}代表要執行的語句。

一個流程圖中,以{}表示的動作僅僅是一個可執行的動作。邏輯分析即和數電狀態轉移分析類似,這里請自行分析。

4、用Verilog 進行建模

Verilog-HDL :處理數字信號Digital signal

Verilog-A :處理模擬連續時間信號Analog continuous-time signal

Verilog-AMS :處理模擬離散時間信號Analog discrete-event signal

可以用這些語言建模,例如D觸發器

module d_latch(d,clk,q);

input d;

input clk;

output q;

reg q;

always @ (d,clk)

if(clk)

q <= d;

endmodule

然后用AMS對其進行數模混合仿真。同樣的原理我們可以用于對SAR

的驗證或者混合信號仿真。也可以用incisive結合testbench進行驗證。詳細過程以后講述。

-

寄存器

+關注

關注

31文章

5343瀏覽量

120377 -

SAR

+關注

關注

3文章

416瀏覽量

45963 -

adc

+關注

關注

98文章

6498瀏覽量

544660 -

Verilog

+關注

關注

28文章

1351瀏覽量

110101 -

逐次逼近寄存器

+關注

關注

0文章

7瀏覽量

8180

發布評論請先 登錄

相關推薦

MAX11335-MAX11340逐次逼近寄存器(SAR)模擬數字轉換器(ADC)

貿澤電子開售Analog AD7386逐次逼近寄存器模數轉換器

什么是逐次逼近寄存器SAR

MAX11120-MAX11128低功耗,逐次逼近寄存器串行ADC

MAX11135-MAX11143逐次逼近寄存器(SAR)模數轉換器(ADC)

MAX11329-MAX11332逐次逼近寄存器ADC

ADS868x單電源逐次逼近寄存器(SAR)模數轉換器(ADC)數據表

ADS9120逐次逼近寄存器(SAR)模數轉換器(ADC)數據表

ADS9110逐次逼近寄存器(SAR)模數轉換器(ADC)數據表

基本的SAR逐次逼近寄存器原理及模型

基本的SAR逐次逼近寄存器原理及模型

評論