服務(wù)器是一種為客戶機(jī)提供服務(wù)的高性能計算機(jī)。關(guān)于服務(wù)器最全分析材料請參考文章“終極版:服務(wù)器基礎(chǔ)知識全解(182頁P(yáng)PT)”。

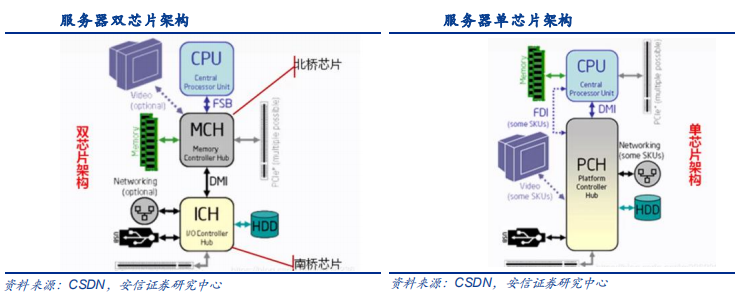

主板芯片組以前均采用雙芯片架構(gòu),即 MCH+ICH(北橋芯片+南橋芯片,MemoryController Hub+ I/O Controller Hub),2012 年 Intel 推出單芯片架構(gòu)后成為主流,即北橋芯片被集成到 CPU 中,南橋芯片改為 PCH(Platform Controller Hub,平臺管理器中樞)。未來,PCH 有進(jìn)一步集成到 CPU 中的趨勢。

南橋芯片(South Bridge,SB)/PCH:處理輸入輸出(Input/Output,I/O)數(shù)據(jù),負(fù)責(zé) PCIe 總線、USB、ATA、SATA、音頻控制器、鍵盤控制器、高級電源管理和實時時鐘控制器等間的通信。位于主板上離 CPU 較遠(yuǎn)的下方,原因是連接的 I/O 總線較多,遠(yuǎn)離 CPU 有利于布線。南橋芯片最初發(fā)展方向是集成主板上更多的通信功能,如網(wǎng)卡和 RAID 等,但 AMD 銳龍低端芯片組許多產(chǎn)品取消了南橋,只支持 CPU所支持的拓展,AMD 最新 Zen2 架構(gòu)平臺上,南橋僅使用 PCI-E X4 通道和 CPU 連接,將通道拆分后支持幾個 PCIe 接口、USB2.0 和 SATA 接口。

北橋芯片(North Bridge,NB):負(fù)責(zé) CPU 與內(nèi)存、加速圖形顯卡(Accelerated GraphicsPort,AGP)以及 PCIe 總線的通信協(xié)調(diào),位于主板上離 CPU 最近的位臵,從而縮短傳輸距離提高通信性能。北橋芯片最初僅作為內(nèi)存控制器出現(xiàn)在主板上,此后又?jǐn)U展了各種控制器,如加速圖形顯卡。但由于延遲大和故障率高等問題,逐漸被取消。Intel 于2012 年推出單芯片架構(gòu),只保留南橋芯片(改名為 PCH,Platform Controller Hub),將北橋芯片集成到 CPU 中,以 PCIe 控制器和內(nèi)存控制器的形式分散存在于晶圓的不同位臵。

隨著 CPU 集成度不斷強(qiáng)大,主板芯片組的功能有被弱化的趨勢,CPU 廠商對芯片組的話語權(quán)也在持續(xù)提高。服務(wù)器芯片組生產(chǎn)商曾經(jīng)生產(chǎn)包括 Intel、AMD、Nvidia 和 VIA(臺灣威盛)等,目前 Intel 和 AMD 占據(jù)主要市場份額,尤以 Intel 為甚,部分國產(chǎn) CPU 參與者由于設(shè)計能力欠缺采用 Intel 或 AMD 的芯片組。

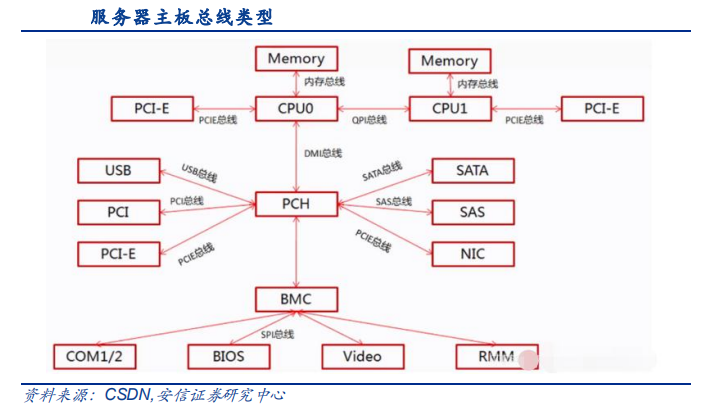

總線是主板傳輸數(shù)據(jù)的“道路”,負(fù)責(zé) CPU 與芯片組(PCH)、PCH 與功能芯片的連接,包括 QPI、PCIe、DMI、SATA、SAS、SPI 總線等。其中,CPU 與 CPU、CPU 與 PCIe 設(shè)備分別通過 QPI 總線和 PCIe 總線連接,PCH 與 USB、SATA 硬盤、SAS 硬盤和網(wǎng)卡等分別通過 USB 總線、SATA 總線、SAS 總線、PCIe 總線等連接,BMC(Baseboard Management Controller,基板管理控制器)與其他設(shè)備通過 SPI 總線連接。

PCIe 總線,負(fù)責(zé)連接擴(kuò)展 I/O 設(shè)備,具有高速低時延的性能,滿足服務(wù)器高速運(yùn)算、快捷訪問數(shù)據(jù)、訪問外設(shè)和訪問網(wǎng)絡(luò)的需求。由于是對前兩代(ISA 和 PCI/PCI-X)的升級,PCIe總線又被稱為第三代 I/O 總線(3GIO),相比于前兩代,數(shù)據(jù)傳輸速率更高、傳輸距離更遠(yuǎn)、功耗更低、抗干擾能力更強(qiáng),可以連接各類高速擴(kuò)展設(shè)備,典型如加速圖形顯示處理器 GPU(Graphics Processing Unit),此外還有 AI 加速卡、PCIe 網(wǎng)卡和視頻監(jiān)控卡等。

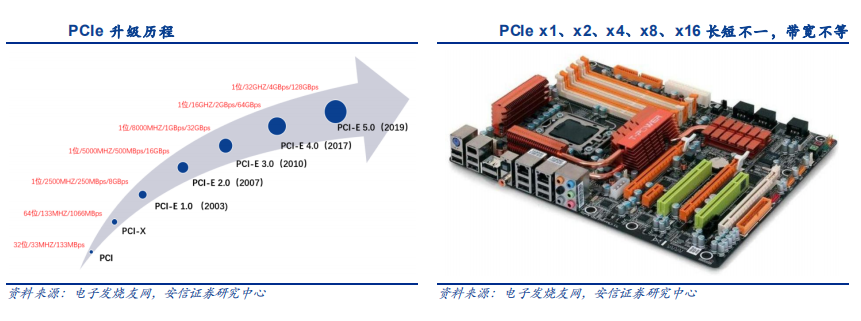

傳輸速率和帶寬大小是 PCIe 總線的核心性能,圍繞這兩大性能,PCIe 總線有特定的升級標(biāo)準(zhǔn),該標(biāo)準(zhǔn)自 2001 年確定 1.0 至今,經(jīng)歷了 2.0、3.0 和 4.0 時代,在 4.0 確立之前,大概按照每三年一代的周期實現(xiàn)性能指標(biāo)升級。PCIe 標(biāo)準(zhǔn)由特殊興趣組織 PCI-SIG 組織負(fù)責(zé)發(fā)布,該組織最初由 Intel 牽頭設(shè)立,目前擁有近 800 名會員。2017 年,PCI-SIG 發(fā)布 PCIe 4.0標(biāo)準(zhǔn),2019 年 5 月發(fā)布 PCIe 5.0。預(yù)計 PCIe 6.0 也將于 2021 年發(fā)布。

PCIe 1.0、2.0、3.0傳輸速率分別為2.5GHz、5GHz和8GHz,單lane帶寬分別達(dá)到250MB/s、500MB/s 和 1GB/s。PCIe 總線由不同 lane 連接,多個 lane 合在一起可提供更高帶寬,兩 個單 lane 合成 x2,兩個 x2 合成 x4,兩個 x4 合成 x8,目前最大為 x16,帶寬需求大的加速顯卡需使用 PCIe x16。從主板插槽形態(tài)上看,x1 最小,x16 最大。PCIe 4.0 可以帶來最大64GBps 的吞吐量(PCIe x16),而 PCIe 5.0 則增加到 128GBps(PCIe x16)。

標(biāo)準(zhǔn)從落地到商用仍有一定周期。雖然 PCIe4.0 標(biāo)準(zhǔn)早在 2017 年發(fā)布,但是根據(jù) Intel 產(chǎn)品路線規(guī)劃圖,適配 PCIe4.0 的 CPU 規(guī)劃在 2020 年 Q2 以后發(fā)布的 Whitley 平臺第二代 IceLake 中出現(xiàn),而適配 PCIe5.0 的 CPU 規(guī)劃在 2021 年發(fā)布的 Eagle Stream 平臺出現(xiàn)。因此預(yù)計 PCIe6.0 商用還有至少三年以上。

PCIe高速設(shè)備包括 GPU、AI 加速卡、視頻監(jiān)控卡、PCIe 接口 SSD 和 PCIe 網(wǎng)卡等,伴隨PCIe 升級至5.0,通過 PCIe 總線連接 CPU 的以上高速設(shè)備有望同步升級。

PCIe總線屬于串行點對點雙通道傳輸,在 x86 系統(tǒng)中體系架構(gòu)主要由 root complex、switch和 endpoint 三類 PCIe 設(shè)備構(gòu)成。BDF(Bus、Device、Function)構(gòu)成每個 PCIe 設(shè)備節(jié)點的身份證號,一般 PCIe 協(xié)議支持 256 個 Bus(總線), 每條 Bus 支持 32 個 Device,每個 Device 支持 8 個 Function。PCIe 總線標(biāo)準(zhǔn)升級帶寬翻倍的同時,外接的 PCIe 設(shè)備帶寬可以實現(xiàn)更大提升。根據(jù) PCI-SIG 官方顯示,使用 PCIe 總線與 CPU 通信的服務(wù)器 I/O 擴(kuò)展設(shè)備,帶寬每三年翻一倍。

“CPU+芯片組+總線”平臺升級按照 2~4 年周期向前推進(jìn),由于 CPU 內(nèi)部主要集成內(nèi)存控制器和 PCIe 控制器,內(nèi)存和 PCIe 總線是平臺升級的兩大關(guān)鍵,需要同時配合 CPU 的升級進(jìn)度實現(xiàn)性能提升。2017 年 7 月 Intel 發(fā)布的 Purley 平臺(包括 Skylake 和 Cascade Lake兩代),相較于上一代 Grantley 平臺:

(1)通道增加 50%,支持 6 通道DDR4;

(2)PCIe接口增加 20%,支持 48 個 PCIe3.0 接口。此外,采用全新的 6*6 的 Mesh 互連架構(gòu),I/O位于頂部,內(nèi)存通道在兩側(cè)居中的位臵;CPU 由上一代最大 24 核提升至 28 核;CPU 之間的互連從 9.6GT/s 的 QPI,升級為 10.4GT/s 的 UPI。

根據(jù)Intel 規(guī)劃路線,最新一代 Whitley平臺于 2020 年發(fā)布,包括 Cooper Lake 和 Ice Lake兩代,按計劃分別于年初和 Q2 面世。其中,Cooper Lake 沿用 PCIe3.0 通道;Ice Lake 將首度支持 PCIe4.0。下一代 Eagle Stream 平臺于 2021 年發(fā)布,包括 Sapphire Rapids 和Granite Rapids 兩代,分別于 2021 年初和 2022 年初面世,同步支持 PCIe5.0。

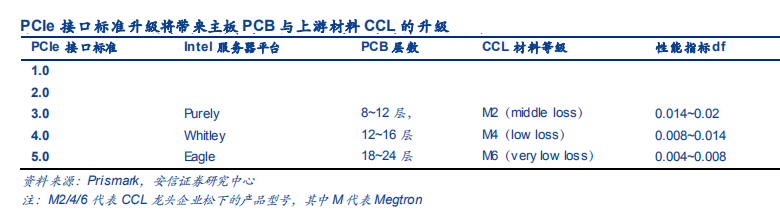

在使用 PCIe3.0 接口的情況下,信號傳輸速率為 8Gbps,服務(wù)器主板 PCB 在 8~12層時就可以滿足要求,相對應(yīng)的CCL 材料 Df 值在0.014~0.02 之間。未來,對于 PCIe4.0接口 16Gbps 的傳輸速率,PCB 層數(shù)需要相應(yīng)提高到12~16 層,CCL 材料 Df 值在0.008~0.014 之間,以 FR4 為主,處于中損耗等級;而對于 36Gbps 傳輸速率的 PCIe5.0接口,PCB 層數(shù)需要達(dá)到 16 層以上,CCL 材料 Df 值需要低于0.008。

PCIe5.0 標(biāo)準(zhǔn)落地,但距離芯片商產(chǎn)品兼容尚需時日,目前 Intel Purely 和 Whitley 平臺分別兼容 PCIe3.0 和 4.0,兼容 5.0 的 Eagle 平臺正在開發(fā)中,因此假設(shè) 2019 年服務(wù)器產(chǎn)品以低等級的 3.0 為主,到 2020 年 Whitley 平臺滲透率可提升至 50%,到 2021 年 Eagle平臺實現(xiàn)落地商用;

服務(wù)器主板 PCB 使用規(guī)格受服務(wù)器類型的影響,從全球服務(wù)器發(fā)貨量來看,雙路服務(wù)器占據(jù)主導(dǎo)位臵,因此我們采用保守估計的方法,按照雙路服務(wù)器 45cm*45cm 的規(guī)格計算主板 PCB 使用需求;此外,服務(wù)器內(nèi)除主板外、I/O 板、硬盤和背板等也是高速 PCB 的關(guān)鍵應(yīng)用場景。

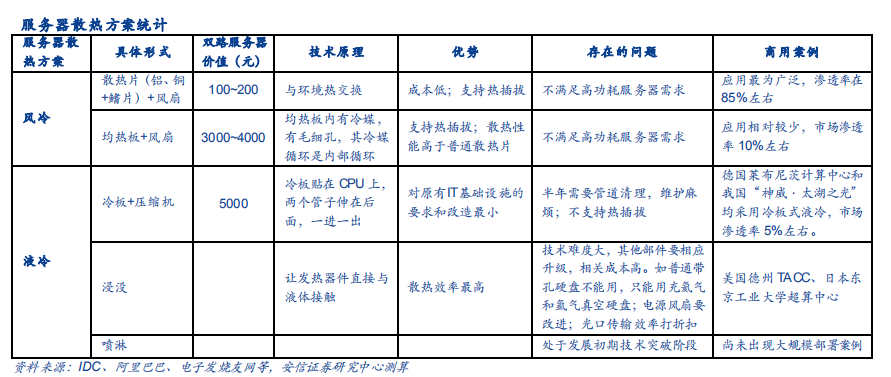

機(jī)箱主要由箱體、硬盤背板、電源、電源背板、散熱風(fēng)扇、硬盤支架、線類和接頭、以及開關(guān)和指示燈等組成。由于 CPU 平臺換代升級導(dǎo)致功耗增加,服務(wù)器機(jī)箱散熱和電源模塊方案同步發(fā)生變化。一方面改善供電方案,提高電力使用效率,在降低成本的同時還能簡化運(yùn)維;另一方面,采用更好的溫控和散熱系統(tǒng),目前液冷已經(jīng)成為數(shù)據(jù)中心制冷新風(fēng)尚。

數(shù)據(jù)中心溫控系統(tǒng)主要包括空調(diào)機(jī)組、氣流組織和服務(wù)器散熱:

(1)空調(diào)機(jī)組從風(fēng)冷型、水冷型向冷凍水型、雙冷源型過渡,氣流組織也從傳統(tǒng)的機(jī)房級向更精準(zhǔn)的機(jī)柜級演進(jìn);

(2)服務(wù)器功率大幅提升,液冷(冷板、浸沒、噴淋三種部署方式)逐漸取代傳統(tǒng)風(fēng)冷成為新模式。

數(shù)據(jù)中心電源需求包括兩塊,一部分是機(jī)房系統(tǒng)供電,另一部分是單臺服務(wù)器模塊電源供電。數(shù)據(jù)中心規(guī)模化建設(shè)或?qū)酉到y(tǒng)供電需求,服務(wù)器需求增加、CPU 功耗提升或?qū)幽K電源量價齊升。

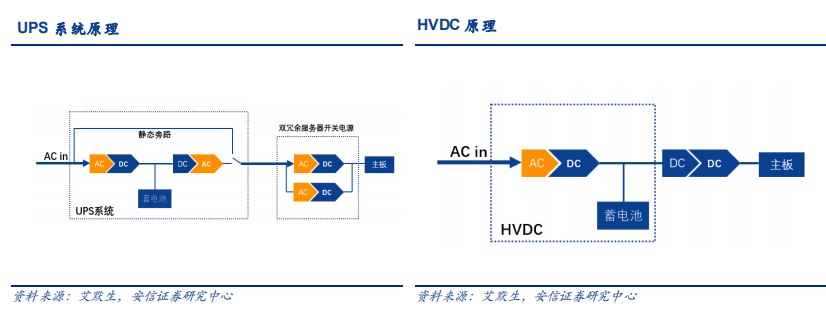

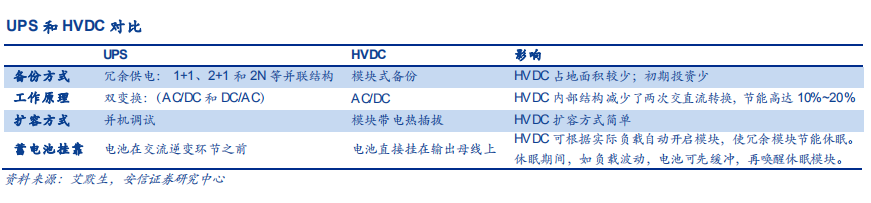

數(shù)據(jù)中心供電方式有傳統(tǒng) UPS(Uniterruptible Power Supply,不間斷供電)和 HVDC(HighVoltage Direct Current,高壓直流)兩種。

UPS 工作原理是市電輸入 UPS 系統(tǒng),經(jīng)過整流器將交流電(AC)轉(zhuǎn)換為直流電(DC),一部分直流電源為蓄電池充電,其余部分通過逆變器轉(zhuǎn)換為交流電(AC)為服務(wù)器機(jī)柜供電。當(dāng)市電不正常時,由蓄電池經(jīng)逆變器向服務(wù)器機(jī)柜供電。這種系統(tǒng)大大提高供電的穩(wěn)定性,成熟度高且廣泛使用。

HVDC高壓直流是一種輸入市電交流電,輸出直流電的電源(UPS輸入和輸出均為交流電的電源)。相較于UPS,HVDC在備份、工作原理、擴(kuò)容以及蓄電池掛靠等方面存在顯著的技術(shù)優(yōu)勢,因而具有運(yùn)行效率高、占地面積少、投資成本和運(yùn)營成本低的特點,正逐步獲得通信基站運(yùn)營商和數(shù)據(jù)中心云服務(wù)廠商的青睞。

-

電源

+關(guān)注

關(guān)注

184文章

17740瀏覽量

250565 -

服務(wù)器

+關(guān)注

關(guān)注

12文章

9205瀏覽量

85557 -

主板

+關(guān)注

關(guān)注

53文章

1893瀏覽量

70938

原文標(biāo)題:服務(wù)器主板及電源介紹

文章出處:【微信號:AI_Architect,微信公眾號:智能計算芯世界】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

獨立服務(wù)器與云服務(wù)器的區(qū)別

基于高通主板的ARM架構(gòu)服務(wù)器

云服務(wù)器和虛擬服務(wù)器的區(qū)別是什么

京準(zhǔn)電鐘:GPS時鐘服務(wù)器(NTP授時服務(wù)器)資料詳細(xì)介紹書

GITSTAR集特 國產(chǎn)龍芯3C5000+7A2000服務(wù)器主板GME-3001

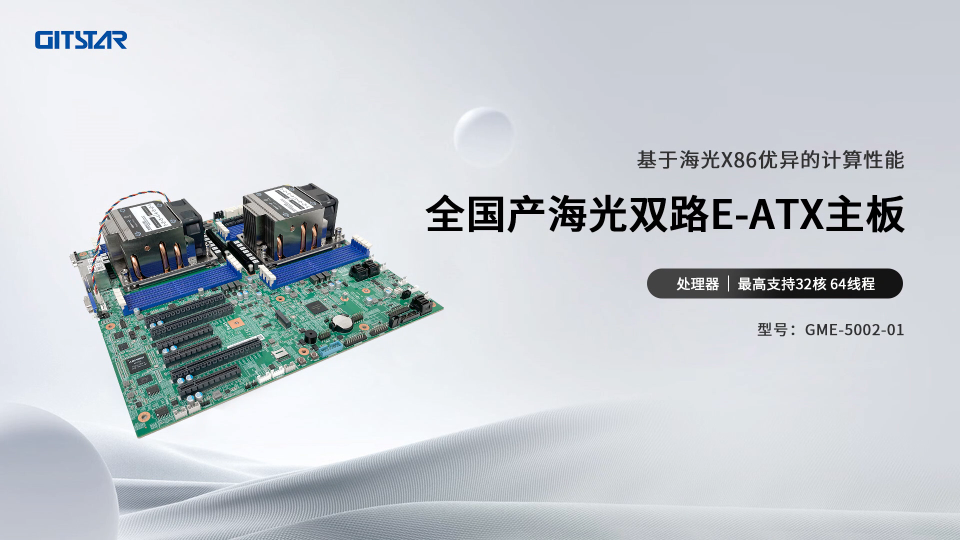

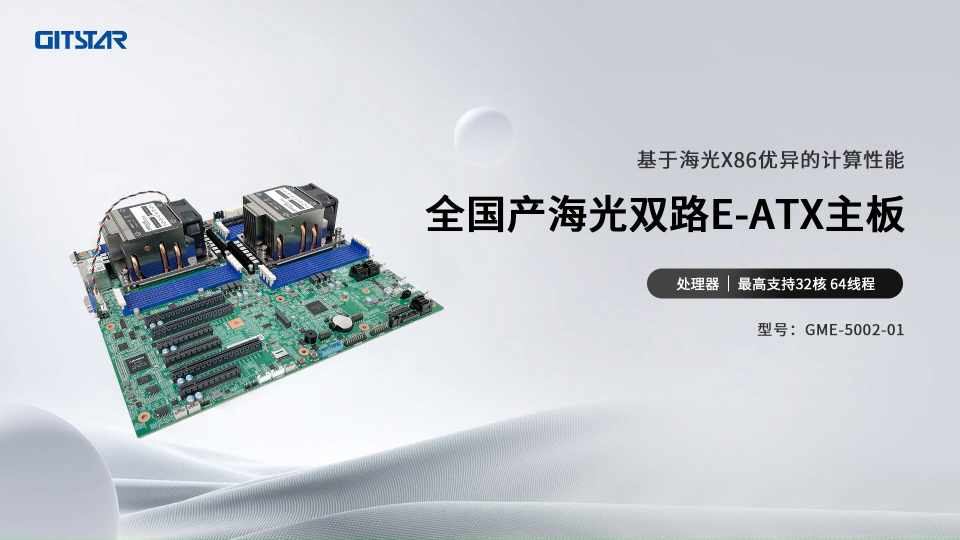

GITSTAR集特海光2/3/4號5000/7000全系列處理器E-ATX工業(yè)服務(wù)器主板GME-5002-01

linux服務(wù)器和windows服務(wù)器

集特 國產(chǎn)龍芯3C5000+7A2000單路服務(wù)器主板GS0-3001#龍芯服務(wù)器主板 #國產(chǎn)主板

MOSFET在服務(wù)器電源上的應(yīng)用

獨立服務(wù)器和云服務(wù)器的區(qū)別

NTP服務(wù)器介紹

服務(wù)器的主板及電源介紹

服務(wù)器的主板及電源介紹

評論