模數轉換器(ADC)是任何系統中不可或缺的組件,它依賴于從外部(模擬)世界收集信息進行(數字)處理。這些系統的應用范圍各不相同,從通信接收器到電子測試和測量,再到軍事和航空航天,僅舉幾例。硅處理技術(如65納米CMOS和28納米CMOS)的進步使高速ADC能夠跨越GSPS(每秒千兆采樣)障礙。這為系統設計人員提供了對越來越寬的帶寬進行采樣以進行數字處理的能力。出于環境和成本原因,系統設計人員不斷嘗試降低總功耗。傳統上,ADC制造商推薦使用低噪聲LDO(低壓差)穩壓器為GSPS(或RF采樣)ADC供電,以實現最大性能。但是,這不是高效的供電網絡 (PDN) 實現。系統設計人員越來越要求使用開關電源穩壓器直接為 GSPS ADC 供電,而不會顯著降低 ADC 性能。

解決方案在于仔細的PDN實現和布局,以確保ADC性能不會受到影響。本文討論了線性電源和開關電源之間的區別,并演示了將GSPS ADC與DC-DC轉換器結合使用可以顯著提高系統電源效率,而不會對ADC性能造成任何影響。本文討論了使用供電網絡組合的GSPS ADC的性能,并對成本和性能進行了比較分析。

傳統上推薦用于 GSPS ADC 的 PDN

高帶寬、高采樣速率ADC(或GSPS ADC)可以有多個電源域(如AVDD或DVDD)。隨著幾何尺寸的縮小,不僅電源域的數量增加了,而且為ADC供電所需的不同電壓的數量也增加了。例如,AD9250,114位、170 MSPS/250 MSPS,雙通道模數轉換器JESD204B,采用180 nm CMOS工藝構建,具有三個域:AVDD、DVDD和DRVDD。但是,所有三個域的電壓相同:1.8 V。

現在考慮AD9680,214位、1.25 GSPS/1 GSPS/820 MSPS/500 MSPS JESD204B雙通道模數轉換器,采用65 nm CMOS工藝。這款GSPS ADC具有七個不同的域(AVDD1、AVDD1_SR、AVDD2、AVDD3、DVDD、DRVDD和SPIVDD)和三種不同的電壓:1.25 V、2.5 V和3.3 V。

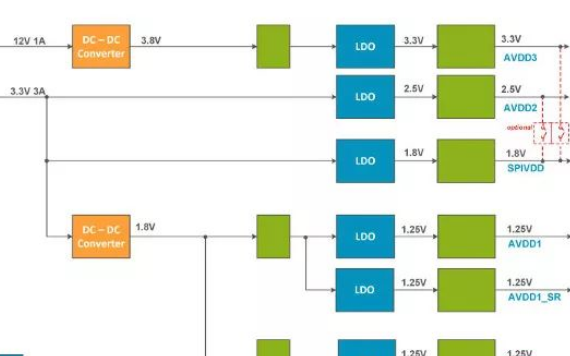

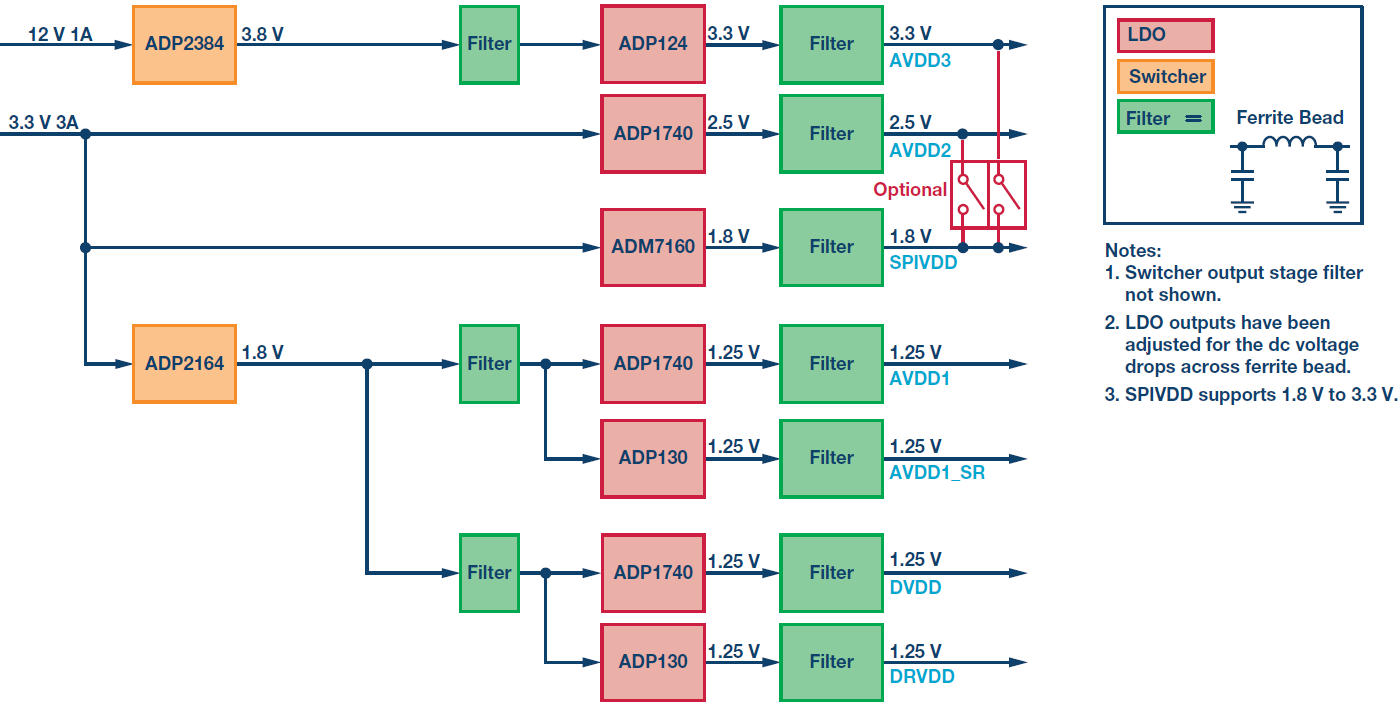

這些電源域和各種電壓的擴散對于在這些采樣速率下工作是必要的。它們需要確保各種電路域(如采樣、時鐘、數字和串行器)之間的適當隔離,同時提供最佳性能。正是出于這個原因,ADC制造商設計了評估板,并推薦了精心設計的電源設計,以確保最小的風險和最大的性能。例如,圖1顯示了AD9680評估板中使用的默認PDN的框圖表示。電源輸入來自采用 Vita12.1 規范的 FMC(FPGA 夾層卡)連接器提供的 3 V/3 A 和 3.57 V/1 A 電源。ADP23843和ADP21644DC-DC轉換器用于將電壓降壓至可管理的水平,因此LDO無需進入熱關斷狀態即可進行調節。

圖1.AD9680評估板的默認PDN。

無需太多時間就能意識到這是一個昂貴的實施方案,有七個LDO穩壓器,每個域一個。就性能而言,此 PDN 可能是最佳的,但就運營成本而言,它肯定不是最具成本效益或效率的。系統設計人員發現,實現具有多個ADC的系統具有挑戰性。例如,相控陣雷達方案將包含數百個AD9680同步工作。要求系統設計人員在數百個ADC的每個電壓域使用一個LDO穩壓器是不合理的。

用于 GSPS 模數轉換器的更簡單的 PDN

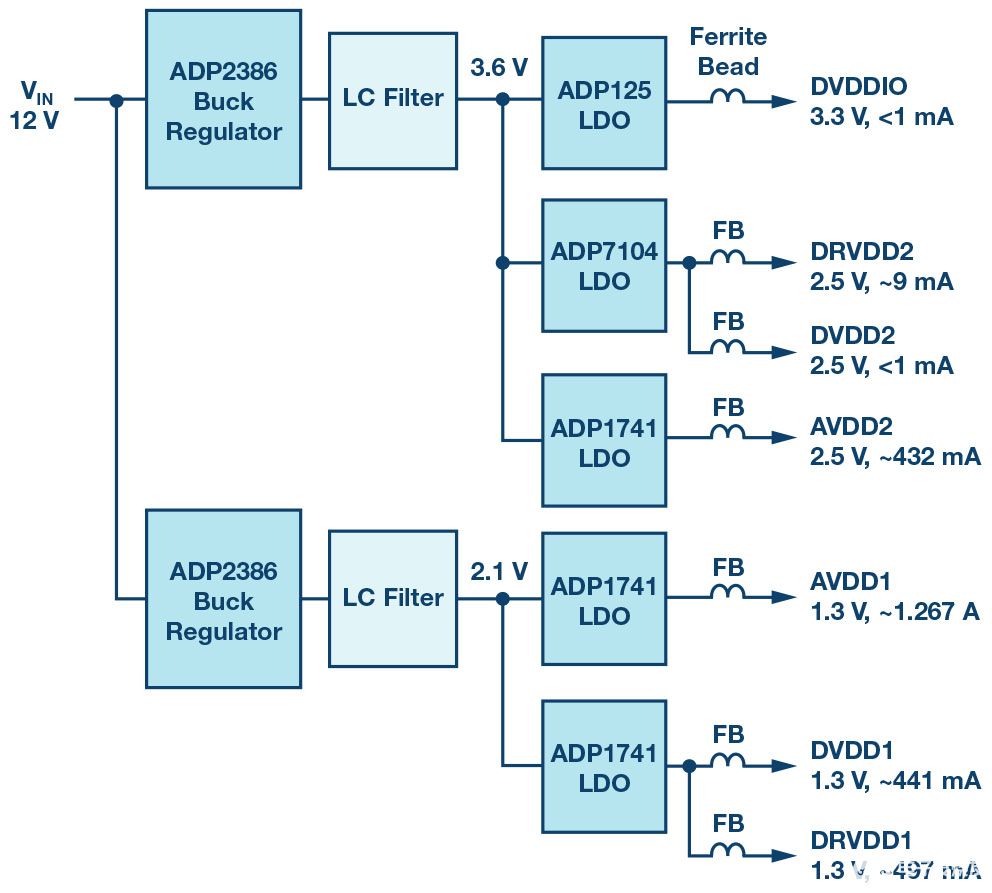

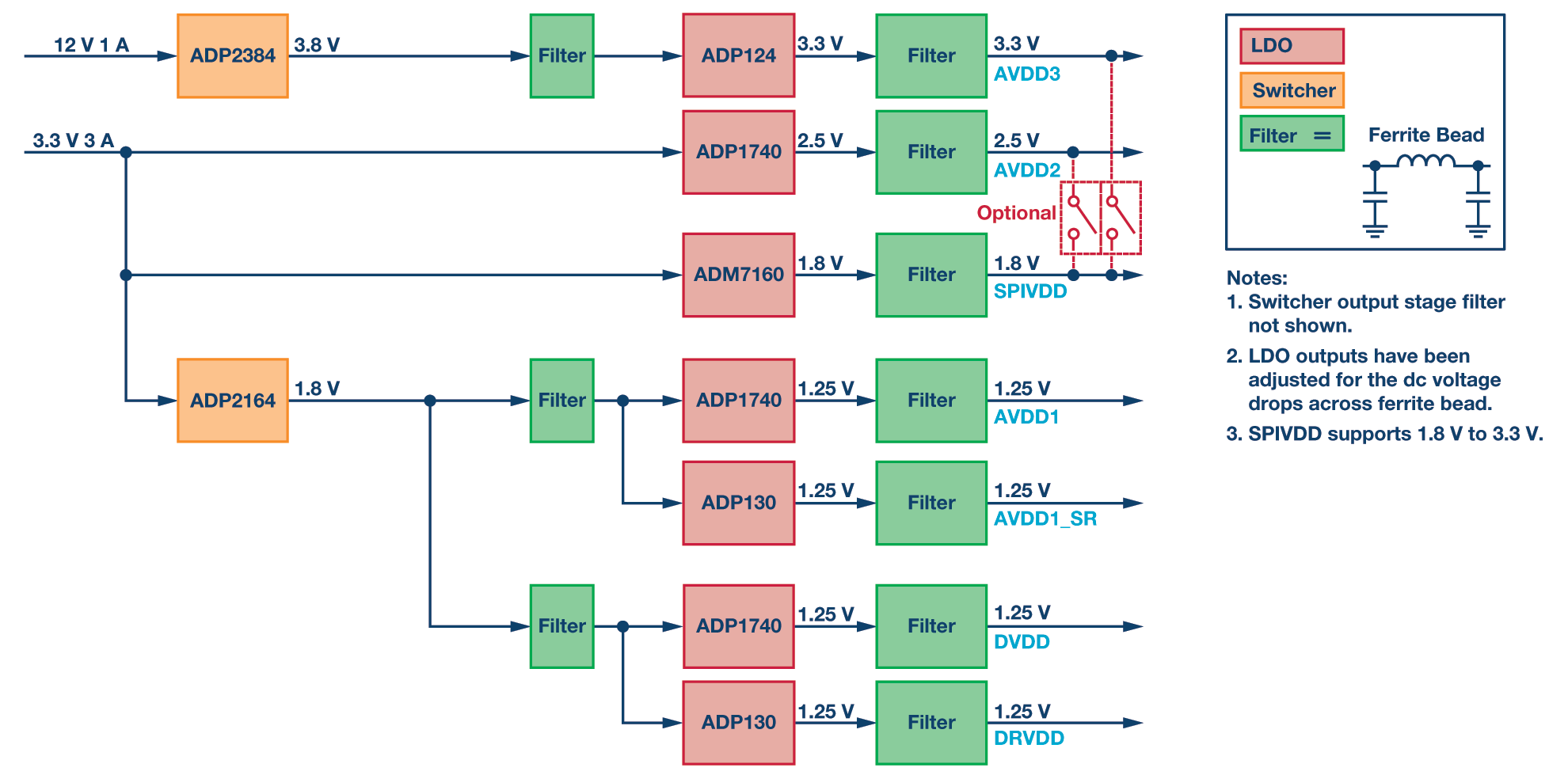

PDN 設計的一種更具成本效益的方法是組合具有相同電壓值的域(例如所有具有 1.25 V 模擬域的域),并從同一 LDO 驅動它們。這減少了元件數量(和物料清單 - BOM 成本),并且可能適用于某些設計。簡化的PDN如圖2所示,在AD9680評估板上實現。在此實現中,整個AD9680可以使用3.3 V單輸入供電。

圖 2:AD9680 評估板的簡化 PDN。

驅動AD9680的DC-DC轉換器

通過完全移除為1.25 V域供電的LDO,可以進一步簡化PDN。這將是最有效和最具成本效益的解決方案。這里的挑戰是確保DC-DC轉換器穩定運行,從而不影響ADC的性能。ADP2164驅動AD1的所有25.1 V域(AVDD1、AVDD9680_SR、DVDD和DRVDD)的PDN如圖3所示。

圖 3:使用 DC-DC 轉換器為 AD9680 供電。

比較各種 PDN

上面討論的三個PDN與第四個網絡一起進行測試,其中AD9680評估板由臺式電源供電。表1列出了AD9680評估板上實現的各種供電網絡。

表 1.供電網絡列表

|

PDN 設置 |

描述 | ||

| 板凳 | AD9680使用臺式電源運行 | ||

| PDN #1 |

評估板上的默認 PDN (如圖 1 所示) |

||

| PDN #2 |

所有1.25 V域均由一個LDO驅動 (如圖 2 所示) |

||

| PDN #3 | 所有1.25 V域均由DC-DC轉換器驅動(如圖3所示) | ||

由于SPIVDD可以支持1.8 V至3.3 V,并且被認為是非關鍵節點,因此它使用1.8 V LDO輸出供電。在常規系統實現中,SPIVDD可以連接到2.5 V或3.3 V域。也就是說,在許多ADC和DAC之間共享SPI總線的系統中,仍應監控SPIVDD連接。如果是這種情況,必須注意確保正常的SPI操作不會導致SPIVDD域上的電源瞬變。如果SPIVDD低于閾值電平,它們的電源瞬變可能會觸發上電復位(POR)情況。

表 2.信噪比性能比較

| 頻率(兆赫) | 板凳 | 默認值 (PDN #1) | 簡化 (PDN #2) | 切換臺 (PDN #3) |

|

63 |

66.5 |

66.5 |

66.6 |

66.7 |

|

170 |

66.4 | 66.1 | 65.9 | 66.2 |

| 340 | 64.8 |

64.5 |

64.5 | 64.7 |

| 450 | 64.0 | 63.7 | 63.6 | 63.8 |

| 765 | 62.5 | 62.2 | 62.2 | 62.3 |

| 985 | 61.3 |

61.0 |

61.0 | 61.1 |

|

1283 |

59.8 |

59.5 |

59.5 | 59.5 |

| 1725 | 57.7 | 57.4 | 57.4 | 57.5 |

| 1983 | 56.7 | 56.4 | 56.5 | 56.6 |

表 3.SFDR 性能比較 (dBFS)

| 頻率(兆赫) | 板凳 | 默認值 (PDN #1) | 簡化 (PDN #2) | 切換臺 (PDN #3) |

|

63 |

83 |

82 |

88 |

83 |

|

170 |

86 | 85 | 85 | 84 |

| 340 | 77 |

76 |

76 | 76 |

| 450 | 72 | 72 | 71 | 71 |

| 765 | 77 | 76 | 76 | 82 |

| 985 | 77 |

76 |

76 | 83 |

|

1283 |

74 |

74 |

74 | 75 |

| 1725 | 67 | 67 | 68 | 67 |

| 1983 | 60 | 60 | 60 | 60 |

表2和表3分別顯示了AD9680使用各種PDN時的SNR和SFDR性能。根據AD9680數據手冊,遵循了各種奈奎斯特區域的前端網絡和寄存器設置建議。2

僅使用DC-DC轉換器為AD9680的1.25 V域(PDN #3)供電的PDN在輸入頻率范圍內表現出良好的性能。這證明,可以組合域并高效、經濟地為其供電,而不會對ADC性能造成巨大損失。工作臺提供的 PDN 是噪聲最低的電源,可提供最佳的噪聲性能。但是,值得注意的是,PDN #3 始終比默認網絡 (PDN #1) 表現出更好的 SNR 性能。這可能是由于LDO適用于低頻清理,但即使在電路中,在超過100 kHz的頻率上也不會做太多事情。這可以解釋使用 PDN #0 時 SNR 的 2.3 dB 優勢。

FFT 圖

圖4和圖5分別顯示了170 MHz和785 MHz輸入時的單音FFT。FFT沒有顯示頻譜衰減,因為1.25 V域由單個DC-DC轉換器供電。

圖4.170 MHz 輸入時的單音 FFT,帶 PDN #3。

圖5.785 MHz 輸入時的單音 FFT,帶 PDN #3。

開關雜散

除了噪聲性能外,還應檢查DC-DC轉換器方案是否由于涉及開關元件和磁性元件而產生雜散成分。這就是減少接地環路和地面反彈的仔細布局技術將有益的地方。有許多資源可以幫助測量開關電源噪聲。5,6邊帶雜散出現在開關頻率(在本例中為1.2 MHz)的基波偏移的任一側。必須注意的是,圖2或圖3所示的輸出濾波器級是一個兩級濾波器。該兩級濾波器是降低開關噪聲(紋波)的主要因素,有助于改善ADC噪聲(SNR)性能。同樣,兩級濾波器還有助于減少輸出FFT中出現的開關雜散。圖6和圖7分別顯示了170 MHz和785 MHz的這些頻率。

圖6.1.2 MHz 邊帶開關雜散,輸入頻率為 170 MHz。雜散水平 = –105 dBFS。

圖7.1.2 MHz 邊帶開關雜散,輸入頻率為 785 MHz。雜散水平 = –94 dBFS。

邊帶雜散的電平可以通過了解PSRR(電源抑制比)或ADC的電源域來估算。7

模擬DC-DC轉換器開關電路

DC-DC轉換器輸出端的兩級濾波器可以使用ADIsimPE等工具進行仿真。8圖8顯示了為仿真PDN的輸出噪聲和穩定性特性而生成的ADIsimPE原理圖。ADIsimPE是一款方便而強大的工具,可幫助系統工程師設計、優化和分析電源網絡。

圖8.驅動2164.1 V域的ADP25的ADIsimPE原理圖。

圖9顯示了在ADIsimPE中仿真的第一級輸出和電路第二級之后的濾波輸出。此處所示的紋波約為3 mV p-p。

圖9.ADIsimPE仿真的第1級和第2級輸出。

物料清單

表4顯示了AD9680評估板簡化PDN的物料清單,如圖2所示。通過使用圖 3 所示的網絡,系統設計人員可以節省高達 40% 到 45% 的 BOM 成本。BOM 成本是通過計算流行的電子元件供應商網站上的組件的 1k 單價來估算的。

表 4.PDN 物料清單如圖 2 所示

| REFDES | 數量 | 描述 |

制造 |

部件號 |

價值 |

|

C1 |

1 | 22 μF、6.3 V、X5R 0805 電容器 |

村田 制作所 |

GRM21BR60J226ME39L |

22 微法 |

|

C2 |

4 | 22 μF、6.3 V、X5R 0805 電容器 |

村田 制作所 |

GRM21BR60J226ME39L |

22 微法 |

| Cf | 1 | 0.1 μF、10 V、X5R 0402 電容 | 村田制作所 |

GRM155R61A104KA01D |

0.1 μF |

| C3, C4, C5, C6, C7, C8, C9, C10, C11, C12, C13, C14, C15, C16, C17, C18, C19 | 17 | 4.7 μF、6.3 V、X5R 0402 電容器 |

村田 制作所 |

GRM155R60J475ME47D | 4.7 μF |

| E1, E2, E3, E4, E5, E6 | 6 | 鐵氧體芯片 10 Ω 0402 | 村田制作所 | BLM15AX100SN1D | 10 Ω |

| L1 | 1 | 1.0 μH屏蔽功率電感器,10 mΩ | 線藝 | XAL5030-102ME | 1.0微小時 |

| L2 | 1 | 2.2 μH屏蔽功率電感器,0.1 Ω | 線藝 | ME3220-222ML | 2.2微小時 |

| Rf1 | 1 | 4.99 kΩ, 1% 1, W/10 W 0402 電阻 | 松下 | ERJ-2RKF4991X | 4.99 千分電阻 |

| Rf2 | 1 | 41.2 kΩ, 1% 1, W/10 W 0402 電阻 | 松下 | ERJ-2RKF4122X | 41.2 千分電阻 |

| Rb | 1 | 23.2 kΩ, 1% 1, W/10 W 0402 電阻 | 松下 | ERJ-2RKF2322X | 23.2 千分電阻 |

| ADP2164 | 1 | IC, REG, 降壓調節, 4 A, 同步, 16 引腳 LFCSP | ADI公司 | ADP2164ACPZ-R7 | |

| ADP1741 | 3 | 集成電路、注冊、線性控制、調整后、2 A、16 引腳 LFCSP | ADI公司 | ADP1741ACPZ-R7 | |

| ADP171 | 2 |

集成電路、正控、線性穩壓、調整、0.3 A、5 引腳 TSOT-23 |

ADI公司 | ADP171AUJZ-R7 |

組件選擇和布局

ADC 在各種 PDN 上運行時的性能不僅取決于精心設計,還取決于組件的選擇及其在 PCB 上的布局。開關電源中產生的高電流通常會導致強磁場,這些磁場會耦合到電路板上的其他磁性元件中,包括匹配網絡中的電感器和用于耦合模擬和時鐘信號的變壓器。必須采用謹慎的電路板布局技術,以防止這些磁場耦合到關鍵信號中。

電感器選擇

由于構成輸出濾波級的電感和電容器執行大部分功率傳輸,因此需要仔細選擇它們。在本例中,混合使用了屏蔽和非屏蔽電感。第一濾波級使用屏蔽電感。在這種情況下,第二級可以使用非屏蔽電感。但是,建議在兩級都使用屏蔽電感,以最大程度地減少可能的EMI輻射。電感器還被選擇在飽和電流(ISAT)和直流電阻(DCR)方面具有足夠的裕量,以確保它們不會進入飽和或導致自身電壓降過大。

電容器選擇

建議使用 X5R 或 X7R 電容器作為輸出濾波電容器。電容器還必須具有低ESR(等效串聯電阻)。低 ESR 有助于降低輸出端的開關紋波。另一個使總ESR和ESI(等效串聯電感)最小化的技巧是將電容器并聯組合在一起。如圖3和表4所示,第一濾波級使用2×22 μF電容,而第二濾波級使用4× 22 μF電容。電容器的額定電壓也是其選擇的重要因素。這是因為陶瓷電容器的電介質隨著直流偏置的增加而降低。這意味著,在6 V直流偏置下,額定電壓為3.22 V的50 μF電容可能會降低高達4%的電壓9,10。 在本例中,額定電壓為6.3 V的電容用于1.25 V電源。在輸出端增加更多電容確實會略微增加BOM成本和電路板空間,但這可以很好地防止開關噪聲和紋波干擾ADC性能。

鐵氧體磁珠選擇

如圖3所示,鐵氧體磁珠用于隔離各種域。鐵氧體磁珠的選擇也至關重要,因為鐵氧體磁珠高于所需的DCR(直流電阻)將導致域電壓低于最佳電壓。這種低電壓導致ADC性能(SNR和SFDR)低于最佳性能。必須充分注意鐵氧體磁珠的阻抗特性、最大直流承載能力和DCR。11

PCB 布局注意事項

為了盡量減少開關穩壓器和ADC之間的相互作用,DC-DC轉換器及其開關元件應遠離與ADC相互作用的任何磁性元件(例如前端匹配網絡或時鐘網絡)。在DC-DC轉換器布局中,兩級濾波器應盡可能靠近DC-DC轉換器放置,以最小化環路電流。

結論

RF采樣(或GSPS)ADC允許對寬帶寬進行數字化,從而在系統設計中具有獨特的優勢。業界熱衷于降低這些GSPS ADC電源設計的復雜性、尺寸和成本。通過充分注意設計、元件選擇和 PCN 布局,可以擁有低噪聲且具有成本效益的 PDN,從而為 GSPS ADC 供電。通過實施,開關穩壓器還有助于提高電源系統效率,并提供運營成本和BOM節省,而不會對性能造成任何影響。

審核編輯:郭婷

-

轉換器

+關注

關注

27文章

8703瀏覽量

147182 -

穩壓器

+關注

關注

24文章

4235瀏覽量

93809 -

DC-DC

+關注

關注

30文章

1948瀏覽量

81671

發布評論請先 登錄

相關推薦

通過輸電網絡合探討GSPS ADC性能

RF采樣ADC 可對寬帶寬進行數字化處理

如何利用開關穩壓器為GSPS ADC供電

DC–DC轉換器為GSPS ADC提供高效輸電網絡

DC1818A配置為使開關穩壓器提供也為LDO供電的輸出

靜音開關穩壓器μ模塊穩壓器可為GSPS采樣ADC供電

為GSPS或RF采樣ADC供電:開關穩壓器與LDO

為GSPS或RF采樣ADC供電:開關穩壓器與LDO

Silent Switcher μModule穩壓器為GSPS采樣 ADC提供低噪聲供電

ADC12D1800RF一款RF采樣GSPS ADC數據表

ADC12D1x00RF 12位、3.2 GSPS和2 GSPS RF采樣ADC數據表

為GSPS或RF采樣ADC供電:開關穩壓器與LDO

為GSPS或RF采樣ADC供電:開關穩壓器與LDO

評論