《道德經》里說“圖難于其易,為大于其細。天下難事,必作于易;天下大事必作于細。”其實芯片也是這樣,要做大,先做小,這里的從小做起不僅是指器件建模、RTL描述或IP實現,還包括以真正的“芯粒”組合來搭建大芯片。

在當前先進工藝開發的大型SoC中,根據主要功能劃分出計算、存儲、接口等不同模塊,每個模塊選擇最合適的工藝制造完成后,再通過封裝技術組合在一起,已經成為了一種常見選擇。這種“硬核拼搭”的樂高積木式開發方法,可以有效化解集成度持續提高帶來的風險,例如良率面積限制、開發成本過高等問題,因而逐漸成為行業發展的熱點方向。

小芯片之間如何拼接,成為多晶片系統(Multi Die System)設計方法學實現的關鍵。在多晶片系統(Multi Die System)出現的早期,由于技術新穎,都是各廠商自己摸索,采用自有技術實現不同小芯片之間的連接。但各家都是自研接口技術,不僅重復開發工作繁重,而且也難以真正發揮多晶片系統(Multi Die System)的效力,如果能夠將芯粒的接口技術標準化,則不僅可以加速推廣多晶片系統(Multi Die System)技術,減少重復開發工作量,也可以打破廠商界限,將不同供應商的芯粒組合在一起,從而進一步提高資源利用率和開發效率,最終圍繞芯粒建立一個大型的生態系統。

正當其時的UCIe

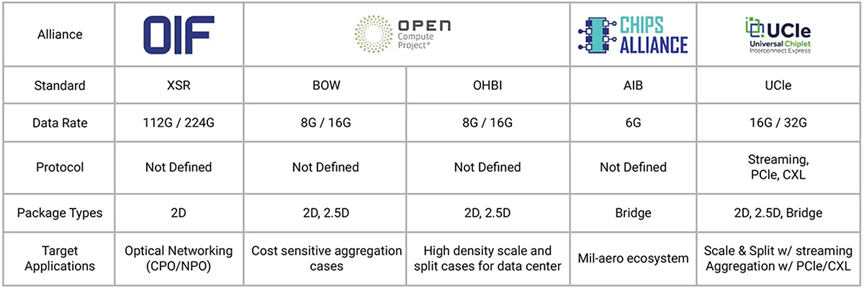

近年來,已有不同的行業組織提出了適用于多晶片系統的芯粒間(Die-to-Die)互連技術規格,而通用芯粒互連標準UCIe(Universal Chiplet Interconnect Express)在2022年3月發布,作為較晚出現的技術標準,UCIe不僅獲得了半導體生態鏈上各主要廠商的支持,也是到目前為止,技術規范定義最完整的一個標準。

圖片來源:新思科技

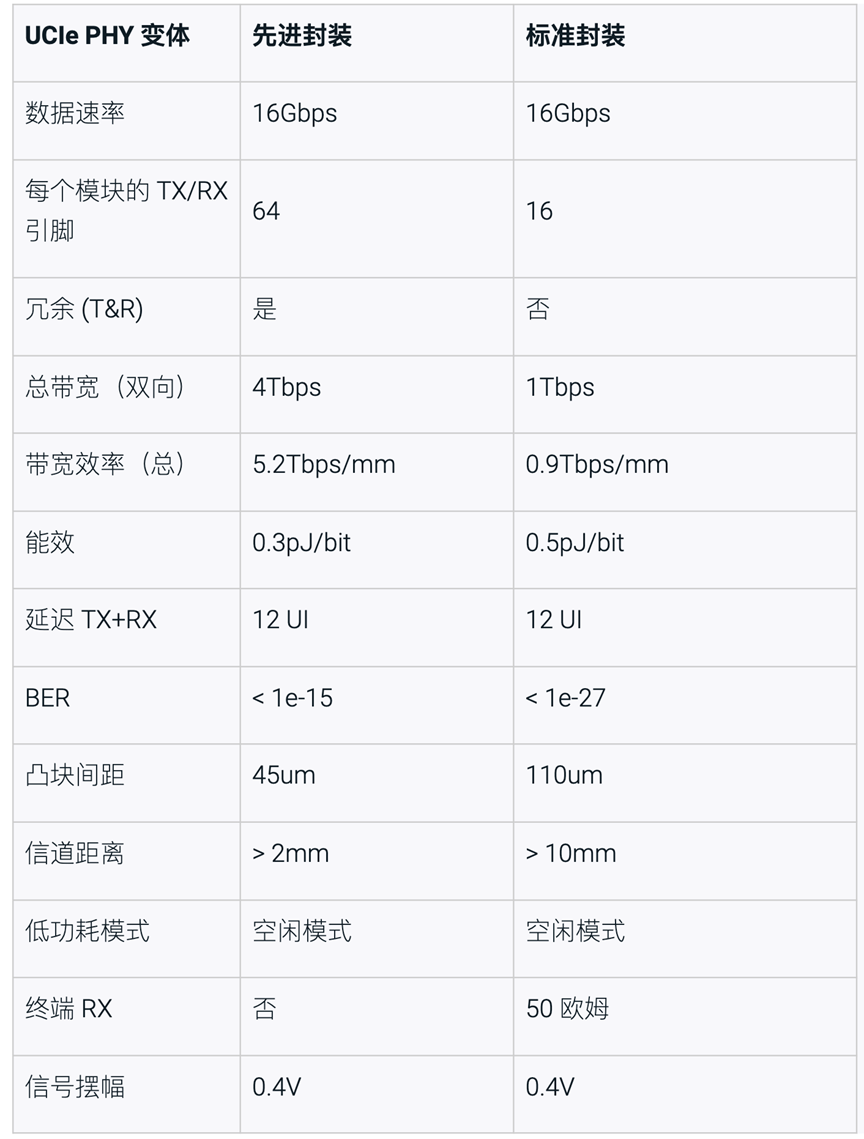

從UCIe聯盟公布的白皮書來看,UCIe 1.0標準支持即插即用,在協議層支持PCIe或CXL等成熟技術,也支持用戶自定義的流式傳輸,兼具普適性與靈活性;在協議上,UCIe定義了完整的芯粒間互連堆棧,確保了支持UCIe技術的芯粒相互之間的互操作性,這是實現多裸片系統的前提條件;雖然是為芯粒技術定制,但UCIe既支持封裝內集成,也支持封裝間互連,可用于數據中心等大型系統設備間的互連組裝;對封裝內互連,UCIe既支持成本優先的普通封裝,也支持能效或性能優先的立體封裝。總而言之,得到了半導體及應用領域各環節核心廠商支持的UCIe,具備了成為普適技術的基礎。

不同封裝UCIe參數

UCIe規范概述

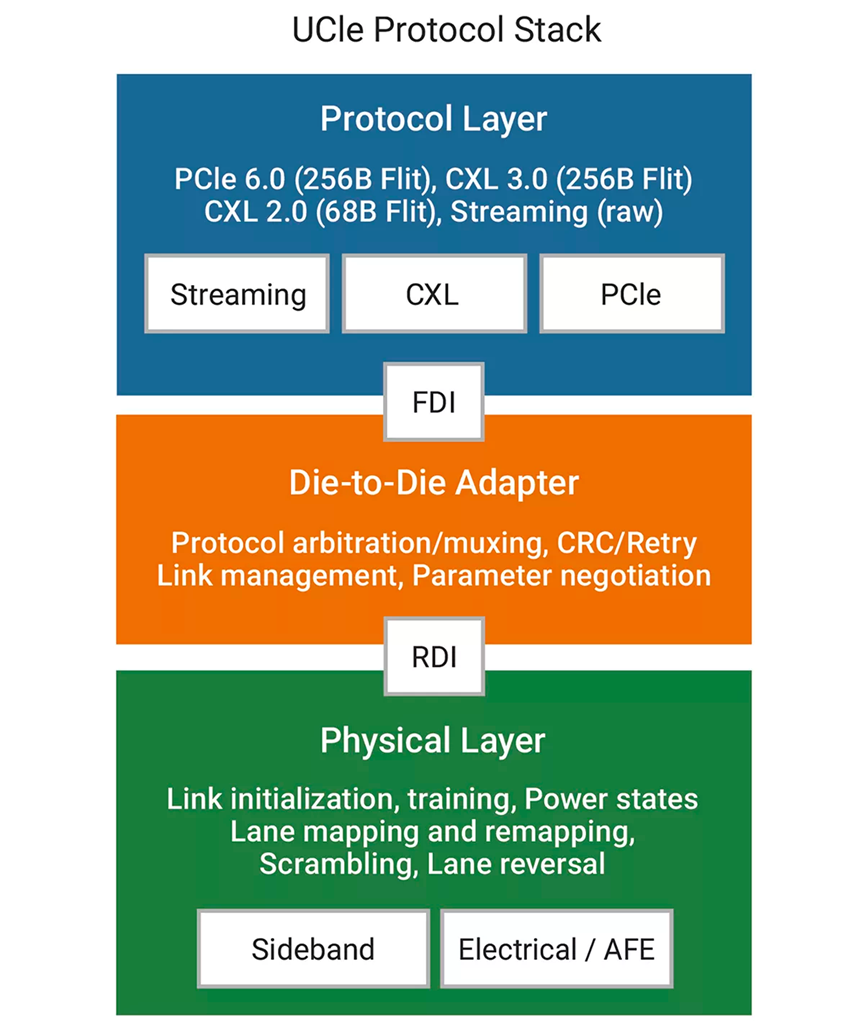

UCIe是一個三層協議。物理層負責電信號、時鐘、鏈路協商、邊帶等,芯粒適配器(Die-to-Die Adpater)層為提供鏈路狀態管理和參數控制,它可選地通過循環冗余校驗 (CRC) 和重試機制保證數據的可靠傳輸,UCIe接口通過這兩層與標準互連協議層相連。

其中,物理層是最底層,這一層是封裝介質的電氣接口。它包括電氣模擬前端AFE、發射器、接收器以及邊帶信道,可實現兩個裸片間的參數交換和協商。該層還具備邏輯PHY,可實現鏈路初始化、訓練和校準算法,以及通道的測試和修復功能。

芯粒適配器層負責鏈路管理功能以及協議仲裁和協商。它包括基于循環冗余校驗 CRC 和重試機制,以及可選的糾錯功能。

協議層可支持對一個或多個 UCIe 支持協議的實現。這些協議基于流控單元(Flit),用戶可根據需要選擇PCIe/CXL協議,也可以根據應用自定義流式傳輸協議。優化的協議層可為用戶提供更高的效率和更低的延遲。

能否統一封裝內互連技術?

芯粒間接口技術標準化,既可以為眾廠商提供技術發展路線圖做參考,又可以讓不同廠商生產的符合標準的芯粒自由組合,打破良率尺寸限制,建立起基于先進封裝技術的SoC開發新生態。

在當前已有的協議中,UCIe在協議完整性、支持廠商等方面都具有優勢,也具備進一步的發展空間,例如支持更高的數據速率和3D封裝等,只不過由于UCIe技術相對較新,要成功推廣,還需要產業鏈上核心廠商在IP、工具和制造等方面提供足夠的支持。

審核編輯:劉清

-

soc

+關注

關注

38文章

4196瀏覽量

218769 -

crc

+關注

關注

0文章

199瀏覽量

29514 -

晶片系統

+關注

關注

0文章

3瀏覽量

5662 -

UCIe

+關注

關注

0文章

48瀏覽量

1637

原文標題:為什么UCIe最適合多晶片系統 ?

文章出處:【微信號:bdtdsj,微信公眾號:中科院半導體所】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

UCIe能否統一多晶片系統封裝內互連技術?

UCIe能否統一多晶片系統封裝內互連技術?

評論