PCI Express (PCIe) 6.0規范實現了64GT/s鏈路速度,還帶來了包括帶寬翻倍在內的多項重大改變,這也為SoC設計帶來了諸多新變化和挑戰。對于HPC、AI和存儲SoC開發者來說,如何理解并應對這些變化帶來的設計挑戰變得至關重要。

本文將就上述問題和方案作詳細介紹及探討。

PCIe 6.0的重大新變化

變化一:PCIe 6.0電器性發生根本性的機制改變

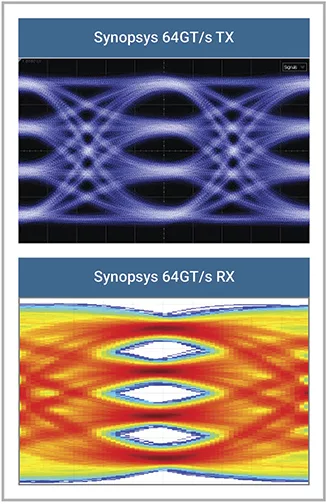

為了實現64GT/s的鏈路速度,PCIe 6.0采用脈沖幅度調制4級 (PAM4) 信號,在與32GT/s PCIe相同的單元間隔(UI)中提供4個幅度級別(2 位)。圖1顯示了三眼眼圖與此前的單眼眼圖的對比。

圖 1:與NRZ信號相比,PCIe 6.0 PAM-4信號是三眼眼圖

與NRZ相比,轉換到PAM4信號編碼引入了更高的誤碼率(BER)。為緩解這種情況,6.0規范在以 64GT/s 運行時實現了許多新功能。例如,當將新的4級電壓眼圖映射到數字值時,格雷編碼可以最小化每個 UI 內的錯誤,并且發送器應用預編碼來最小化迸發錯誤;PCIe 6.0還采用前向糾錯(FEC)機制來降低較高的誤碼率。這些對 PCIe 協議和控制器設計都具有重大影響。

變化二:新一代協議的引入

PCIe 6.0 引入了全新的“FLIT 模式”,其中數據包被組織在固定大小的流控制單元中,而不是過去規范版本中的可變大小。這種模式簡化了控制器級別的數據管理,帶來了更高的帶寬效率、更低的延遲和更小的控制器占用空間。當以 64GT/s 的速率運算時,FLIT 模式使用未編碼數據(稱為“1b1b 編碼”),而 128/130 編碼用于 8GT/s 至 32GT/s 的鏈路速度,經典8b10b編碼用于2.5GT/s 和 5GT/s 的鏈路速度。

與具有相同配置的 32GT/s PCIe 控制器相比,64GT/s PCIe 6.0 控制器所需的硅面積顯著增加;支持1b1b編碼不僅增加了第三物理層路徑(位于 8b10b 和 128b130b 頂部),還增加了數據鏈路層中的邏輯;FLIT模式中使用的新優化標頭,也進一步增加了邏輯門數,超過了 32GT/s 解決方案。

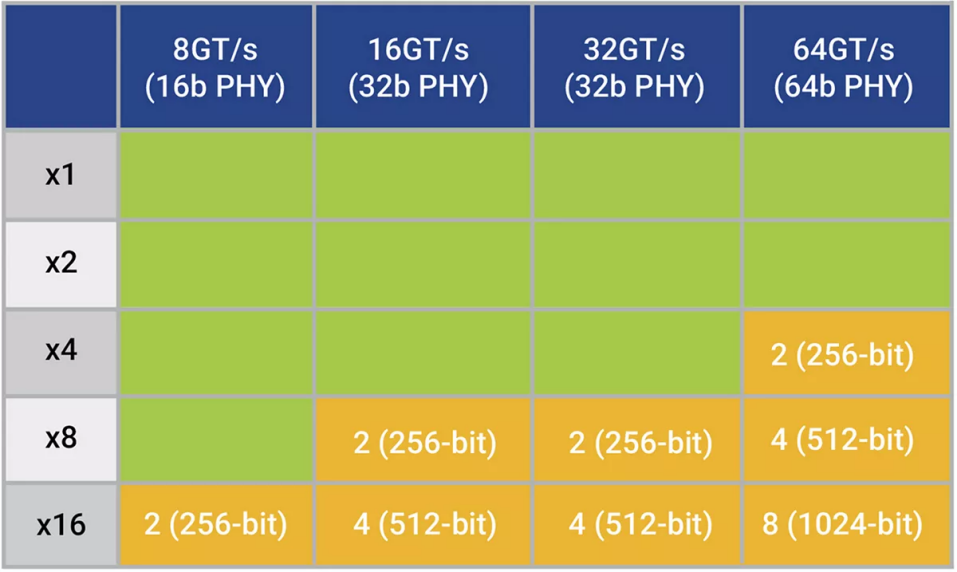

為了保持與上一代相同的最大時鐘頻率,64GT/s下PIPE數據路徑寬度增加了一倍,即需要1024位數據路徑的16通道設計,這為芯片設計帶來了新的問題。

要知道,大于128位的數據路徑寬度,可能會導致SoC需要在每個時鐘周期處理多個PCIe 數據包。最小的PCIe事務層數據包 (TLP) 可以被視為 3 個 DWORD(12 字節)加上 4 字節 LCRC,總共 16 個字節(128 位)。在 8GT/s 時,使用PCIe PHY的 500MHz 16 位 PIPE 接口最為常見,這意味著8通道及以下(16 位/通道 * 8 通道 = 128 位)的鏈路寬度會在每個時鐘最多傳輸一個完整的數據包。但是,16通道(16位/通道 * 16通道 = 256位)在每個時鐘周期就需要傳輸兩個完整的數據包。

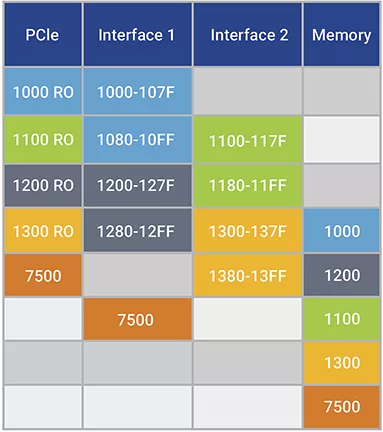

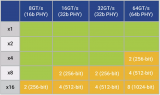

如表1顯示,隨著鏈路速度的提高,每個時鐘的完整數據包的數量相應增加,從而影響越來越多的設計。

表 1:數據路徑寬度隨鏈路速度增加,導致更多配置超過128位閾值

PCIe 6.0的優化設計

1松弛排序

PCIe排序規則需要Posted事務,例如內存寫入保持有序,除非數據包標頭中設置了松弛排序 (RO) 或 ID 排序 (IDO) 屬性。使用RO集的Posted事務可以傳遞任何先前 Posted 事務,而使用IDO集的事務只能使用不同的請求者ID傳遞先前事務。

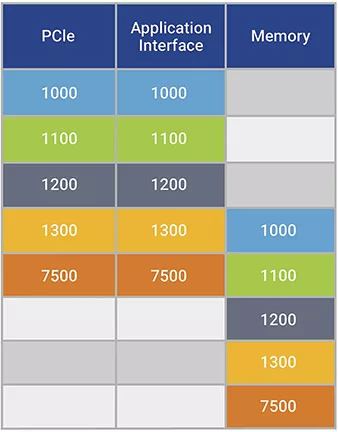

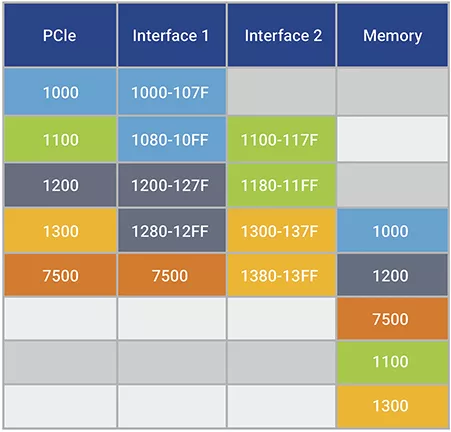

以下四個示例展示了這兩種屬性對于實現完整的PCIe 64GT/s 性能的重要性。他們均利用4個PCIe內存的序列寫入256字節中的每一個,表示將1KB 有效載荷遞送到地址1000,然后是4個字節的PCIe內存寫入,表示將“成功完成”指示遞送到地址7500。表中的每一行代表一個時間段,而三列(從左到右)表示事務到達PCIe引腳、應用程序接口和 SoC 內存。在所有 4 次內存寫入之前,“成功完成”指示到達內存的任何場景都反映出失敗,因為軟件在收到指示后立即可進行數據處理,因此在交付正確的數據之前處理。

示例1:只要其中一個應用程序接口的帶寬至少等于 PCIe 帶寬,該接口就可以正常工作。

表2:單一全速率應用程序接口可正確傳輸數據

示例2:雙接口通常會出現故障,因為無法保證SoC中兩個通往內存的獨立路徑之間的到達順序。

表3:顯示雙半速率應用程序接口失敗,原因是“成功完成”指示早于所有數據到達

示例3:將強排序流量強制到單個接口可避免出現無序到達,但由于無法使用全部內部帶寬,因此很快落后于 PCIe 鏈路。

表4:由于無法全速傳輸數據,所示的雙半速應用程序接口失敗

示例4:當鏈路伙伴把數據有效載荷數據包標記為 RO 且把成功完成數據包標記為強排序時,兩個半速率接口可以成功傳輸。請注意,當 RO 有效載荷數據無序到達時,非 RO 寫入 7500 不被允許傳遞有效載荷寫入,因此在發送所有先前寫入之前,不會將其發送到應用接口。

表 5:顯示雙半速應用程序接口通過對有效載荷數據使用松弛排序成功

SoC 設計人員可以在其出站數據流中設置RO屬性,并顯著提高PCIe鏈路性能。IDO排序屬性在許多情況下都具有類似的優勢,大多數 PCIe 實現都可以將其應用于其傳輸的每個數據包。

具有IDO集的數據包僅被允許傳輸具有不同請求者 ID 的先前事務,這意味著數據包來自 PCIe 鏈路上的不同邏輯代理。大多數端點實現(單功能和多功能)都對與往返于其他 PCIe 端點的流量相關的數據排序漠不關心,因為它們通常只與RC通信。同樣,大多數RC通常不會在多個端點之間混合相同的流量流,因此在這兩種情況下,都沒有與其他設備的請求者 ID 相關的排序問題。與此類似,大多數多功能端點對功能之間的數據排序也不關心,因此也不必擔心自己的請求者ID之間的排序。因此,大多數實施已經可以為他們發起的所有事務設置IDO。

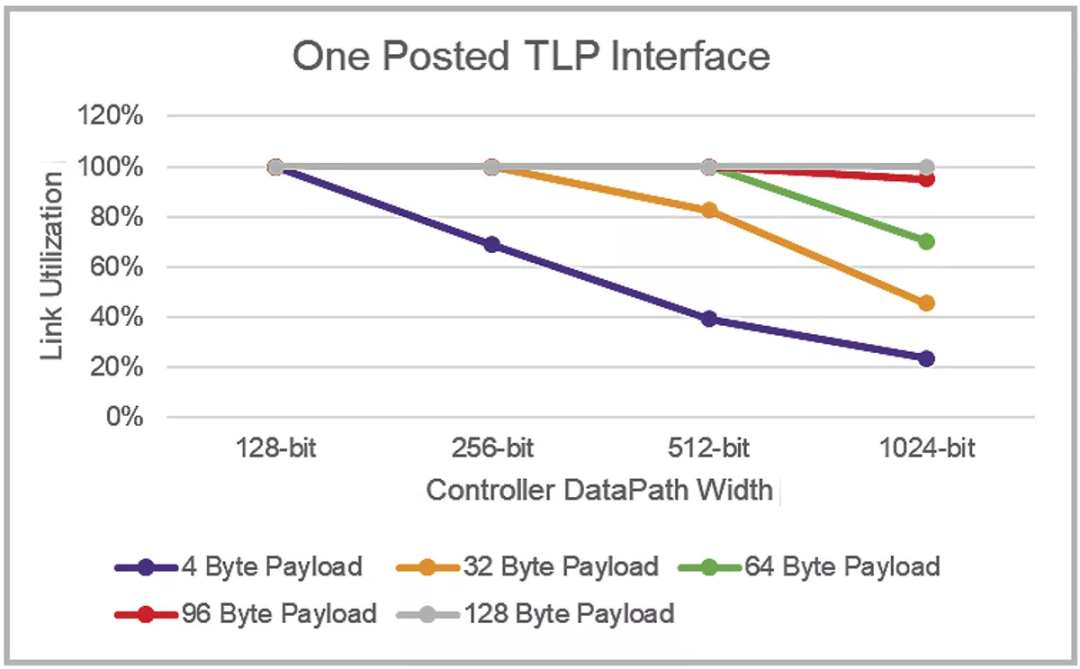

2增加應用程序接口

除了上文討論的因素外,當數據包小于接口寬度時,利用多個較窄的應用程序接口可顯著提高整體性能。圖 2 顯示了新思科技 PCI Express 6.0 控制器IP上64GT/s Flit模式下在發送連續的 Posted TLP流方面的傳輸鏈路利用率。對于更大的數據路徑寬度,顯然需要更大的數據包來通過單個應用程序接口保持完全的鏈路利用率,1024 位接口需要 128 字節的有效負載。

圖 2:在 64GT/s FLIT 模式下,利用單個應用程序接口進行傳輸的各種有效荷載大小和數據路徑寬度的鏈路利用率

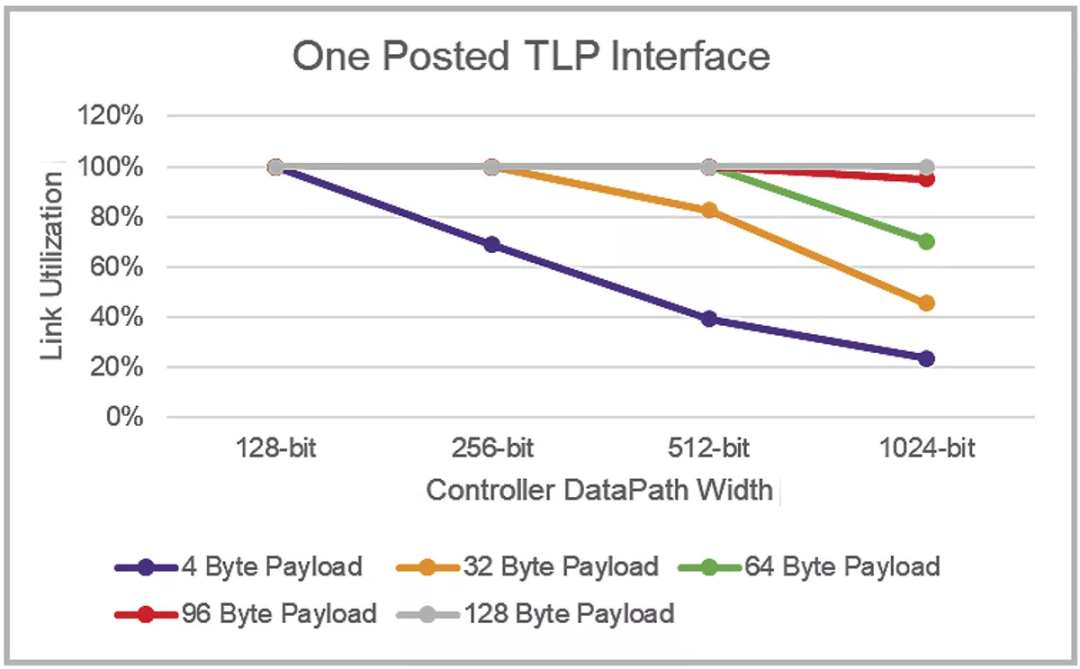

相反,當新思科技控制器配置為兩個應用接口并運行相同的流量模式時,就會有明顯的改進,現在64字節的有效負載即使在 1024 位數據路徑中也能產生完全的鏈路利用率,如圖 3 所示。

圖 3:在 64GT/s FLIT 模式下,通過兩個應用接口配置進行傳輸的各種有效載荷大小和數據路徑寬度的鏈路利用率

3解決小數據包效率低下

雖然大多數設備幾乎無法控制其流量模式,但小數據包可以實現更少帶寬。新思科技 CoreConsultant 使用最大有效負載大小和往返時間 (RTT) 等參數來配置 PCIe 6.0 控制器中的緩沖區大小、突出 PCIe 標簽數量和其他關鍵參數。

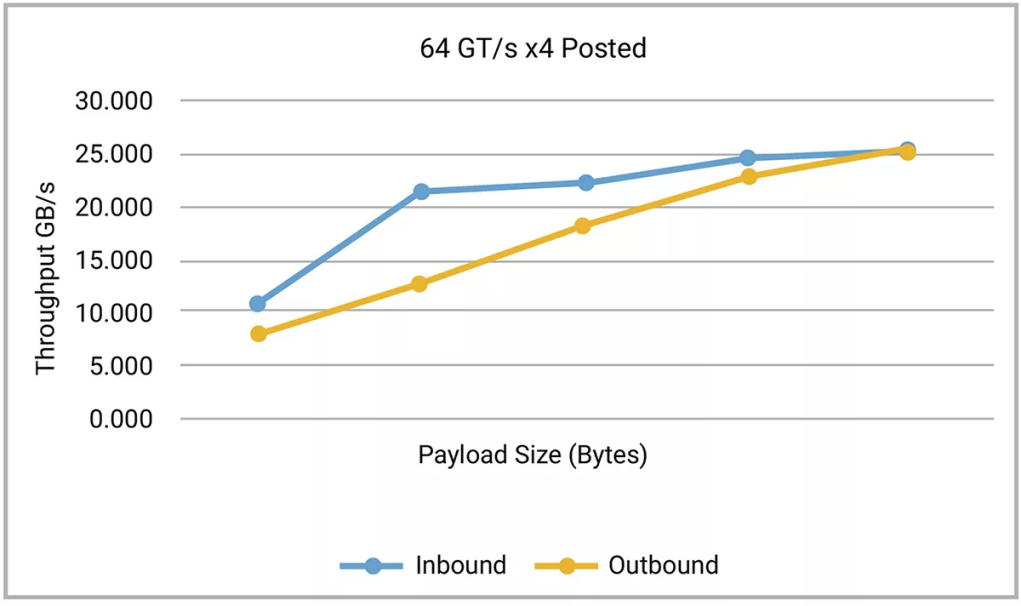

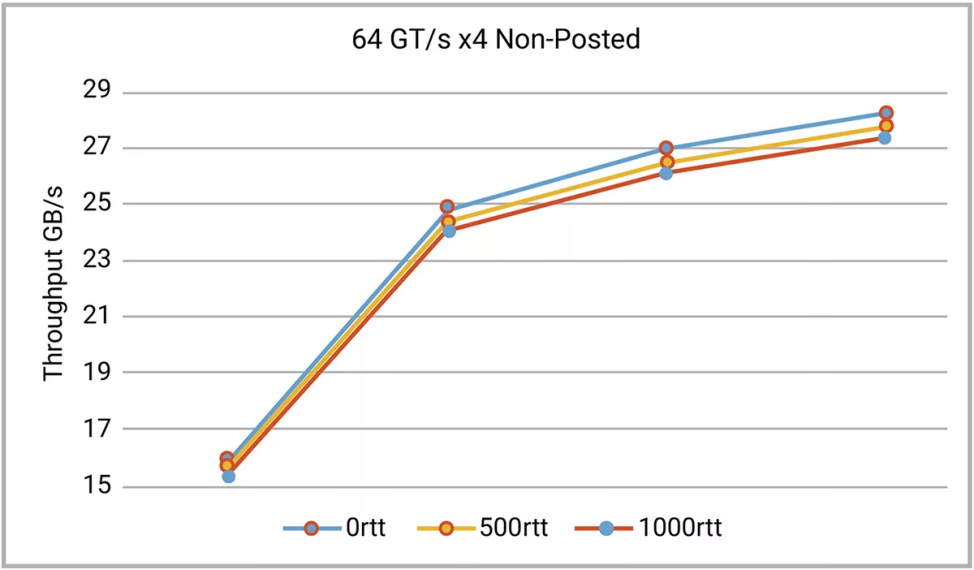

圖3和圖4顯示了從新思科技的 64GT/s x4 控制器的仿真中獲得的數據。該控制器配置為 512 字節最大有效載荷大小和 1000nS RTT 掃描,覆蓋一系列有效載荷大小和 RTT 值。如果在同一范圍內重復相同的掃描,但任意一個參數降低,則當掃描通過優化范圍后,性能會降低。

圖 3:小尺寸 Posted 數據包效率低下

圖 4:小尺寸Non-Posted數據包效率低下,在一系列往返時間范圍內掃描

總結

實施 64GT/s PCIe 接口的 SoC 設計人員應確保其支持松弛排序屬性,即有效載荷而非相關控制上的RO,以及所有數據包上的IDO,除非應用程序有異常要求。這是在整個 64GT/s 生態系統中實現高性能的關鍵部分。

為x4和更寬鏈路實施64GT/s PCIe的設計人員需要注意每個時鐘周期的多個數據包,并應根據其典型流量大小考慮多個應用接口。

所有64GT/s實施者都應為1GHz(或更快)的設計實現做好準備,并且應確保通過硅前性能模擬檢查其假設。

對于上述這些優化設計辦法,新思科技提供完整的PCIe 6.0解決方案(包括控制器、PHY 和 VIP)。這些解決方案支持松弛排序屬性、PAM-4 信號、FLIT 模式、L0p 電源、高達 1024 位的架構以及多個應用程序接口選項,有助于更輕松地過渡到64GT/s PCIe設計。

審核編輯:湯梓紅

-

芯片

+關注

關注

456文章

50889瀏覽量

424242 -

控制器

+關注

關注

112文章

16384瀏覽量

178337 -

soc

+關注

關注

38文章

4173瀏覽量

218404 -

芯片設計

+關注

關注

15文章

1021瀏覽量

54917 -

PCIe

+關注

關注

15文章

1241瀏覽量

82729

原文標題:如何破解PCIe 6.0帶來芯片設計新挑戰?

文章出處:【微信號:架構師技術聯盟,微信公眾號:架構師技術聯盟】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

PCIe 6.0元年,AI與HPC迎來新速度

綠色制造帶來多種挑戰 破解工藝成本難題

楷登電子發布PCIe 6.0規范Cadence IP

PCIe 6.0的新變化與新挑戰

PCIe 6.0規范及它是如何從過去的規范演變而來的

干貨:PCIE6.0技術剖析

面向高性能數據中心和人工智能SoC Rambus推出PCIe 6.0接口子系統

如何破解PCIe 6.0帶來的芯片設計新挑戰?

AI和數據中心:PCIe 6.0,你是懂加速的

PCIe 6.0的優化設計方案探討分析

新思科技PCIe 6.0 IP與英特爾PCIe 6.0測試芯片實現互操作

新思科技成功實現與英特爾PCIe 6.0測試芯片的互操作性

如何簡化PCIe 6.0交換機的設計

如何破解PCIe 6.0帶來芯片設計新挑戰?

如何破解PCIe 6.0帶來芯片設計新挑戰?

評論