在大多數情況下,隔離SPI非常簡單。這些線路都是單向的,使用標準的數字邏輯電平來存儲數據,并且沒有集電極開路輸出來支持電線和連接。只要速度相當適中,低于約5MHz時鐘速率,大多數數字隔離器就可以完成這項工作,而不會大驚小怪。不幸的是,隨著時鐘速率的增加,有一個限制速度的問題。

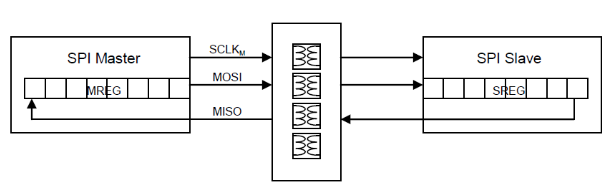

SPI的標準實現使用主器件生成的時鐘信號SCLKM來控制總線上的所有數據移動。數據在主站和從站之間移動,就好像它們是兩個相互連接的移位寄存器一樣。主站和從站將數據提供給時鐘一端的總線,并將數據讀入另一端的移位寄存器。只要通過總線的往返傳播延遲小于時鐘周期的一半,該系統就可以正常工作,因為數據必須在下一個時鐘邊沿,半個時鐘周期后返回主站。

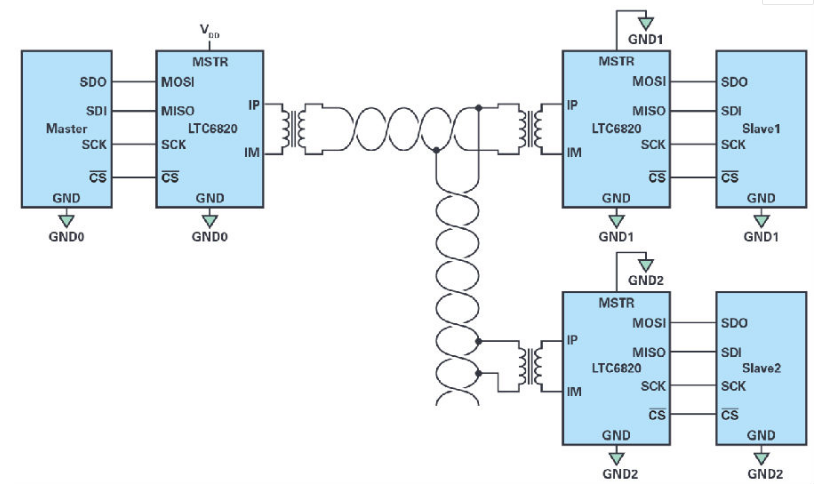

.

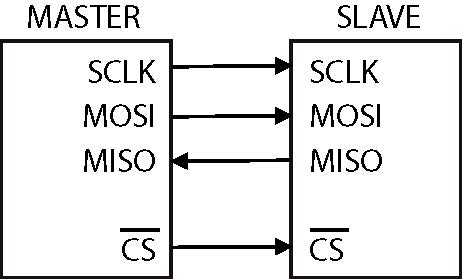

將隔離集成到SPI總線中會限制SCLKM速率,因為來自從器件的數據必須在下一個時鐘邊沿之前到達主設備。由于發生這種情況所需的最短時間是最大傳播延遲的 2 倍,因此這設置了時鐘速率的最大限制。

我們通常建議將ADuM1401C用于此工作,因為它的保證速度為45 MHz,最大傳播延遲為32 ns。當用于隔離SPI時,時鐘半周期必須大于2個傳播延遲,或最大SCLKM速率為7.8MHz。與數字隔離器的最大吞吐量相比,這是對數據速率的嚴重限制。事實上,數字隔離器需要小于5.5 ns的最大保證傳播延遲才能支持45 MHz SPI。

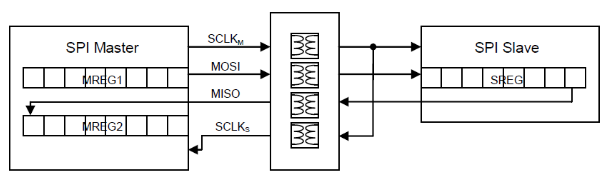

幸運的是,有一個直接的解決方案可以消除這個瓶頸。如果SCLKM信號與來自從器件的數據一起通過耦合器包裝回去,則新信號SCLKS和數據之間的時序與耦合器的傳播延遲偏斜相同。SCLKS可用于將數據時鐘回主站,其速率再次由耦合器的保證數據速率設置。在每個事務之后,輔助緩沖區 MREG2 被復制到 MREG1 在本例中,這將 SPI 時鐘速率提高到完整的 45MHZ,提高了 5 倍。該解決方案的成本是額外的耦合器通道來包裝主時鐘信號和主控制器中的額外輸入移位寄存器

推薦用于SPI應用的iCoupler器件是ADuM1401C和ADuM3441。使用這些器件可以實現高達 50 MHz 的數據速率。

審核編輯:郭婷

-

寄存器

+關注

關注

31文章

5355瀏覽量

120531 -

總線

+關注

關注

10文章

2888瀏覽量

88138 -

隔離器

+關注

關注

4文章

774瀏覽量

38341

發布評論請先 登錄

相關推薦

AD采集芯片SPI信號隔離,電源和地怎么接

用SPI總線實現DSP和MCU之間的高速通信

多種SPI總線隔離設計方案

為高速SPI通信添加穩健可靠的隔離

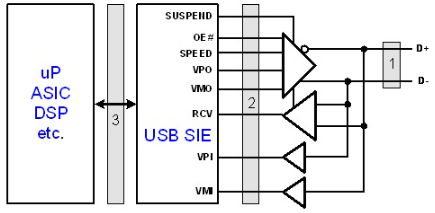

全速USB連接的光隔離研究

通過隔離實現快速SPI連接

通過隔離實現快速SPI連接

評論