本應用筆記描述了意法半導體開發的首款指令緩存(ICACHE)和數據緩存(DCACHE)。

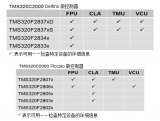

在 Arm Cortex-M33 處理器的 AHB 總線中引入的 ICACHE 和 DCACHE 嵌入到下表中列出的 STM32 微控制器(MCU)中。

這些緩存使用戶從內部和外部存儲器提取指令和數據時或在用于外部存儲器的數據流量時提高應用性能并降低功耗。本文檔提供了典型示例,以強調 ICACHE 和 DCACHE 功能,并便于配置。

1. ICACHE 和 DCACHE 概述

本節概述了嵌入在基于 STM32 Arm Cortex內核的微控制器中的 ICACHE 和 DCACHE 接口。詳細介紹了 ICACHE 和 DCACHE 框圖架構以及在系統架構中的集成。

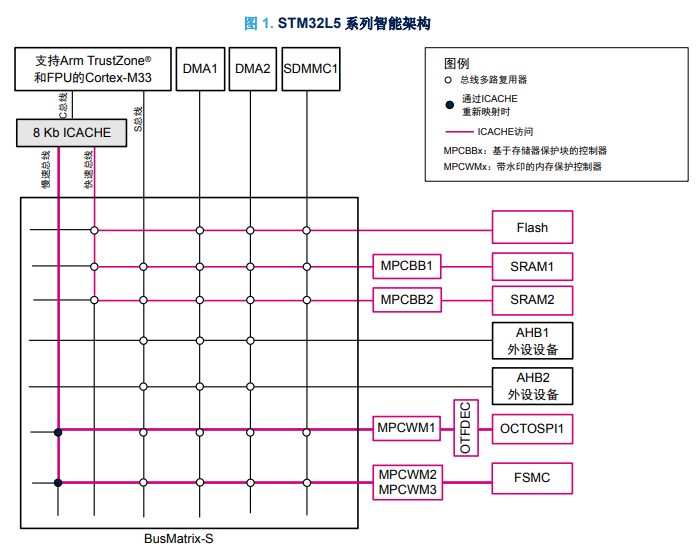

1.1 STM32L5 系列智能架構

此架構基于總線矩陣,允許多個主設備(Cortex-M33、DMA1/2 和 SDMMC1)訪問多個從設備(如Flash 存儲器、SRAM1/2、OCTOSPI1 或 FSMC)。

下圖描述了 STM32L5 系列智能架構。

由于將 8-Kb 的 ICACHE 接口引入其 C-AHB 總線,通過快速總線從內部存儲器(Flash 存儲器、SRAM1 或SRAM2)或通過慢速總線從外部存儲器(OCTOSPI1 或 FSMC)提取代碼或數據時,Cortex-M33 的性能有所提升。

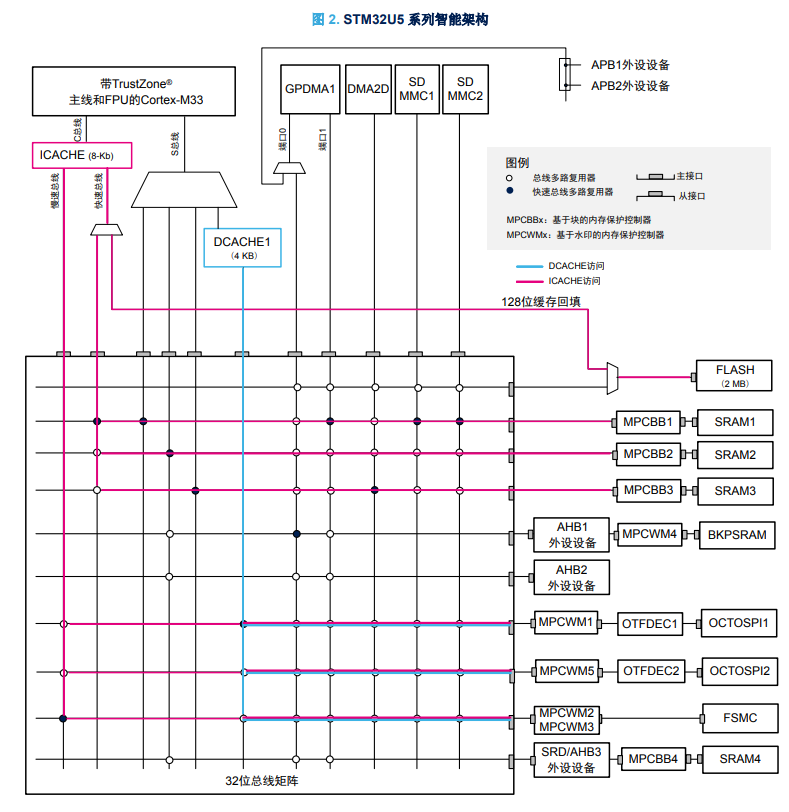

1.2 STM32U5 系列智能架構

此架構基于總線矩陣,允許多個主設備(Cortex-M33、GPDMA1、DMA2D 和SDMMC1/2)訪問多個從設備(如 Flash 存儲器、SRAM1/2/3/4、BKPSRAM、OCTOSPI1/2 或 FSMC)。

下圖描述了 STM32U5 系列智能架構。

其 C-AHB 總線引入了 8-Kb 的 ICACHE 接口,通過快速總線從內部存儲器(Flash 存儲器、SRAM1、SRAM2 或SRAM3)或通過慢速總線從外部存儲器(OCTOSPI1、OCTOSPI2 或 FSMC)提取代碼或數據時,Cortex-M33 的性能有所提升。其 S-AHB 總線引入了 4-Kb 的 DCACHE 接口,提高了外部存儲器(OCTOSPI1、OCTOSPI2 或 FSMC)的數據流量。

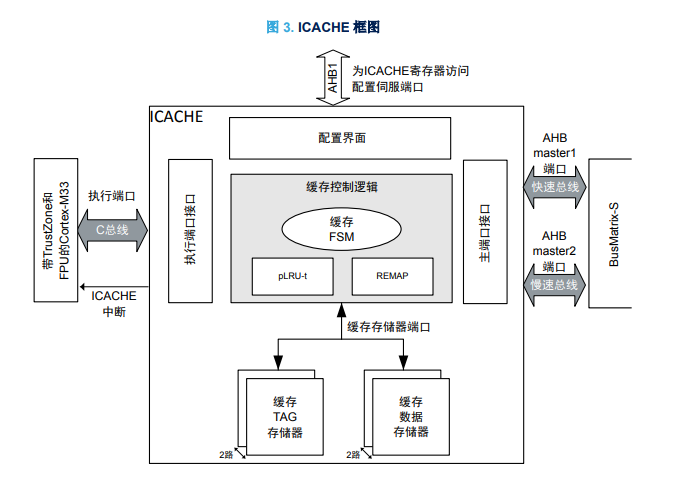

1.2 ICACHE 框圖

ICACHE 框圖如下圖所示:

ICACHE 存儲器包括:

? 具有以下元素的 TAG 存儲器:

– 指示將哪些數據包含在緩存數據存儲器中的地址標簽

– 有效位

? 數據存儲器,包含緩存的數據

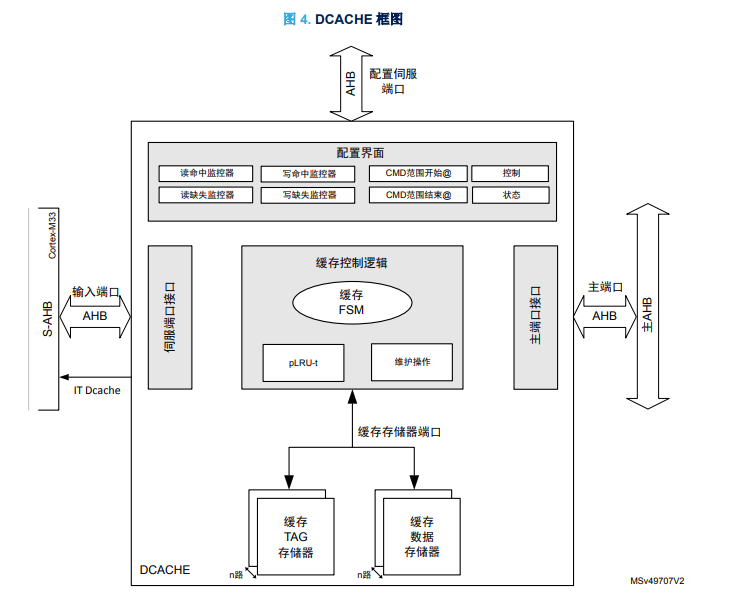

1.4DCACHE 框圖

DCACHE 框圖如下圖所示。

DCACHE 存儲器包括:

? 具有以下元素的 TAG 存儲器:

– 指示將哪些數據包含在緩存數據存儲器中的地址標簽

– 有效位 特權位

– dirty 位

? 數據存儲器,包含緩存的數據

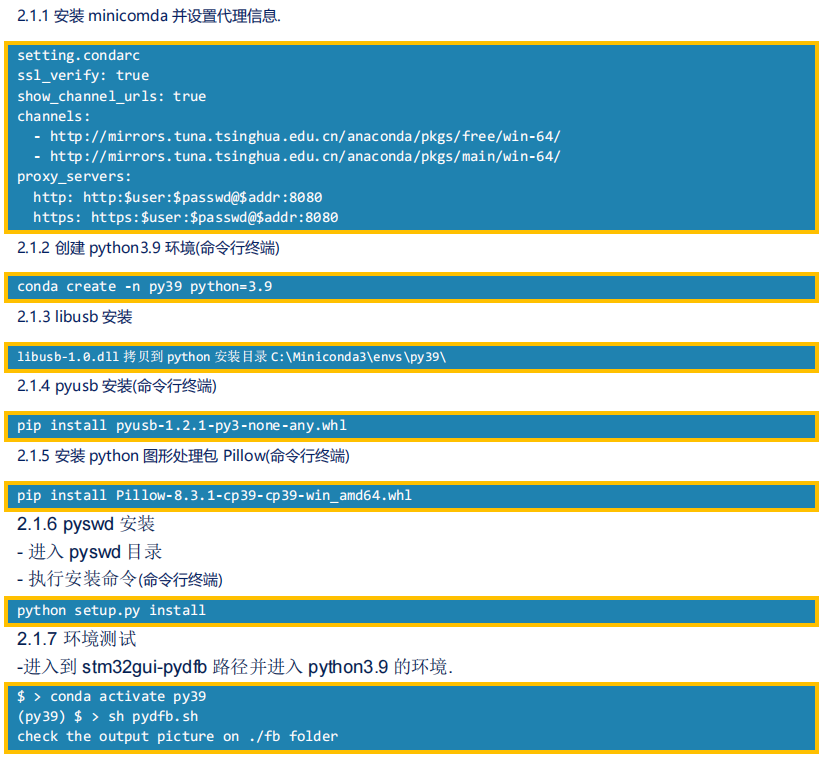

本文檔詳細介紹了意法半導體開發的首款指令緩存(ICACHE)和數據緩存(DCACHE)的基本特性,并在文中提供示例介紹其性能,為大家帶來關于這款指令的全面解讀。由于文章篇幅有限僅展示部分,完整內容請點擊“閱讀原文”下載原文檔。

審核編輯:湯梓紅

-

微控制器

+關注

關注

48文章

7627瀏覽量

151769 -

mcu

+關注

關注

146文章

17263瀏覽量

351986 -

ARM

+關注

關注

134文章

9143瀏覽量

368322 -

存儲器

+關注

關注

38文章

7522瀏覽量

164102 -

Cortex

+關注

關注

2文章

203瀏覽量

46537

原文標題:使用 STM32 緩存來優化性能與功率效率

文章出處:【微信號:mcugeek,微信公眾號:MCU開發加油站】歡迎添加關注!文章轉載請注明出處。

發布評論請先 登錄

相關推薦

智能電機控制優化實時性能與效率設計介紹

Linux和Android系統故障和優化性能的方法和流程探討

實時控制系統需要不斷優化性能

使用STM32緩存來優化性能與功率效率

設計出優化性能的實時控制系統關鍵

UWB帶通濾波器優化性能資料下載

使用STM32緩存來優化性能與功率效率

使用STM32緩存來優化性能與功率效率

評論