》nameWhenByFile

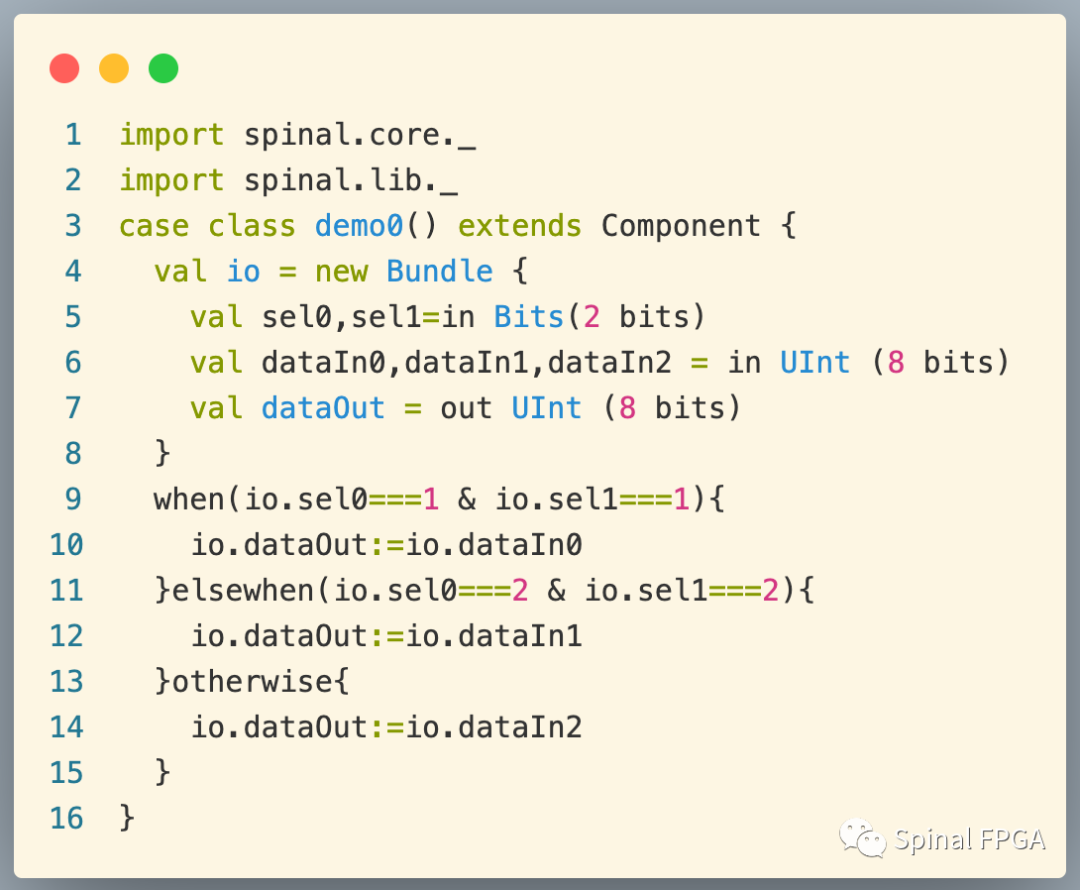

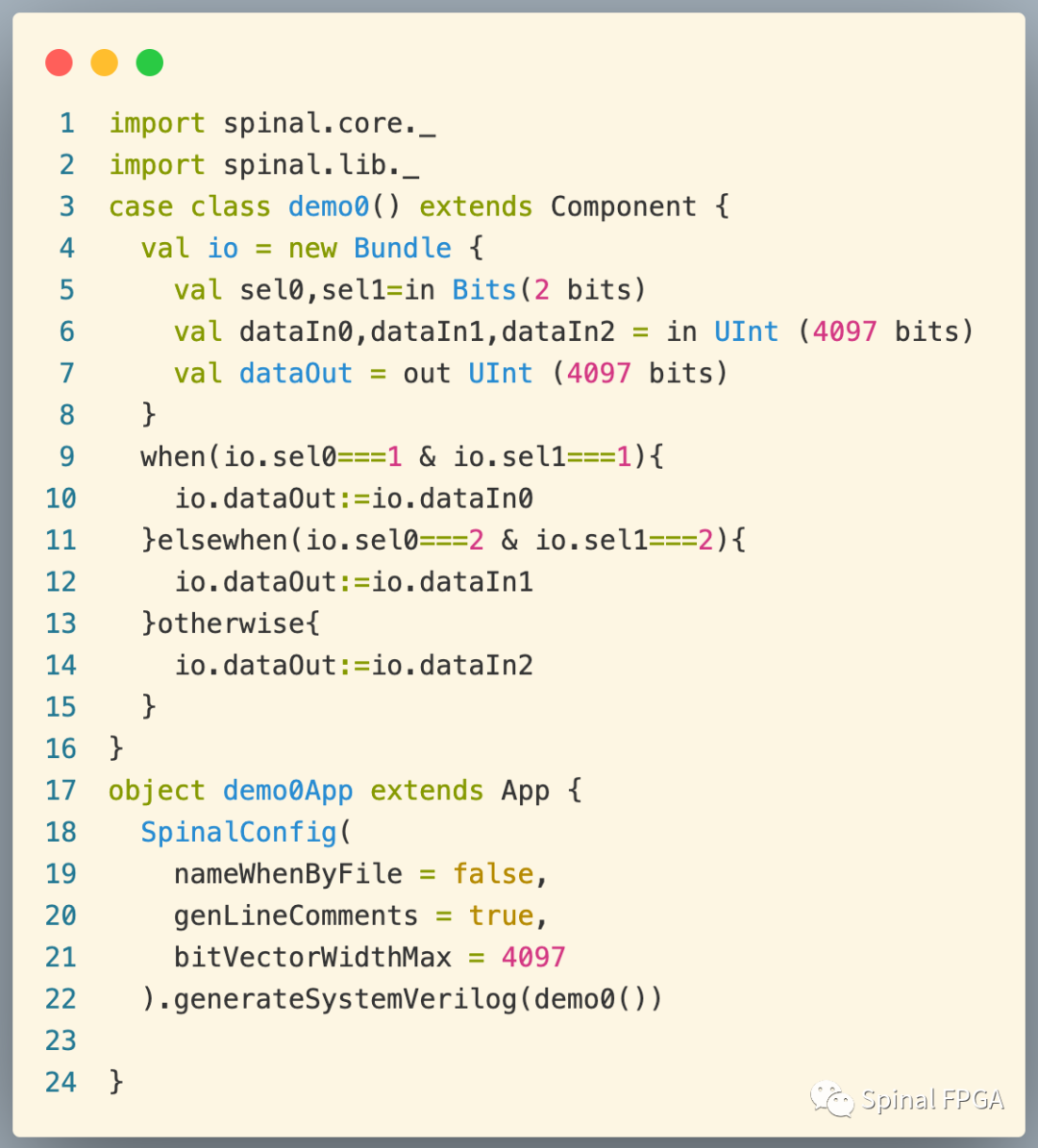

測試代碼如下:

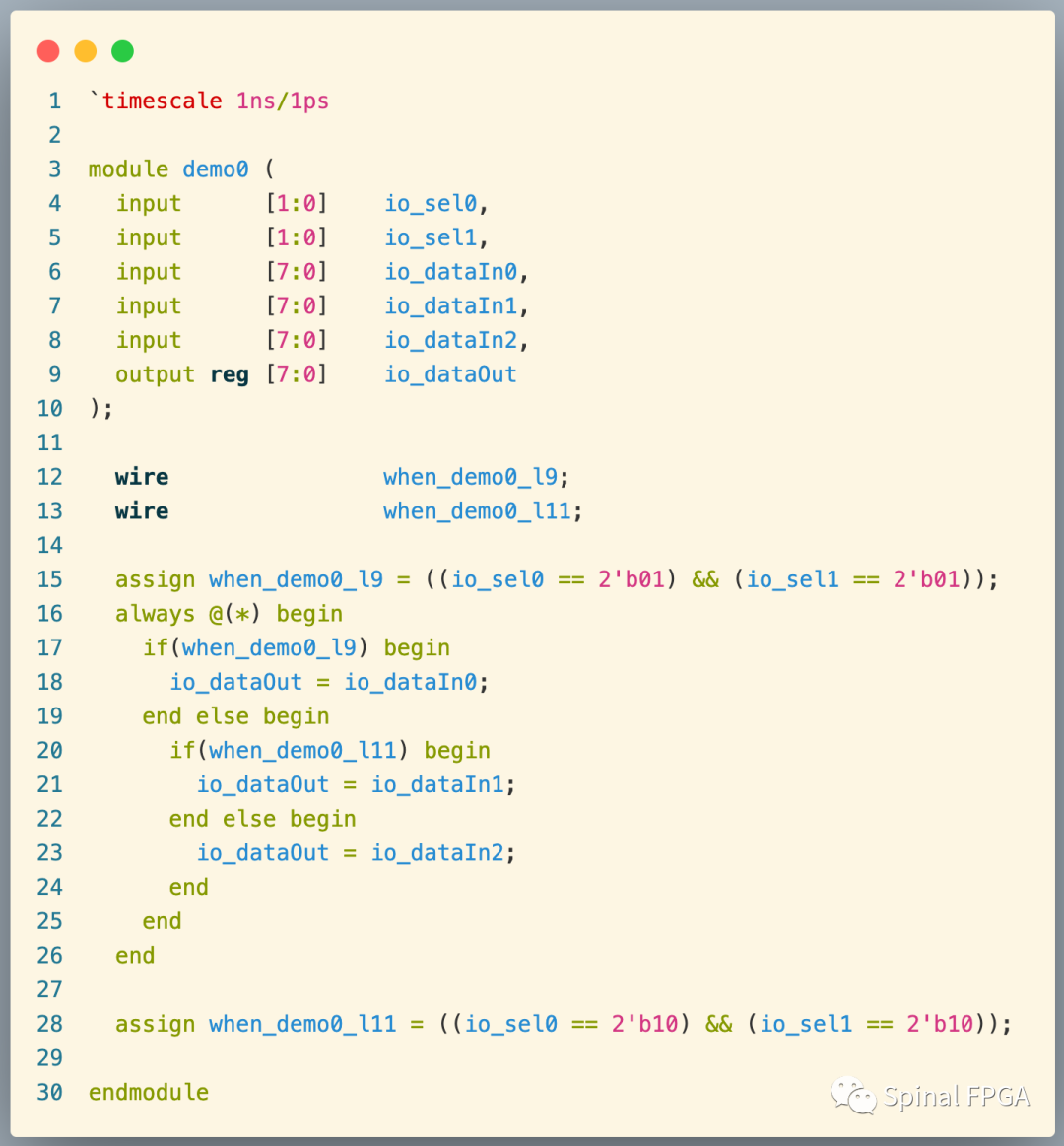

當(dāng)我們采用SpinalSystemVerilog(demo0())的方式生成RTL代碼時其生成的代碼風(fēng)格如下:

在SpinalHDL中對于when的使用,when中所包含的條件往往會生成以一個when+fileName+行號的變量來替代,看起來無非代碼多了幾行,并不影響功能。

因?yàn)橛行刑柕囊耄覀円坏pinalHDL代碼中這部分代碼哪怕是添加了幾行注釋也會引起生成代碼的部分修改,雖然不影響功能,但對于那些喜歡看RTL代碼的人就顯得略顯得不爽了。

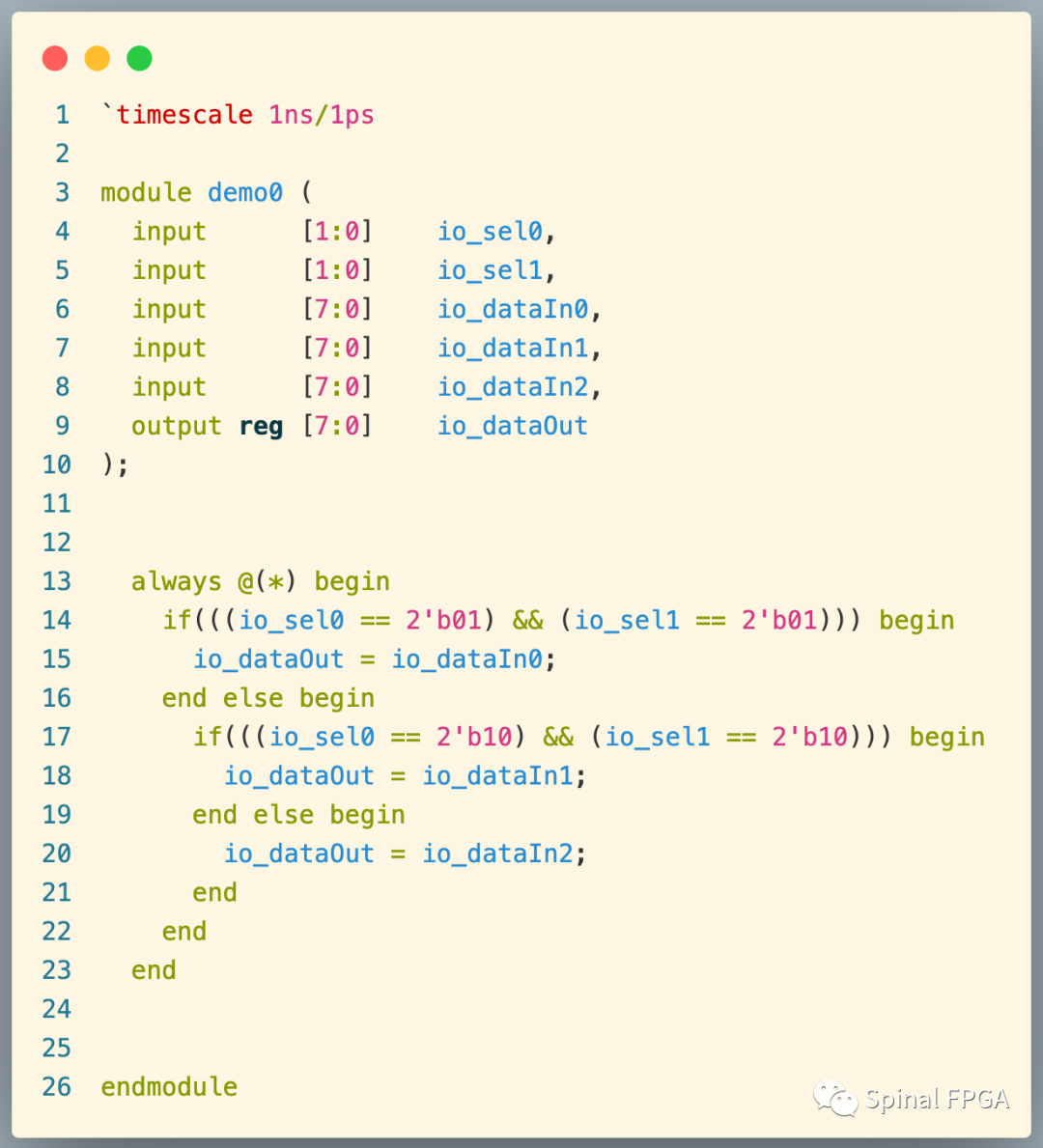

對于when的使用,可以在生成RTL代碼時采用下面的形式來生成:

SpinalConfig( nameWhenByFile=false ).generateSystemVerilog(demo0())

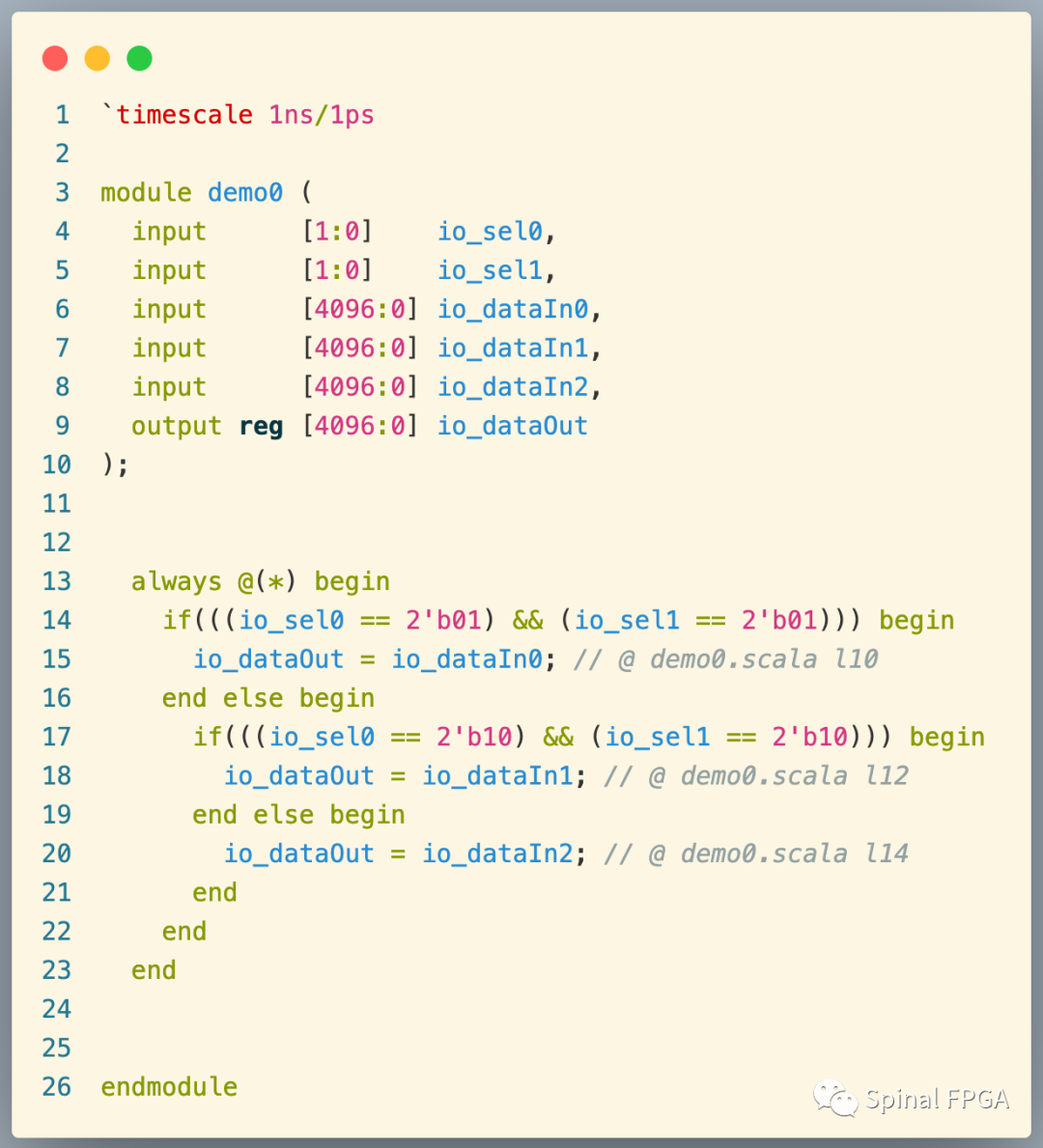

生成代碼如下:

如此生成的代碼不會再對when語句聲明單獨(dú)的變量,代碼看起來和那些采用Verilog寫代碼的人毫無差異吧~

這對于生層的RTL盡可能減少非必要的信號名稱變化。

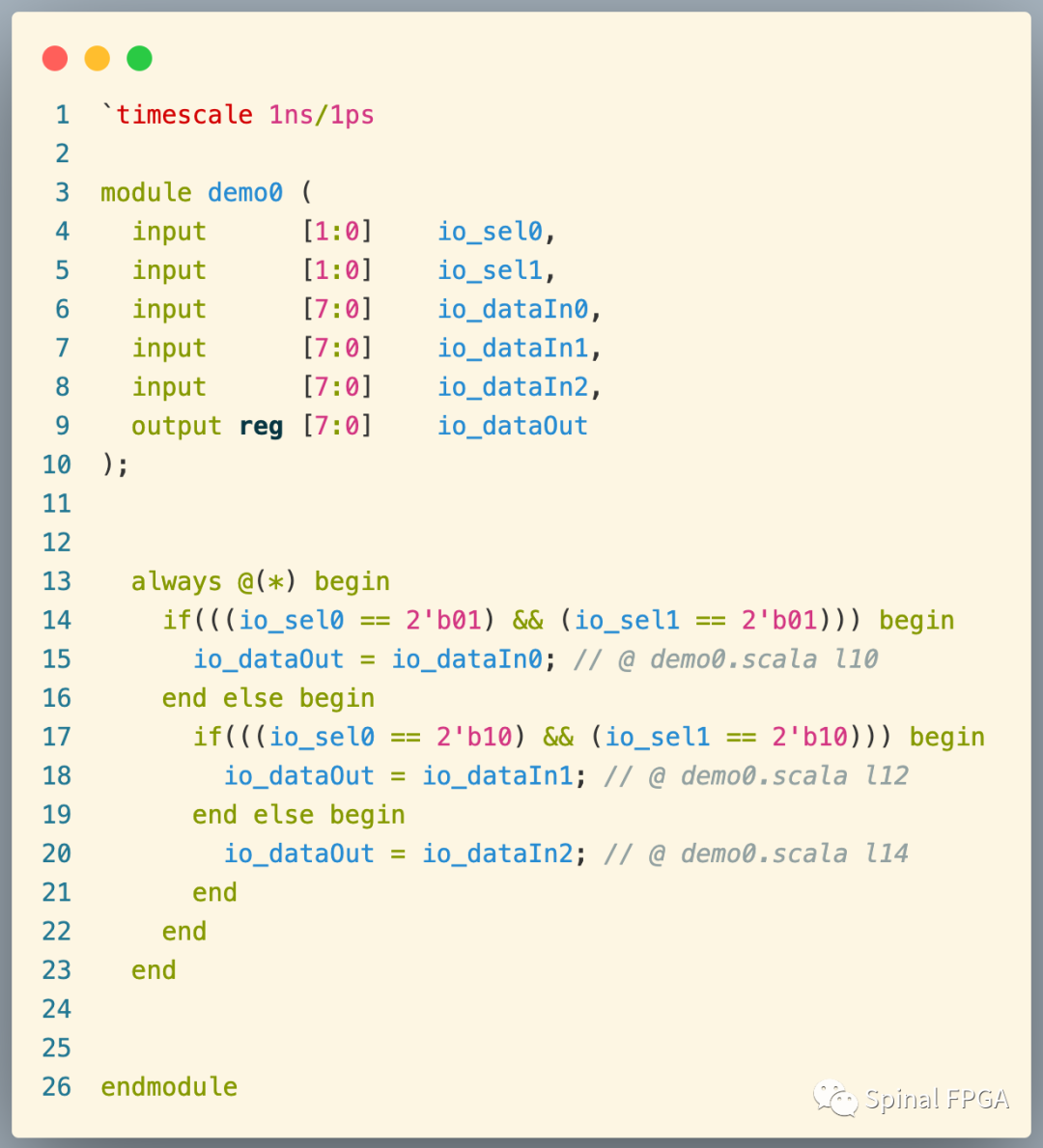

》genLineComments

更近一步,對于代碼生成時采用下面的形式生成:

SpinalConfig(

nameWhenByFile = false,

genLineComments = true

).generateSystemVerilog(demo0())

此時生成的代碼風(fēng)格如下:

當(dāng)genLineComments聲明為true時,在生成RTL代碼中會標(biāo)注映射對應(yīng)的SpinalHDL代碼行號,這對于初學(xué)者在對比生成的RTL代碼學(xué)習(xí)SpinalHDL還是非常的有幫助~

》bitVectorWidthMax

SpinalHDL中對于信號位寬默認(rèn)是最大不超過4096(Intel DDR校準(zhǔn)控制IP里面就有信號位寬就是4096 bit位寬),當(dāng)設(shè)計里定義了信號 位寬超過4096,則會在生成RTL代碼時報錯,可通過SpianlConfig中的bitVectorWidthMax對最大位寬進(jìn)行修改:

審核編輯:劉清

-

DDR

+關(guān)注

關(guān)注

11文章

712瀏覽量

65420 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110190 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59875

原文標(biāo)題:SpinalConfig Tips——讓代碼優(yōu)雅點(diǎn)兒

文章出處:【微信號:Spinal FPGA,微信公眾號:Spinal FPGA】歡迎添加關(guān)注!文章轉(zhuǎn)載請注明出處。

發(fā)布評論請先 登錄

相關(guān)推薦

在SpinalHDL中如何快速地實(shí)現(xiàn)總線連接

安規(guī)三項(xiàng)

關(guān)于SpinalHDL中的驗(yàn)證覆蓋率收集簡單說明

在SpinalHDL中關(guān)于casez的使用

在SpinalHDL中的代碼組織結(jié)構(gòu)如何實(shí)現(xiàn)Component參數(shù)化設(shè)計呢

請問SpinalHDL中的Area到底是什么意思

如何在SpinalHDL里啟動一個仿真

三項(xiàng)閃聯(lián)國際標(biāo)準(zhǔn)文本明年2月公布

iOS 14和tvOS 14系統(tǒng)更新,HomeKit迎來三項(xiàng)重要功能

在SpinalHDL中的對應(yīng)關(guān)系及聲明形式

SpinalHDL中Bundle數(shù)據(jù)類型的轉(zhuǎn)換

國際認(rèn)證三項(xiàng)電池CTL決議最新動態(tài)

不同型號的三項(xiàng)電容可以串聯(lián)嗎?

分享下SpinalHDL中SpinalConfig中的三項(xiàng)參數(shù)

分享下SpinalHDL中SpinalConfig中的三項(xiàng)參數(shù)

評論