4

旁路電路注入故障

旁路電路技術的實現原理和掃描鏈技術類似,在原有的電路結構上添加附加電路來使電路能夠模擬單粒子翻轉效應 ^[25-26]^ 。以寄存器為例,在正常狀態下寄存器保持其原本的功能,在故障注入模式下通過外部控制信號驅動附加電路從旁路修改寄存器的數值。

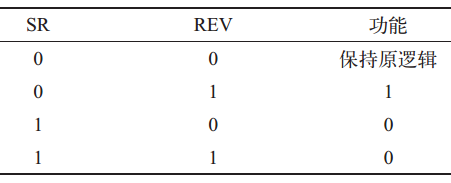

文獻[27]介紹了一種旁路電路注入故障的電路結構,基于Xilinx Virtex-5的FPGA實現,帶旁路電路的寄存器結構如圖4所示。該電路在原本的寄存器結構上添加了3個查找表(Look-Up-Table, LUT)和額外的輸入信號,修改寄存器的復位信號SR(Set/Reset)和翻轉信號REV(REVerse)的輸入值來實現故障注入功能。默認模式下寄存器對應的真值表如表1所示。

表1 默認模式寄存器真值表

圖4中,輸入信號inj為故障注入使能信號,Original_CE、Original_R和Original_S分別連接寄存器原始的時鐘使能CE、復位Reset和置位Set信號。如果inj為0,該寄存器等同于普通的寄存器,而inj為1時,3個查找表就會根據寄存器的輸出值Q生成相反的值并寫入寄存器。

圖4 帶旁路電路的寄存器結構

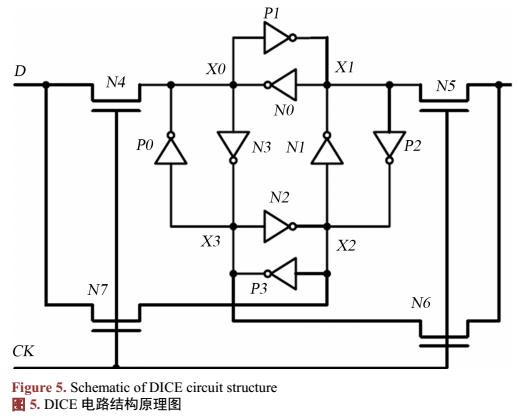

文獻[28]的電路修改方式更加簡單,僅在原始寄存器結構上增加了一個異或門。替換前后的寄存器結構如圖5所示。當故障注入信號Inject信號為高電平時,寄存器的輸入端數據會發生翻轉,而Inject信號為低電平時,寄存器的輸入端數據保持原始狀態。和文獻[27]相比,區別在于故障注入時,文獻[28]的寄存器數值一定會進行翻轉,而文獻[27]則可以模擬更加復雜的情況,因為單粒子翻轉效應在作用于寄存器時有固定0、固定1和翻轉3種情況,并不一定會導致翻轉。但是,文獻[28]的電路結構的資源開銷比文獻[27]小得多,具備一定的優勢。

文獻[29-30]介紹了另一種旁路電路的實現方式,通過對電路綜合后的網表進行修改,將原有的器件庫全部替換成為附加故障注入功能的器件庫,其中包括寄存器、隨機存取存儲器(Random Access Memory, RAM)、查找表、邏輯門以及乘法器等,更新后的網表的時序邏輯部分不會受到影響,只是添加了故障注入相關的組合邏輯模塊。但其實現過程較為復雜,器件庫的修改需要耗費大量的時間進行功能和時序驗證。同時器件庫和FPGA型號是緊密聯系的,更替FPGA芯片將可能導致器件庫無法使用,因此遷移性較差。

和掃描鏈技術相比,旁路電路技術省去了串行移位故障數據的過程,故障直接注入到待評估寄存器中,從而提高了故障注入速度。旁路電路同樣可適用于任意規模電路,而且可以針對電路中的其他存儲元件(LUT、RAM等)設計故障電路,適用范圍更廣,故障敏感節點的定位精度也高于掃描鏈。其主要缺陷會帶來額外的資源開銷,此外還可能增加關鍵路徑的延時,對時序造成負面影響。

除了故障注入速度的差異,文獻[31]同樣提到了數據交互過程造成的龐大時間開銷,文中基于RS232傳輸故障激勵數據,傳輸速度配置為115 kbit/s,單次數據傳輸過程需花費14 ms,而故障注入執行過程僅占2 ms,因此導致故障注入速度偏慢。

5

故障注入方式對比和展望

5.1 故障注入方式對比

FPGA模擬技術主要用于評估超大規模集成電路設計對單粒子翻轉效應的敏感性。因此本文從評估速度、電路開銷和敏感點定位精度3個方面進行對比,故障注入方式具體性能對比如表2所示。

表2 故障注入方式性能對比

FPGA模擬技術中的重配置技術存在速度瓶頸,雖然通過部分重配置可以顯著提高效率,但是與修改電路結構的方式相比較,重配置技術故障注入速度稍慢。若基于掃描鏈去實現,其串行移位的故障注入模式會帶來一定的時間開銷。而旁路電路方式可使得電路即時響應故障,不會產生額外的時間開銷。

在電路開銷方面,由于重配置所需要的硬件電路都固化在FPGA芯片內部,所以額外需要的電路開銷是最小的。考慮到掃描鏈可以復用可測性設計的掃描鏈結構,所以電路開銷稍低。電路開銷最大的是旁路電路,因為每個寄存器外圍都需要配備譯碼選通電路和故障注入電路,但是隨著FPGA的技術開發,單LUT電路能夠實現的功能愈加復雜,其占用的電路開銷比例也可以不斷下降。

在敏感點定位精度上,由于配置文件格式不公開,多數研究采取隨機注入或是遍歷式注入,但是注入故障后難以在最初的原始設計文件中定位故障節點,這對評估工作非常不友好,難以指導后續的改進工作。由于掃描鏈是串行結構,定位需要依賴輸入激勵和輸出響應的先后順序,這會和評估速度形成互相制約的關系。因為如果注入速度過快,對準確采樣高速輸出響應的工作會提出很高的要求。旁路電路由于具有專用接口電路,因此即使在高速注入情況下,也能準確定位注入故障的位置。

5.2 故障注入方式展望

重配置、掃描鏈和旁路電路3種方法的實現結構不一樣,優化的思路也會有所不同。

重配置在評估速度上表現不佳,主要是由于上位機和FPGA之間頻繁通信造成較大的時間開銷。如何讓測試激勵以更快的速度配置到FPGA中是未來的提高方向。采用DDR緩存測試激勵,以及采用類似Xilinx ZYNQ架構的芯片作為測試平臺,都是可行的方式。在確定注入故障定位上,可行的思路有對比配置文件格式和配置后器件位置,對配置文件進行破解。但是需要按照電路版圖結構從大到小逐次解析,并區分LUT、RAM等多種存儲元件,工作量比較龐大 ^[32]^ ,所以重配置技術的改善工作更適合FPGA設計廠商實施。

在有可測性設計的電路中,掃描鏈技術是非常合理的選擇。但是,為了提高測試效率,如何壓縮測試激勵的數量,以及測試響應的高效對比,是掃描鏈技術未來的發展方向。此外,掃描鏈的電路結構也可以進行一定的優化,主要在提高運行速度和降低開銷兩方面進行針對性的改進,擴充可測性設計的研究范疇。

旁路電路的改進方向是進一步壓低電路開銷。這方面可以考慮相鄰電路之間復用故障注入電路,從而降低電路開銷。需要注意的是,旁路電路往往和測試平臺的器件庫密切相關,所以未來在設計電路時可以將電路修改方式設計成通用腳本,通過算法和器件庫建立聯系,從而增加其適用范圍。

此外,由于3種方案的優勢各不相同,未來的評估平臺也可以結合多種方式。比如可利用旁路電路故障注入的準確性彌補重配置技術的精度缺陷,提高注入速度,同時也可以通過重配置技術避免旁路電路相關故障注入模塊的資源開銷。這樣不僅平臺的評估效率有所提高,評估電路的適用范圍也變得更加廣泛。

6

** 總 結 **

隨著集成電路工藝邁入納米時代,現有FPGA模擬技術面臨的最大挑戰是待評估電路規模過于龐大導致評估時間大幅增加。如何在設計資源允許的情況下,盡可能提高模擬單粒子翻轉效應的故障注入速度,并盡可能確定待評估電路中SEU敏感區位置,是FPGA模擬單粒子翻轉效應的重要研究方向。從上述內容可以看出,重配置、掃描鏈和旁路電路技術假以時日,均能在評估速度、電路開銷和定位精度等性能指標上取得進展,使之更適合用于評估超大規模集成電路設計對單粒子翻轉效應的敏感性。

-

FPGA

+關注

關注

1629文章

21759瀏覽量

604279 -

電路

+關注

關注

172文章

5936瀏覽量

172478 -

寄存器

+關注

關注

31文章

5357瀏覽量

120658

發布評論請先 登錄

相關推薦

單粒子翻轉引起SRAM型FPGA的故障機理闡述

單粒子翻轉效應的FPGA模擬技術 (下)

單粒子翻轉效應的FPGA模擬技術 (下)

評論