數(shù)字硬件建模SystemVerilog(四)-綜合

綜合編譯器將實(shí)現(xiàn)細(xì)節(jié)添加到抽象RTL模型,合成編譯器:

- 將RTL功能轉(zhuǎn)換為等效功能的通用邏輯門(mén)。

- 將通用門(mén)映射到特定的ASIC或FPGA目標(biāo)。

- 執(zhí)行邏輯優(yōu)化以滿足時(shí)鐘速度要求。

- 執(zhí)行邏輯優(yōu)化以滿足面積和功率要求,

- 執(zhí)行邏輯優(yōu)化以滿足建立和保持時(shí)間。

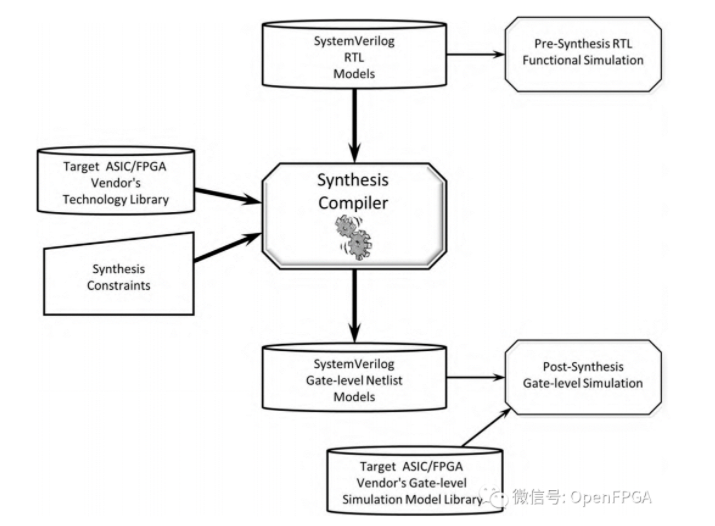

圖1-10說(shuō)明了使用SystemVerilog進(jìn)行數(shù)字綜合的一般流程,

圖1-10:SystemVerilog綜合工具流程

綜合編譯器需要三種主要類型的輸入信息:

- 系統(tǒng)Verilog RTL模型-這些模型由設(shè)計(jì)工程師編寫(xiě),代表需要在ASIC或FPGA中實(shí)現(xiàn)的功能行為

- 目標(biāo)ASIC或FPGA的工藝庫(kù)-該庫(kù)由ASIC或FPGA供應(yīng)商提供,包含可用于實(shí)現(xiàn)所需功能的標(biāo)準(zhǔn)單元(用于ASIC)或門(mén)陣列塊(用于FPGA)的定義

- 綜合約束定義-這些約束由設(shè)計(jì)工程師定義,并提供RTL代碼中不可用的綜合編譯器信息,例如需要在ASIC或FPGA中實(shí)現(xiàn)的所需時(shí)鐘速度、面積和功率目標(biāo)。

出于前端設(shè)計(jì)和驗(yàn)證目的,綜合的主要輸出是門(mén)級(jí)網(wǎng)表。網(wǎng)絡(luò)列表是組件和將這些組件連接在一起的導(dǎo)線(稱為網(wǎng)絡(luò))的列表。網(wǎng)絡(luò)列表中引用的組件將是用于實(shí)現(xiàn)所需功能的ASIC標(biāo)準(zhǔn)單元或FPGA門(mén)陣列塊。此網(wǎng)絡(luò)列表可以有多種格式,包括EDIF、VHDL、Verilog2001或SystemVerilog。本系列文章僅使用SystemVerilog輸出。

為了仿真SystemVerilog網(wǎng)絡(luò)列表,需要每個(gè)組件的仿真模型。目標(biāo)ASIC或FPGA供應(yīng)商將提供用SystemVerilog編寫(xiě)的仿真庫(kù)。通常,這些庫(kù)只使用SystemVerilog的Verilog-2001子集。這些組件在門(mén)級(jí)建模,具有詳細(xì)的傳播延遲。這些模型與設(shè)計(jì)工程師編寫(xiě)的抽象RTL模型不同。

SV綜合編譯器

有幾個(gè)SystemVerilog綜合編譯器支持SystemVerilog語(yǔ)言。Cadence、Mentor Graphics和Synopsys等電子設(shè)計(jì)自動(dòng)化(EDA)公司銷售的商用綜合編譯器。一些FPGA供應(yīng)商,如Xilinx和Intel(前身為Altera)提供了專用于該供應(yīng)商技術(shù)的專用綜合編譯器。

SystemVerilog是一種兩用語(yǔ)言。一個(gè)目的是對(duì)數(shù)字硬件的行為進(jìn)行建模。第二個(gè)目的是編寫(xiě)驗(yàn)證程序來(lái)測(cè)試硬件模型。這兩個(gè)目的有非常不同的語(yǔ)言要求。許多通用編程結(jié)構(gòu)對(duì)于這兩個(gè)目的都很有用,例如,if-else決策或for循環(huán)。其他語(yǔ)言特性只能用于驗(yàn)證,例如約束隨機(jī)測(cè)試(random test)生成。這些驗(yàn)證結(jié)構(gòu)并不表示硬件功能,綜合編譯器也不支持這些驗(yàn)證結(jié)構(gòu)。

IEEE尚未確定SystemVerilog的正式可綜合子集。標(biāo)準(zhǔn)的這一缺陷導(dǎo)致了每個(gè)綜合編譯器對(duì)可綜合SystemVerilog語(yǔ)言子集的支持存在重大偏差。此外,由特定綜合編譯器標(biāo)識(shí)的子集可以(幾乎肯定會(huì))將綜合產(chǎn)品的一個(gè)版本更改為該產(chǎn)品的下一個(gè)版本。

綜合編譯Synthesis Compilation

綜合編譯器的目標(biāo)與仿真編譯器不同。這兩種類型的編譯器都需要檢查SystemVerilog RTL源代碼的語(yǔ)法正確性,但這就是相似性的終點(diǎn)。仿真是一個(gè)動(dòng)態(tài)過(guò)程,涉及仿真時(shí)間、事件調(diào)度、應(yīng)用刺激和驗(yàn)證輸出。綜合是一個(gè)靜態(tài)轉(zhuǎn)換和優(yōu)化過(guò)程,不涉及任何這些仿真目標(biāo)。綜合編譯器需要確保代碼滿足必要的語(yǔ)言限制,以便將RTL功能轉(zhuǎn)換為ASIC和FPGA實(shí)現(xiàn)中支持的邏輯門(mén)類型。這些限制包括檢查RTL代碼是否具有明確定義的時(shí)鐘周期活動(dòng)、單驅(qū)動(dòng)程序邏輯等,綜合編譯器只需要編譯RTL模型。綜合不需要編譯帶有激勵(lì)生成和輸出驗(yàn)證的測(cè)試臺(tái)代碼。

單文件和多文件編譯

大型設(shè)計(jì)被劃分為許多子塊。通常,每個(gè)子塊將存儲(chǔ)在單獨(dú)的文件中,為了仿真分區(qū)設(shè)計(jì),仿真要求所有這些子塊都被編譯并連接在一起。另一方面,綜合通常可以分別編譯和處理每個(gè)子塊。綜合優(yōu)化和技術(shù)映射是計(jì)算密集型過(guò)程。將太多的子塊合成在一起可能會(huì)導(dǎo)致結(jié)果質(zhì)量(QOR)不理想。

在綜合設(shè)計(jì)的子塊時(shí),有兩個(gè)重要的考慮因素。首先,來(lái)自定義包的子塊中使用的任何定義都要求該包與子塊一起編譯,并以適當(dāng)?shù)姆绞桨凑枕樞蚓幾g,如果多個(gè)子塊使用同一個(gè)包,則需要使用與其他子塊分開(kāi)編譯的每個(gè)子塊重新編譯包,第二個(gè)考慮因素是,在每個(gè)單獨(dú)的編譯中都不會(huì)看到任何全局聲明,包括“定義編譯器指令”。

約束條件

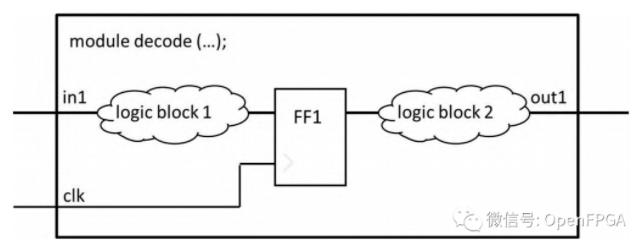

圖1-10顯示了綜合的三個(gè)主要輸入之一是約束。約束用于定義綜合所需的信息,但這些信息既不在RTL模型中,也不在ASIC/FPGA供應(yīng)商的技術(shù)庫(kù)中。圖1-11說(shuō)明了一個(gè)簡(jiǎn)單的電路,其中綜合所需的一些信息必須由設(shè)計(jì)工程師指定。

圖1-11:需要綜合約束的簡(jiǎn)單電路圖

將此功能數(shù)據(jù)流綜合成邏輯門(mén)的過(guò)程包括:

- 將綜合的觸發(fā)器FF1映射到目標(biāo)ASIC或FPGA中的適當(dāng)觸發(fā)器。

- 將logic_block_1中描述的功能映射到目標(biāo)ASIC或FPGA的標(biāo)準(zhǔn)單元或邏輯塊。

- 優(yōu)化logic_block_1的布局布線,以滿足FF1建立時(shí)間和保持時(shí)間要求。

- 將logic_block_2中描述的功能映射到目標(biāo)ASIC或FPGA的標(biāo)準(zhǔn)單元或邏輯塊。

- 優(yōu)化logic_block_2的布局布線,以滿足建立時(shí)間和保持時(shí)間要求。

為了在目標(biāo)ASIC或FPGA中實(shí)現(xiàn)圖1-11所示的簡(jiǎn)單電路,綜合編譯器必須知道:

- 用于實(shí)現(xiàn)logic_block_1和logic_block_2的標(biāo)準(zhǔn)單元或邏輯塊的傳播延遲、面積和功率要求。

- FF1建立時(shí)間和保持時(shí)間。

- clk的周期或頻率,如100Mhz。

- in1相對(duì)于CLK邊沿的到達(dá)時(shí)間。

- in1外部電源的驅(qū)動(dòng)能力

- 相對(duì)于clk邊沿的out1的到達(dá)時(shí)間。

- out1的輸出驅(qū)動(dòng)要求。

此信息不在RTL模型中。此列表中前兩項(xiàng)的規(guī)范,傳播延遲和建立/保持時(shí)間,將來(lái)自ASIC或FPGA供應(yīng)商提供的技術(shù)庫(kù),其余細(xì)節(jié)必須由綜合設(shè)計(jì)的設(shè)計(jì)工程師指定。這些規(guī)范被稱為綜合約束,更大、更復(fù)雜的設(shè)計(jì)將需要更多的綜合約束,后續(xù)的RTL編碼示例將在適當(dāng)?shù)那闆r下討論適用的綜合約束。還提供了簡(jiǎn)化必須指定的約束的指南。

指定綜合約束的方式因不同的合成編譯器而異。推薦讀者閱讀《綜合和時(shí)序分析的約束設(shè)計(jì)Constmining Designs for Synthesis and Timing Analysis》文檔了解此信息。

-

FPGA

+關(guān)注

關(guān)注

1630文章

21781瀏覽量

604913 -

asic

+關(guān)注

關(guān)注

34文章

1205瀏覽量

120624 -

Verilog

+關(guān)注

關(guān)注

28文章

1351瀏覽量

110216 -

RTL

+關(guān)注

關(guān)注

1文章

385瀏覽量

59892

發(fā)布評(píng)論請(qǐng)先 登錄

相關(guān)推薦

FPGA時(shí)序約束之衍生時(shí)鐘約束和時(shí)鐘分組約束

ISE 生成的sdf文件和在綜合前的約束有關(guān)系么?

介紹FPGA的綜合(轉(zhuǎn))

FPGA的約束設(shè)計(jì)和時(shí)序分析

FPGA上的引腳和區(qū)域約束語(yǔ)法介紹

FPGA設(shè)計(jì)約束技巧之XDC約束之I/O篇(下)

基于FPGA的綜合技術(shù)分析(RTL分析、SDC約束和綜合向?qū)В?/a>

FPGA約束的詳細(xì)介紹

如何輕松管理PCB設(shè)計(jì)規(guī)則和約束

如何輕松地管理您的設(shè)計(jì)規(guī)則和約束

淺談PCB設(shè)計(jì)系統(tǒng)中的設(shè)計(jì)規(guī)則和約束

FPGA的綜合和約束的關(guān)系

Xilinx FPGA時(shí)序約束設(shè)計(jì)和分析

Xilinx FPGA的約束設(shè)置基礎(chǔ)

什么是FPGA的綜合和約束的關(guān)系?

什么是FPGA的綜合和約束的關(guān)系?

評(píng)論